# FR400 Series Instruction Set Manual

Version 2.2 Jan, 2004

# **FUJITSU LIMITED**

- The contents of this document are subject to change without notice.

Customers are advised to consult with FUJITSU sales representatives before ordering.

- 2) The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of FUJITSU semiconductor device; FUJITSU does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information. FUJITSU assumes no liability for any damages whatsoever arising out of the use of the information.

- 3) Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU or any third party or does FUJITSU warrant non-infringement of any third-party's intellectual property right or other right by using such information. FUJITSU assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

- 4) The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite). Please note that FUJITSU will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

- 5) Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

- 6) If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.

© 2003 FUJITSU LIMITED All Rights Reserved.

# Contents

| FR40             | 00 Series                                                                            | I   |

|------------------|--------------------------------------------------------------------------------------|-----|

| <b>T</b> 4       |                                                                                      |     |

| Instr            | uction Set Manual                                                                    | I   |

| 1. Instruc       | ction Set Reference                                                                  | . 1 |

| 1.1. Exp         | planation of each term                                                               | 1   |

| -                | eger Instructions                                                                    |     |

| 1.2.1.           | Add / Subtract (ADDSS and SUBSS are available for MB93405/MB93451.)                  |     |

| 1.2.1.           | Multiply                                                                             |     |

| 1.2.3.           | Multiply and Add / Subtract (These instructions are available for MB93405/MB93451.). |     |

| 1.2.4.           | Multiply to IACC (This instruction is available for MB93405/MB93451.)                |     |

| 1.2.5.           | Divide                                                                               |     |

| 1.2.6.           | Logical Operations                                                                   |     |

| 1.2.7.           | Shift (SLASS instruction is available for MB93405/MB93451.)                          |     |

| 1.2.8.<br>1.2.9. | Byte Compare Instruction                                                             | 16  |

|                  |                                                                                      |     |

|                  | nd/Store Instructions                                                                |     |

| 1.3.1.           | Load GR                                                                              |     |

| 1.3.2.<br>1.3.3. | Load FRStore GR                                                                      |     |

| 1.3.3.<br>1.3.4. | Store FR.                                                                            |     |

|                  | a transfer Instructions                                                              |     |

|                  |                                                                                      |     |

| 1.4.1.<br>1.4.2. | Swap                                                                                 |     |

|                  |                                                                                      |     |

|                  | ntrol transfer Instructions                                                          |     |

| 1.5.1.           | Integer Conditional Branch                                                           |     |

| 1.5.2.<br>1.5.3. | Floating-point / media Conditional Branch  LCR Conditional Branch to LR              |     |

| 1.5.3.<br>1.5.4. | Integer conditional Branches to LR                                                   |     |

| 1.5.4.           | Floating-point/Media Branches to LR                                                  |     |

| 1.5.6.           | Jump and Link                                                                        |     |

| 1.5.7.           | Call                                                                                 |     |

| 1.5.8.           | Return from Trap                                                                     | 45  |

| 1.5.9.           | Integer Conditional Trap                                                             | 46  |

| 1.5.10.          | Floating-point / media Conditional Trap                                              |     |

| 1.5.11.          | Break                                                                                |     |

| 1.5.12.          | Media Trap                                                                           |     |

| 1.6. Cor         | nstant Setting Instructions                                                          | 54  |

| 1.6.1.           | Set                                                                                  | 54  |

| 1.7. Sca         | n instruction                                                                        | 56  |

| 1.7.1.           | Scan                                                                                 | 56  |

| 1.8. Cor         | ndition Code Operating Instructions                                                  | 58  |

| 1.8.1.           | Check for Integer Condition Code.                                                    |     |

| 1.8.2.           | Check for Floating-point/Media Condition Code                                        |     |

| 1.8.3.  | Condition Code Logical Operations                      | 62  |

|---------|--------------------------------------------------------|-----|

| 1.9. S  | pecial Operation Instructions                          | 66  |

| 1.9.1.  | Instruction Cache Invalidate                           | 66  |

| 1.9.2.  | Data Cache Invalidate                                  | 67  |

| 1.9.3.  | Data Cache Flush                                       | 68  |

| 1.9.4.  | Instruction Cache Entry Invalidate Instruction         | 69  |

| 1.9.5.  | Data Cache Entry Invalidate Instruction.               | 70  |

| 1.9.6.  | Data Cache Entry Flush Instruction                     | 71  |

| 1.9.7.  | Instruction Cache Pre-Load                             | 72  |

| 1.9.8.  | Data Cache Pre-Load                                    | 73  |

| 1.9.9.  | Instruction Cache UnLock                               | 74  |

| 1.9.10. | Data Cache UnLock                                      | 75  |

| 1.9.11. | Barrier                                                | 76  |

| 1.9.12. | Memory Barrier                                         | 77  |

| 1.9.13. |                                                        |     |

| 1.9.14. |                                                        |     |

| 1.9.15. | TLB Probe (This instruction is available for MB93451.) | 82  |

| 1.10. N | Media Instructions                                     | 85  |

| 1.10.1. | Media Nop Instruction (M -Type Instruction)            | 85  |

| 1.10.2. |                                                        |     |

| 1.10.3. | Rotate                                                 | 87  |

| 1.10.4. | Word Cut                                               | 88  |

| 1.10.5. | Average (Halfword Dual)                                | 90  |

| 1.10.6. | Shift (Halfword Dual)                                  | 91  |

| 1.10.7. |                                                        |     |

| 1.10.8. | Saturate (Halfword Dual)                               | 93  |

| 1.10.9. | T                                                      |     |

| 1.10.10 | · · · · · · · · · · · · · · · · · · ·                  |     |

| 1.10.1  | I (                                                    |     |

| 1.10.12 |                                                        |     |

| 1.10.1. | - F J ( )                                              |     |

| 1.10.14 | · · · · · · · · · · · · · · · ·                        |     |

| 1.10.13 | · · · · · · · · · · · · · · · · · · ·                  |     |

| 1.10.10 | · · · · · · · · · · · · · · · · · · ·                  |     |

| 1.10.1  |                                                        |     |

| 1.10.13 | - F J (                                                |     |

| 1.10.19 |                                                        |     |

| 1.10.20 | T J                                                    |     |

| 1.10.2  |                                                        |     |

| 1.10.22 | 119                                                    |     |

| 1.10.23 |                                                        |     |

| 1.10.24 | 1 1 3 \                                                |     |

| 1.10.23 | 5. Complex Multiply (Halfword Quad)                    | 125 |

| 1.10.20 |                                                        |     |

| 1.10.2  |                                                        |     |

| 1.10.28 |                                                        |     |

| 1.10.29 |                                                        |     |

| 1.10.30 | 1 /                                                    |     |

| 1.10.3  |                                                        |     |

| 1.10.32 |                                                        |     |

| 1.10.33 |                                                        |     |

| 1.10.34 | , ,                                                    |     |

| 1.10.33 | 5. Clear Accumulator                                   | 143 |

| 1.10.36.           | Read/Write Accumulator                                                                                          | 144 |

|--------------------|-----------------------------------------------------------------------------------------------------------------|-----|

| 1.10.37.           | Media Accumulator Addition Instruction                                                                          |     |

| 1.10.38.           | Media Accumulator Subtraction Instruction                                                                       |     |

| 1.10.39.           | Media Dual Accumulator Addition Instruction                                                                     |     |

| 1.10.40.           | Media Dual Accumulator Subtraction Instruction                                                                  |     |

| 1.10.41.           | Media Accumulator Addition and Subtraction Instruction                                                          |     |

| 1.10.42.           | Media Dual Accumulator Addition and Subtraction Instruction                                                     |     |

| 1.10.43.           |                                                                                                                 |     |

|                    | Media Quad Low Clear (Halfword Quad) Instruction (M-Type Instruction. This instruble for MB93451.)              |     |

| 1.10.45.           | Media Quad Scope Limitation (Halfword Quad) Instruction (M-Type Instruction. This on is available for MB93451.) | 3   |

| 1.10.46.           |                                                                                                                 |     |

| available          | e for MB93451.)                                                                                                 |     |

| 1.11. Co           | nditional Integer Instructions                                                                                  | 158 |

| 1.11.1.            | Add / Subtract / Multiply / Divide                                                                              |     |

| 1.11.2.            | Add, Subtract and Multiply with setting ICC / Divide unsigned integer                                           |     |

| 1.11.3.            | Logical Operations                                                                                              |     |

| 1.11.4.            | Logical Operations with setting ICC                                                                             |     |

| 1.11.5.            | Shift                                                                                                           |     |

| 1.11.6.            | Shift with setting ICC                                                                                          | 168 |

| 1.12. Co           | nditional Load/Store Instructions                                                                               | 170 |

| 1.12.1.            | Load GR                                                                                                         | 170 |

| 1.12.2.            | Load FR                                                                                                         |     |

| 1.12.3.            | Store GR                                                                                                        | 174 |

| 1.12.4.            | Store FR                                                                                                        | 176 |

| 1.13. Co           | nditional Data transfer Instructions                                                                            | 178 |

| 1.13.1.            | Swap                                                                                                            | 178 |

| 1.13.2.            | Move                                                                                                            |     |

| 1.14 Co            | nditional Control transfer Instructions.                                                                        | 182 |

| 1.14.1.            | Jump and Link                                                                                                   |     |

|                    | nditional Scan instruction                                                                                      |     |

|                    | Scan                                                                                                            |     |

| 1.15.1.            |                                                                                                                 |     |

|                    | nditional Condition code operating Instructions                                                                 |     |

| 1.16.1.            | Check for Integer Condition code                                                                                |     |

| 1.16.2.            | Check for Floating-point/Media Conditional code                                                                 |     |

| 1.17. Co           | nditional Media Instructions                                                                                    | 189 |

| 1.17.1.            | Logical Operations                                                                                              | 189 |

| 1.17.2.            | Add / Subtract with Saturation (Halfword Dual)                                                                  |     |

| 1.17.3.            | Multiply and Accumulate (Halfword Dual)                                                                         |     |

| 1.17.4.            | Add / Subtract with Saturation (Halfword Quad)                                                                  |     |

| 1.17.5.            | Multiply / Multiply and Accumulate (Halfword Quad)                                                              |     |

| 1.17.6.<br>1.17.7. | Complex Multiply (Halfword Dual)                                                                                |     |

| 1.17.7.            | Expand (Halfword)                                                                                               |     |

|                    | instruction                                                                                                     |     |

|                    |                                                                                                                 |     |

|                    | nstruct ion of VLIW instruction                                                                                 |     |

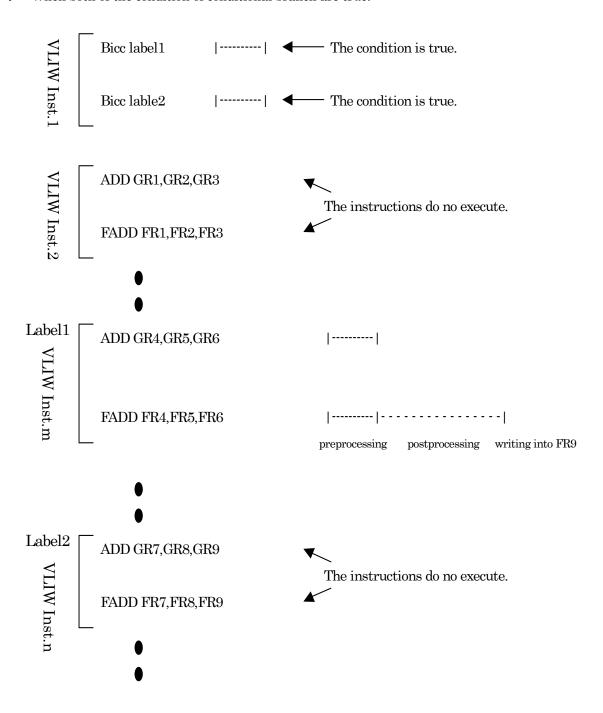

|                    | ecution of VLIW instruction                                                                                     |     |

| 2.2.1.             | Read/Write operation in same VLIW instruction                                                                   |     |

| 2.2.2.             | Execution of Control Transfer Instruction                                                                       | 207 |

| Appendix                                         | 213 |

|--------------------------------------------------|-----|

| 1. Instruction Code Table                        | 213 |

| 2. Instruction Matrix                            | 226 |

| 2.1. Primary Ope-code                            | 226 |

| 2.2. Secondary Opecode                           | 227 |

| 3. Instruction / Device No. Correspondence table | 233 |

| 4. IACC0 special rule                            | 234 |

# **Table Contents**

| Table 1 #cond field and pseudo opecode               | 33  |

|------------------------------------------------------|-----|

| Table 2 #cond field and pseudo opecode               |     |

| Table 3 #ccond field and evaluation condition of LCR | 36  |

| Table 4 #ccond field and evaluation condition of LCR | 39  |

| Table 5 #cond field and pseudo opecode               | 39  |

| Table 6 #ccond field and evaluation condition of LCR |     |

| Table 7 #cond field and pseudo opecode               | 42  |

| Table 8 Pseudo opecode                               |     |

| Table 9 Pseudo opecode                               |     |

| Table 10 #cond field and Pseudo opecode              |     |

| Table 11 Result of ICC test and Value of CCCR(CCx)   |     |

| Table 12 #cond field and Pseudo opecode              | 61  |

| Table 13 Result of FCC test and value of CCCR(CCx)   | 61  |

| Table 14 Values of CCCR(CCx, CCy and CCz)            | 63  |

| Table 15 ANDCR                                       |     |

| Table 16 ORCR                                        |     |

| Table 17 XORCR                                       |     |

| Table 18 NANDCR                                      |     |

| Table 19 NORCR                                       |     |

| Table 20 ANDNCR.                                     |     |

| Table 21 ORNCR                                       |     |

| Table 22 NANDNCR                                     |     |

| Table 23 NORNCR                                      |     |

| Table 24 NOTCR                                       |     |

| Table 25 Values of #cond field                       |     |

| Table 26 Values of #cond field                       |     |

| Table 27 Values of #cond field                       |     |

| Table 28 Values of #cond field                       |     |

| Table 29 Values of #cond field                       |     |

| Table 30 Values of #cond field                       |     |

| Table 31 Values of #cond field                       |     |

| Table 32 Values of #cond field                       | 173 |

| Table 33 Values of #cond field                       |     |

| Table 34 Values of #cond field                       |     |

| Table 35 Values of #cond field                       |     |

| Table 36 Values of #cond field                       |     |

| Table 37 Values of #cond field                       |     |

| Table 38 Values of #cond field                       |     |

| Table 39 #cond field and pseudo opecode              |     |

| Table 40 Values of #ccond field                      |     |

| Table 41 Values of CCCR                              |     |

| Table 42 test results and values of CCCR             |     |

| Table 43 #cond field and pseudo ope-code             |     |

| Table 44 Values of #ccond field                      |     |

| Table 45 Values of CCCR                              |     |

| Table 46 Values of #cond field                       |     |

|                                                      | 192 |

| Table 48 Values of #cond field | 194 |

|--------------------------------|-----|

| Table 49 Values of #cond field | 196 |

| Table 50 Values of #cond field | 198 |

| Table 51 Values of #cond field | 200 |

| Table 52 Values of #cond field | 201 |

| Table 53 Values of #cond field | 203 |

#### 1. Instruction Set Reference

This chapter describes instruction set architecture, which are categorized into related instructions.

#### 1.1. Explanation of each term

#### Instruction table

This term is described about the ope-code of each instruction, op fields in instruction code, ope fields in instruction code and execution behavior.

#### Category

This term is described about instruction type of each instruction.

#### **Instruction format**

This term is described about instruction format of each instruction.

#### Assembler description

This term is described about suggested assembly language syntax.

#### **Behavior description**

This term is described about description of instruction execution.

#### **Operation example**

In the instruction which needs a complex operation, an example is shown in the table.

#### Altered register other than a destination register

This term is described an altered register which is not indicated by assembly description. For ICC, it is described that the flag may be altered by the instruction. A symbol O means that the flag may be altered by the instruction. A symbol X means that the flag does not altered by the instruction.

#### Occurrence exception

This term is described exceptions that may be occurred by the instruction.

## **Detected exception**

When the instruction detects exceptions, there are exceptions which do not initiate an exception processing and may store the information. This term is described about this kind of exception. When the instruction is non-excepting instruction, the detected exception is initiated by the COMMIT instruction. When the instruction is media instruction, the detected exception is initiated by executing MTRAP instruction.

## 1.2. Integer Instructions

#### 1.2.1. Add / Subtract (ADDSS and SUBSS are available for MB93405/MB93451.)

| Ope-code | op      | ope    | Operation                                       |

|----------|---------|--------|-------------------------------------------------|

| ADD      | 0000000 | 0000   | Add                                             |

| ADDcc    | 0000000 | 0001   | Add and ICC setting                             |

| ADDX     | 0000000 | 0010   | Add with carry                                  |

| ADDXcc   | 0000000 | 0011   | Add with carry and ICC setting                  |

| SUB      | 0000000 | 0100   | Subtract                                        |

| SUBcc    | 0000000 | 0101   | Subtract and ICC setting                        |

| SUBX     | 0000000 | 0110   | Subtract with carry                             |

| SUBXcc   | 0000000 | 0111   | Subtract with carry and ICC setting             |

| ADDI     | 0010000 | -      | Add (Immediate)                                 |

| ADDIcc   | 0010001 | -      | Add and ICC setting (Immediate)                 |

| ADDXI    | 0010010 | -      | Add with carry (Immediate)                      |

| ADDXIcc  | 0010011 | -      | Add with carry and ICC setting (Immediate)      |

| SUBI     | 0010100 | -      | Subtract (Immediate)                            |

| SUBIcc   | 0010101 | -      | Subtract and ICC setting (Immediate)            |

| SUBXI    | 0010110 | -      | Subtract with carry (Immediate)                 |

| SUBXIcc  | 0010111 | -      | Subtract with carry and ICC setting (Immediate) |

| ADDSS    | 1000110 | 000000 | Add with Signed Saturation                      |

| SUBSS    | 1000110 | 000001 | Substract with Signed Saturation                |

<sup>#:</sup> ADDSS and SUBSS are available for MB93405/MB93451.

## Category

Integer

## **Instruction Format (INT, Logic, Shift Operation (R-R))**

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 | 9 8 | 3 7 | 6 | 5 | 4 | 3  | 2  | 1 | 0 |

|----|-------------------|----------------------|-------------------|-------|-----|-----|---|---|---|----|----|---|---|

|    | GRk               | op                   | GRi               | -     | (   | ope |   |   |   | G] | Rj |   |   |

#### **Instruction Format (ADDSS,SUBSS)**

| 3 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 9 | 8   | 7 | 6 | 5 | 4 | 3 | 2  | 1 | 0 |

|---|-------------------|----------------------|-------------------|---------|-----|---|---|---|---|---|----|---|---|

|   | GRk               | op                   | GRi               | (       | ope |   |   |   |   | G | Rj |   |   |

#### Instruction Format (INT, Logic, Shift Operation (R-simm))

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 9 | 8 | 7 | 6  | 5   | 4 | 3 | 2 | 1 | 0 |

|----|-------------------|----------------------|-------------------|---------|---|---|----|-----|---|---|---|---|---|

|    | GRk               | op                   | GRi               |         |   |   | #s | :12 | , |   |   |   |   |

## Instruction Format (INT, Logic, Shift-cc Operation (R-R))

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 | 9 | 8 7 | 6 | 5 | 4 | 3 | 2  | 1 | 0 |

|----|-------------------|----------------------|-------------------|-------|---|-----|---|---|---|---|----|---|---|

|    | GRk               | op                   | GRi               |       |   | ope |   |   |   | G | Rj |   |   |

ICCi

#### Instruction Format (INT, Logic, Shift-cc Operation (R-simm))

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 | 9 | 8 | 7 | 6 | 5  | 4  | 3 | 2 | 1 | 0 |

|----|-------------------|----------------------|-------------------|-------|---|---|---|---|----|----|---|---|---|---|

|    | GRk               | op                   | GRi               |       |   |   |   |   | #s | 10 |   |   |   |   |

|    |                   |                      |                   | ICCi  |   |   |   |   |    |    |   |   |   |   |

#### **Assembler Syntax**

| ADD     | GRi, GRj, GRk        |

|---------|----------------------|

| ADDcc   | GRi, GRj, GRk, ICCi  |

| ADDX    | GRi, GRj, GRk, ICCi  |

| ADDXcc  | GRi, GRj, GRk, ICCi  |

| SUB     | GRi, GRj, GRk        |

| SUBcc   | GRi, GRj, GRk, ICCi  |

| SUBX    | GRi, GRj, GRk, ICCi  |

| SUBXcc  | GRi, GRj, GRk, ICCi  |

| ADDI    | GRi, #s12, GRk       |

| ADDIcc  | GRi, #s10, GRk, ICCi |

| ADDXI   | GRi, #s10, GRk, ICCi |

| ADDXIcc | GRi, #s10, GRk, ICCi |

| SUBI    | GRi, #s12, GRk       |

| SUBIcc  | GRi, #s10, GRk, ICCi |

| SUBXI   | GRi, #s10, GRk, ICCi |

| SUBXIcc | GRi, #s10, GRk, ICCi |

| ADDSS   | GRi, GRj, GRk        |

| SUBSS   | GRi, GRj, GRk        |

|         |                      |

#### **Description**

The integer addition and subtraction instructions add or subtract GRi and GRj (immediate instruction: sign\_ext (#s12) or sign\_ext (#s10)) and write the result in GRk.

The ADD instruction calculates "GRi+GRi".

The ADDX instruction calculates "GRi+GRj+C". C is the carry bit of ICCi.

The SUB instruction calculates "GRi - GRj".

The SUBX instruction calculates "GRi - GRj - C". C is the carry bit of ICCi.

The ADDcc, ADDXcc, SUBcc, and SUBXcc instructions and their immediate instructions change the integer condition code (ICC).

The ADDSS instruction adds a 32bit value of GRi to a 32bit value of GRj, and saturate, to pruduce a 32bit result. The result is placed into GRk. If the result is overflow as 32bit signed integer, maximum value of 32bit signed interger placed into GRk. (0x7FFFFFFF or 0x80000000)

The SUBSS instruction subrtacts a 32bit value of GRi to a 32bit value of GRj, and saturate,to pruduce a 32bit result. The result is placed into GRk. If the result is overflow as 32bit signed integer, maximum value of 32bit signed interger placed into GRk. (0x7FFFFFFF or 0x80000000)

#### Registers altered (except destination register)

ICCi ... instructions with "cc" only

N

Z

V

C

O

O

O

O

## **Occurrence Exceptions**

register\_exception (unimplement\_exception)

## **Detected Exceptions**

### 1.2.2. Multiply

| Ope-code | op      | ope  | Operation                                 |

|----------|---------|------|-------------------------------------------|

| SMUL     | 0000000 | 1000 | Signed Integer Multiply                   |

| SMULcc   | 0000000 | 1001 | Signed Integer Multiply and ICC setting   |

| UMUL     | 0000000 | 1010 | Unsigned Integer Multiply                 |

| UMULcc   | 0000000 | 1011 | Unsigned Integer Multiply and ICC setting |

| SMULI    | 0011000 | -    | Signed Integer Multiply (Immediate)       |

| SMULIcc  | 0011001 | -    | Signed Integer Multiply and ICC setting   |

|          |         |      | (Immediate)                               |

| UMULI    | 0011010 | -    | Unsigned Integer Multiply (Immediate)     |

| UMULIcc  | 0011011 | -    | Unsigned Integer Multiply and ICC setting |

|          |         |      | (Immediate)                               |

## Category

Integer

## **Instruction Format (INT, Logic, Shift Operation (R-R))**

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 | 9 | 3 7 | 6 | 5 | 4 | 3 | 2  | 1 | 0 |

|----|-------------------|----------------------|-------------------|-------|---|-----|---|---|---|---|----|---|---|

|    | GRk               | op                   | GRi               | -     | ( | ope |   |   |   | G | Rj |   |   |

## Instruction Format (INT, Logic, Shift Operation (R-simm))

| - | 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 9 | 8 | 7 | 6  | 5  | 4 | 3 | 2 | 1 | 0 |

|---|----|-------------------|----------------------|-------------------|---------|---|---|----|----|---|---|---|---|---|

|   |    | GRk               | op                   | GRi               |         |   |   | #8 | 12 | , |   |   |   |   |

## Instruction Format (INT, Logic, Shift-cc Operation (R-R))

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 | 9 | 8 7 | 6 | 5 | 4 | 3 | 2  | 1 | 0 |

|----|-------------------|----------------------|-------------------|-------|---|-----|---|---|---|---|----|---|---|

|    | GRk               | op                   | GRi               |       |   | ope |   |   |   | G | Rj |   |   |

|    | -                 | •                    |                   | ICCi  |   |     |   |   |   |   |    |   |   |

Instruction Format (INT, Logic, Shift-cc Operation (R-simm))

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 | 9 | 8 7 | 6 | 5  | 4  | 3 | 2 | 1 | 0 |

|----|-------------------|----------------------|-------------------|-------|---|-----|---|----|----|---|---|---|---|

|    | GRk               | op                   | GRi               |       |   |     |   | #s | 10 |   |   |   |   |

ICCi

## **Assembler Syntax**

| SMUL    | GRi, GRj, GRk        |

|---------|----------------------|

| SMULcc  | GRi, GRj, GRk, ICCi  |

| UMUL    | GRi, GRj, GRk        |

| UMULcc  | GRi, GRj, GRk, ICCi  |

| SMULI   | GRi, #s12, GRk       |

| SMULIcc | GRi, #s10, GRk, ICCi |

| UMULI   | GRi, #s12, GRk       |

UMULIcc GRi, #s10, GRk, ICCi

## **Description**

The integer multiply instructions multiply GRi and GRj (immediate instruction: sign\_ext (#s12) or sign\_ext (#s10)) and write the high-order 32 bits of the result in GRk and the low-order 32 bits in GRk+1.

The SMUL and SMULcc instructions calculate the product of signed integer word operands and write a signed integer doubleword as the result.

The UMUL and UMULcc instructions calculate the product of unsigned integer word operands and write an unsigned integer doubleword as the result.

The SMULcc and UMULcc instructions and their immediate instructions change the integer condition code (ICC) specified by ICCi field.

register\_exception (register\_not\_aligned) occur when the register number of GRk is an odd number.

#### Registers altered (except destination register)

ICCi ... instructions with "cc" only

| N | Z | V | C |

|---|---|---|---|

| О | О | X | X |

## **Occurrence Exceptions**

register\_exception (unimplement\_exception, register\_not\_aligned)

#### **Detected Exceptions**

#### 1.2.3. Multiply and Add / Subtract (These instructions are available for MB93405/MB93451.)

| Ope-code | op      | ope    | Operation                                      |

|----------|---------|--------|------------------------------------------------|

| SMASS    | 1000110 | 000110 | Signed Multiply and Add with Signed Saturation |

|          |         |        | (64bit + 32bit x 32bit -> 64 bit)              |

| SMSSS    | 1000110 | 000111 | Signed Multiply and Subtract with Signed       |

|          |         |        | Saturation (64bit – 32bit x32bit -> 64bit)     |

#### Category

Integer

#### **Instruction Format (SMASS,SMSSS)**

| 31 30 29 28 27 26 | 25 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 9 8 7 6 | 5 4 3 2 1 0 |

|-------------------|-------------------------|-------------------|---------------|-------------|

| -                 | op                      | GRi               | ope           | GRj         |

### **Assembler Syntax**

SMASS GRi, GRj SMSSS GRi, GRj

#### Description

#### Registers altered (except destination register)

none

#### **Occurrence Exceptions**

register\_exception (unimplement\_exception)

#### **Detected Exceptions**

## 1.2.4. Multiply to IACC (This instruction is available for MB93405/MB93451.)

| Ope-code | op      | ope    | Operation                                 |

|----------|---------|--------|-------------------------------------------|

| SMU      | 1000110 | 000101 | Signed Multiply (32bit x 32bit -> 64 bit) |

## Category

Integer

## **Instruction Format (SMASS,SMSSS)**

| 31 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 9 8 7 6 | 5 4 3 2 1 0 |

|----------------------|----------------------|-------------------|---------------|-------------|

| -                    | op                   | GRi               | ope           | GRj         |

## **Assembler Syntax**

SMU GRi, GRj

#### **Description**

SMU multiplies the 32bit value in GRi and the 32bit value in GRj.All operands are treated as signed values, to produce a 64bit result. The result is placed into IACC.

## Registers altered (except destination register)

none

## **Occurrence Exceptions**

register exception (unimplement exception)

## **Detected Exceptions**

#### 1.2.5. Divide

| Ope-code | op      | ope  | Operation                           |

|----------|---------|------|-------------------------------------|

| SDIV     | 0000000 | 1110 | Signed Integer Divide               |

| UDIV     | 0000000 | 1111 | Unsigned Integer Divide             |

| SDIVI    | 0011110 | -    | Signed Integer Divide (Immediate)   |

| UDIVI    | 0011111 | -    | Unsigned Integer Divide (Immediate) |

#### Category

Integer

#### **Instruction Format (INT, Logic, Shift Operation (R-R))**

| 3 | 1 3 | 30 29 | 28 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8  | 7 | 6 | 5 | 4 | 3 | 2  | 1 | 0 |

|---|-----|-------|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|----|---|---|---|---|---|----|---|---|

|   |     |       | GRk   |    |    |    |    |    | op | )  |    |    |    |    | G  | Ri |    |    | -  | -  |   | op | e |   |   |   | G | Rj |   |   |

#### **Instruction Format (INT, Logic, Shift Operation (R-simm))**

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 9 | 8 | 7 | 6  | 5  | 4 | 3 | 2 | 1 | 0 |

|----|-------------------|----------------------|-------------------|---------|---|---|----|----|---|---|---|---|---|

|    | GRk               | op                   | GRi               |         |   |   | #8 | 12 | , |   |   |   |   |

#### **Assembler Syntax**

| SDIV  | GRi, GRj, GRk  |

|-------|----------------|

| UDIV  | GRi, GRj, GRk  |

| SDIVI | GRi, #s12, GRk |

| UDIVI | GRi. #s12. GRk |

#### Description

The integer division instructions divide GRi by GRj (immediate instruction: sign\_ext (#s12)) and write the result in GRk. The surplus is not given as a result.

The SDIV instruction divides a signed integer word operand by a signed integer word operand and writes a signed integer word as the result.

The result of 0x80000000/ (-1) in a SDIV instruction is 0x7fffffff in division exception mask mode (ISR.EDEM=1), 0x80000000 in division exception detection mode.

Division\_exception cannot be masked because Division exception mask mode is for only overflow. The UDIV instruction divides an unsigned integer word operand by an unsigned integer word operand and writes an unsigned integer word as the result.

The UDIVI instruction divides 32-bit signed integer which results from sign\_ext(#s12) regarding as 32-bit unsigned integer.

#### Registers altered (except destination register)

none

#### **Occurrence Exceptions**

division\_exception register\_exception (unimplement\_exception)

## **Detected Exceptions**

### 1.2.6. Logical Operations

| Ope-code | op      | ope  | Operation                       |

|----------|---------|------|---------------------------------|

| AND      | 0000001 | 0000 | And                             |

| ANDcc    | 0000001 | 0001 | And and ICC setting             |

| OR       | 0000001 | 0010 | Or                              |

| ORcc     | 0000001 | 0011 | Or and ICC setting              |

| XOR      | 0000001 | 0100 | Xor                             |

| XORcc    | 0000001 | 0101 | Xor and ICC setting             |

| NOT      | 0000001 | 0110 | Not                             |

| ANDI     | 0100000 | -    | And (Immediate)                 |

| ANDIcc   | 0100001 | -    | And and ICC setting (Immediate) |

| ORI      | 0100010 | -    | Or (Immediate)                  |

| ORIcc    | 0100011 | -    | Or and ICC setting (Immediate)  |

| XORI     | 0100100 | -    | Xor (Immediate)                 |

| XORIcc   | 0100101 | -    | Xor and ICC setting (Immediate) |

## Category

Integer

## **Instruction Format (INT, Logic, Shift Operation (R-R))**

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 | 9 | 8 7 | 6 | 5 | 4 | 3 | 2  | 1 | 0 |

|----|-------------------|----------------------|-------------------|-------|---|-----|---|---|---|---|----|---|---|

|    | GRk               | op                   | GRi               | -     |   | ope |   |   |   | G | Rj |   |   |

## **Instruction Format (NOT Operation (R-R))**

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 | 9 8 | 7  | 6 | 5 4 | 3 | 2  | 1 | 0 |

|----|-------------------|----------------------|-------------------|-------|-----|----|---|-----|---|----|---|---|

|    | GRk               | op                   | -                 | -     | o   | pe |   |     | G | Rj |   |   |

## Instruction Format (INT, Logic, Shift Operation (R-simm))

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 9 | 8 | 7 | 6  | 5  | 4 | 3 | 2 | 1 | 0 |

|----|-------------------|----------------------|-------------------|---------|---|---|----|----|---|---|---|---|---|

|    | GRk               | op                   | GRi               |         |   |   | #8 | 12 |   |   |   |   |   |

## **Instruction Format (INT, Logic, Shift-cc Operation (R-R))**

| 3 | 31 30 | 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 | 9 | 8 7 | 6 | 5 | 4 | 3 | 2  | 1 | 0 |

|---|-------|----------------|----------------------|-------------------|-------|---|-----|---|---|---|---|----|---|---|

|   |       | GRk            | op                   | GRi               | ICCi  |   | ope |   |   |   | G | Rj |   |   |

## Instruction Format (INT, Logic, Shift-cc Operation (R-simm))

| 1 | 31 3 | 30 29 28 27 26 2 | 25 | 24 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11  | 10 | 9 | 8 | 7 | 6 | 5  | 4  | 3 | 2 | 1 | 0 |

|---|------|------------------|----|-------|----|----|----|----|----|----|----|----|----|----|----|-----|----|---|---|---|---|----|----|---|---|---|---|

|   |      | GRk              |    |       |    | op | )  |    |    |    |    | G  | Ri |    |    | ICO | Ci |   |   |   |   | #s | 10 |   |   |   |   |

## **Assembler Syntax**

| AND    | GRi, GRj, GRk        |

|--------|----------------------|

| ANDcc  | GRi, GRj, GRk, ICCi  |

| OR     | GRi, GRj, GRk        |

| ORcc   | GRi, GRj, GRk, ICCi  |

| XOR    | GRi, GRj, GRk        |

| XORcc  | GRi, GRj, GRk, ICCi  |

| NOT    | GRj, GRk             |

| ANDI   | GRi, #s12, GRk       |

| ANDIcc | GRi, #s10, GRk, ICCi |

| ORI    | GRi, #s12, GRk       |

| ORIcc  | GRi, #s10, GRk, ICCi |

| XORI   | GRi, #s12, GRk       |

| XORIcc | GRi, #s10, GRk, ICCi |

## **Description**

The integer logical instructions execute logical operations on GRi and GRj bit by bit (immediate instruction: GRi and sign\_ext (#s12) or sign\_ext (#s10)) and write the result in GRk. The ANDcc, ORcc, and XORcc instructions and their immediate instructions change the integer condition code (ICC) specified by ICCi field.

## **Registers altered (except destination register)**

#### **Occurrence Exceptions**

register\_exception (unimplement\_exception)

#### **Detected Exceptions**

None

### 1.2.7. Shift (SLASS instruction is available for MB93405/MB93451.)

| Ope-code | op      | ope    | Operation                                       |

|----------|---------|--------|-------------------------------------------------|

| SLL      | 0000001 | 1000   | Shift Left Logical                              |

| SLLcc    | 0000001 | 1001   | Shift Left Logical and ICC setting              |

| SRL      | 0000001 | 1010   | Shift Right Logical                             |

| SRLcc    | 0000001 | 1011   | Shift Right Logical and ICC setting             |

| SRA      | 0000001 | 1100   | Shift Right Arithmetic                          |

| SRAcc    | 0000001 | 1101   | Shift Right Arithmetic and ICC setting          |

| SLLI     | 0101000 | -      | Shift Left Logical (Immediate)                  |

| SLLIcc   | 0101001 | -      | Shift Left Logical and ICC setting (Immediate)  |

| SRLI     | 0101010 | -      | Shift Right Logical (Immediate)                 |

| SRLIcc   | 0101011 | -      | Shift Right Logical and ICC setting (Immediate) |

| SRAI     | 0101100 | -      | Shift Right Arithmetic (Immediate)              |

| SRAIcc   | 0101101 | -      | Shift Right Arithmetic and ICC setting          |

|          |         |        | (Immediate)                                     |

| SLASS    | 1000110 | 000010 | Shift Left Arithmetic with Signed Saturation    |

<sup>#:</sup> SLASS is available for MB93405/MB93451.

## Category

Integer

#### **Instruction Format (INT, Logic, Shift Operation (R-R))**

| 31 | 30 29 28 27 26 25 2 | 24 23 22 21 20 19 18 1 | 17 16 15 14 13 12 1 | 11 10 | 9 8 | 3 7 | 6 | 5 | 4 | 3 | 2   | 1 | 0 |  |

|----|---------------------|------------------------|---------------------|-------|-----|-----|---|---|---|---|-----|---|---|--|

|    | GRk                 | op                     | GRi                 | -     |     | ope |   |   |   | C | ìRj |   |   |  |

#### **Instruction Format (SLASS)**

| 31 3 | 30 29 28 27 26 25 2 | 24 23 22 21 20 19 18 1 | 17 16 15 14 13 12 | 11 10 9 8 7 6 | 5 4 3 2 1 0 |

|------|---------------------|------------------------|-------------------|---------------|-------------|

|      | GRk                 | ор                     | GRi               | ope           | GRi         |

## **Instruction Format (INT, Logic, Shift Operation (R-simm))**

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 9 | 8 | 7 | 6  | 5  | 4 | 3 | 2 | 1 | 0 |

|----|-------------------|----------------------|-------------------|---------|---|---|----|----|---|---|---|---|---|

|    | GRk               | op                   | GRi               |         |   |   | #8 | 12 |   |   |   |   |   |

## Instruction Format (INT, Logic, Shift-cc Operation (R-R))

| 3 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 | 9 | 8 7 | 6 | 5 | 4 | 3 | 2  | 1 | 0_ |

|---|-------------------|----------------------|-------------------|-------|---|-----|---|---|---|---|----|---|----|

|   | GRk               | op                   | GRi               | ICCi  |   | ope |   |   |   | G | Rj |   |    |

#### **Instruction Format (INT, Logic, Shift-cc Operation (R-simm))**

| 31 | 30 29 28 27 26 25 2 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 | 9 8 | 7 | 6 | 5  | 4  | 3 | 2 | 1 | 0 |

|----|---------------------|----------------------|-------------------|-------|-----|---|---|----|----|---|---|---|---|

|    | GRk                 | op                   | GRi               | ICCi  |     |   |   | #8 | 10 | 1 |   |   |   |

#### Assembler Syntax

| SLL    | GRi, GRj, GRk        |

|--------|----------------------|

| SLLcc  | GRi, GRj, GRk, ICCi  |

| SRL    | GRi, GRj, GRk        |

| SRLcc  | GRi, GRj, GRk, ICCi  |

| SRA    | GRi, GRj, GRk        |

| SRAcc  | GRi, GRj, GRk, ICCi  |

| SLLI   | GRi, #s12, GRk       |

| SLLIcc | GRi, #s10, GRk, ICCi |

| SRLI   | GRi, #s12, GRk       |

| SRLIcc | GRi, #s10, GRk, ICCi |

| SRAI   | GRi, #s12, GRk       |

| SRAIcc | GRi, #s10, GRk, ICCi |

| SLASS  | GRi, GRj, GRk        |

#### Description

The integer shift instructions shift GRi by the number of bits implied by the shift-count and write the result in GRk. The shift-count is specified by the low-order 5 bits of GRj (immediate instruction: sign ext (#s12) or sign ext (#s10)).

The SLL instruction shifts GRi to the left, replacing the vacated positions with zero.

The SRL instruction shifts GRi to the right, replacing the vacated positions with zero.

The SRA instruction shifts GRi to the right, replacing the vacated positions with the highest bit of GRi.

The SLLcc SRLcc, and SRAcc instructions and their immediate instructions change the integer condition code (ICC) specified by ICCi field.

Each bit of shift out is calculated in logical OR, and result in the C flag of ICC in SRAcc instruction.

Each bit of shift out is calculate in logical OR, and result in the V flag of ICC in SLLcc instruction.

SLASS shifts a 32bit value of GRi toward left at a 32bit value of GRj, and saturate,to pruduce a 32bit result. The result is placed into GRk. If the result is overflow as 32bit signed integer, maximum value of 32bit signed integer placed into GRk. (0x7FFFFFFF or 0x80000000)

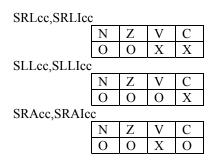

## Registers altered (except destination register)

ICCi ... instructions with "cc" only

#### **Occurrence Exceptions**

register\_exception (unimplement\_exception)

## **Detected Exceptions**

#### 1.2.8. Byte Compare Instruction

| Ope code | op      | ope  | Operation                           |

|----------|---------|------|-------------------------------------|

| CMPB     | 0000000 | 1100 | Byte Comparison and ICC field       |

| CMPBA    | 0000000 | 1101 | OR of Byte Comparison and ICC field |

#### Category

Integer

#### Instruction format (INT, Logic, Shift-cc operation (R – R))

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 | 9 8 | 3 7 | 6 | 5 | 4 | 3 | 2  | 1 | 0 |

|----|-------------------|----------------------|-------------------|-------|-----|-----|---|---|---|---|----|---|---|

|    | -                 | op                   | GRi               | ICCi  |     | ope |   |   |   | G | Rj |   |   |

#### Assembler description

CMPB GRi,GRj,ICCi CMPBA GRi,GRj,ICCi

#### Description

The CMPB instruction compares  $GRi_0$  with  $GRj_0$ ; when they match, the instruction writes 1 to ICCi.n; when they do not match, the instruction writes 0 to ICCi.n. Simultaneously, the instruction compares  $GRi_1$  with  $GRj_1$ , and when they match, the instruction writes 1 to ICCi.z; when they do not match, the instruction writes 0 to ICCi.z. Simultaneously, the instruction compares  $GRi_2$  with  $GRj_2$ , and when they match, the instruction writes 1 to ICCi.v; when they do not match, the instruction writes 0 to ICCi.v. Simultaneously, the instruction compares  $GRi_3$  with  $GRj_3$ , and when they match, the instruction writes 1 to ICCi.c; when they do not match, the instruction writes 0 to ICCi.c.

The CMPBA instruction compares  $GRi_0$  with  $GRj_0$ ;  $GRi_1$  with  $GRj_1$ ;  $GRi_2$  with  $GRj_2$ ; and  $GRi_3$  with  $GRj_3$ , respectively; when there is at least one match, the instruction writes 1 to ICCi.c; when there is no match at all, the instruction writes 0 to ICCi.n, ICCi.z, and ICCi.v.

Indexes used for GRi and GRj show the byte locations in the register. The relationship between byte location and bit position is shown below:

GRi0 = GRi (bit 31 to bit 24), GRi1 = GRi (bit 23 to bit 16) GRi2 = GRi (bit 15 to bit 8), GRi3 = GRi (bit 7 to bit 0)

Note: The same relationship also applies to GRj.

#### Registers altered (except destination register)

None

## **Occurrence Exceptions**

register\_exception (unimplement\_exception)

#### **Detected Exceptions**

None

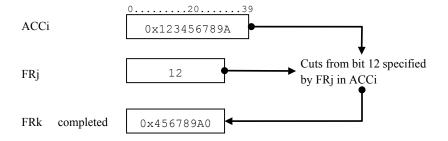

#### 1.2.9. Accumulator Cut Instruction (This instruction is available for MB93405/MB93451.)

| Ope code | op      | ope    | Operation                                     |

|----------|---------|--------|-----------------------------------------------|

| SCUTSS   | 1000110 | 000100 | Signed Cut with Signed Saturation (Immediate) |

#### Category

Integer

#### **Instruction format (SCTUTSS)**

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 9 8 7 6 | 5 4 3 2 1 0 |

|----|-------------------|----------------------|-------------------|---------------|-------------|

|    | GRk               | op                   | -                 | ope           | GRj         |

#### Assembler description

SCUTSS GRj,GRk

#### **Description**

SCUTSS round the 64bit value of Iacc with bit\_position of 7bit signed value of GRj, and cut and saturate, to pruduce a 32bit result. The result is placed into GRk. At round phase, if (32-bit\_posion)th bit of Iacc is '1', 2^(32-bit\_position) is added to IACC. At cut phase, if bit\_position is minus value, the value of IACC is entended with sign bit. At saturation phase, if the result is overflow as 32bit signed integer, maximum value of 32bit signed interger placed into GRk. (0x7FFFFFFF or 0x80000000)

Ex.

IACC: FFFFFEDC BA987654

: without round increment, saturation case

GRj : 16(0000010)

GRk: FEDCBA98

IACC: FFFFFEDC BA987654

: with round increment case

<u>GRj : 12(0000000c)</u>

GRk: FFEDCBAA

IACC: FFFFFEDC BA987654

: with sign extention case

GRj : -4(FFFFFFFC)

GRk: FFFFFEE

IACC: FFFFFEDC BA987654

: with saturation case

GRj : 24(00000018)

GRk: 80000000

#### **Registers altered (except destination register)**

None

#### **Occurrence Exceptions**

register exception (unimplement exception)

## **Detected Exceptions**

None

## 1.3. Load/Store Instructions

#### 1.3.1. Load GR

| Ope-code | op      | ope    | Operation                                |

|----------|---------|--------|------------------------------------------|

| LDSB     | 0000010 | 000000 | Load Signed Byte                         |

| LDUB     | 0000010 | 000001 | Load Unsigned Byte                       |

| LDSH     | 0000010 | 000010 | Load Signed Halfword                     |

| LDUH     | 0000010 | 000011 | Load Unsigned Halfword                   |

| LD       | 0000010 | 000100 | Load Word                                |

| LDD      | 0000010 | 000101 | Load Double                              |

| LDSBU    | 0000010 | 010000 | Load Signed Byte with Update Index       |

| LDUBU    | 0000010 | 010001 | Load Unsigned Byte with Update Index     |

| LDSHU    | 0000010 | 010010 | Load Signed Halfword with Update Index   |

| LDUHU    | 0000010 | 010011 | Load Unsigned Halfword with Update Index |

| LDU      | 0000010 | 010100 | Load Word with Update Index              |

| LDDU     | 0000010 | 010101 | Load Double with Update Index            |

| LDSBI    | 0110000 | -      | Load Signed Byte (Immediate)             |

| LDSHI    | 0110001 | -      | Load Signed Halfword (Immediate)         |

| LDI      | 0110010 | -      | Load Word (Immediate)                    |

| LDDI     | 0110011 | -      | Load Double (Immediate)                  |

| LDUBI    | 0110101 | -      | Load Unsigned Byte (Immediate)           |

| LDUHI    | 0110110 | -      | Load Unsigned Halfword (Immediate)       |

## Category

Integer

## Instruction Format (Load/Store (R-R))

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 9 8 7 6 | 5 4 3 2 1 0 |

|----|-------------------|----------------------|-------------------|---------------|-------------|

|    | GRk               | op                   | GRi               | ope           | GRj         |

## **Instruction Format (Load/Store (R-simm))**

| 3 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 9 | 8 7 | 6 | 5  | 4 | 3 | 2 | 1 | 0 |

|---|-------------------|----------------------|-------------------|---------|-----|---|----|---|---|---|---|---|

|   | GRk               | op                   | GRi               |         |     | d | 12 |   |   |   |   |   |

## **Assembler Syntax**

| LDSB  | @(GRi, GRj), GRk |

|-------|------------------|

| LDUB  | @(GRi, GRj), GRk |

| LDSH  | @(GRi, GRj), GRk |

| LDUH  | @(GRi, GRj), GRk |

| LD    | @(GRi, GRj), GRk |

| LDD   | @(GRi, GRj), GRk |

| LDSBU | @(GRi, GRj), GRk |

| LDUBU | @(GRi, GRj), GRk |

|-------|------------------|

| LDSHU | @(GRi, GRj), GRk |

| LDUHU | @(GRi, GRj), GRk |

| LDU   | @(GRi, GRj), GRk |

| LDDU  | @(GRi, GRj), GRk |

| LDSBI | @(GRi, d12), GRk |

| LDUBI | @(GRi, d12), GRk |

| LDSHI | @(GRi, d12), GRk |

| LDUHI | @(GRi, d12), GRk |

| LDI   | @(GRi, d12), GRk |

| LDDI  | @(GRi, d12), GRk |

#### **Description**

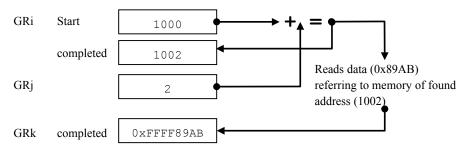

The integer Load instructions calculate "GRi + GRj" as an effective address (immediate instruction: "GRi + sign\_ext (d12)") and copy data from memory to a general-purpose register (GR). Byte or halfword data is written in the GRk register which is right-justified and it is either sign-extended or zero-extended on the left, depending on whether or not the opecode specifies a signed or unsigned operation, respectively. In doubleword Load instruction, it is necessary to set the register number of GRk as an even number with software, and the high-order word is written in the even register and the low-order word in the odd. (sign\_ext(X): X extended with a sign)

An instruction with "update" form calculates "GRi + GRj" as an effective address and writes the result in GRi.

The mem\_address\_not\_aligned exception occurs when the effective address is not aligned on a halfword boundary in halfword Load instruction, when it is not aligned on a word boundary in word Load instruction or when it is not aligned on a doubleword boundary in doubleword Load instruction.

The register\_exception (register\_not\_aligned) exception occurs when the register number of GRk is not an even number in doubleword Load instruction.

When an imprecise exception occurs in the Load with Update Index instruction, it completes to write the effective address in GRi and it does not complete to copy data from memory indicating by the effective address to GRk.

#### **Operation example**

## Registers altered (except destination register)

GRi ... Instruction with "update" form only

#### **Occurrence Exceptions**

mem address not aligned (except byte Load instruction)

data\_access\_exception

data\_access\_MMU\_miss

data\_access\_error

register\_exception (unimplement\_exception, register\_not\_aligned)

## **Detected Exceptions**

#### 1.3.2. Load FR

| Ope-code | op      | ope    | Operation                                   |

|----------|---------|--------|---------------------------------------------|

| LDBF     | 0000010 | 001000 | Load Byte FR register                       |

| LDHF     | 0000010 | 001001 | Load Halfword FR register                   |

| LDF      | 0000010 | 001010 | Load FR register                            |

| LDDF     | 0000010 | 001011 | Load Double FR register                     |

| LDBFU    | 0000010 | 011000 | Load Byte FR register with Update Index     |

| LDHFU    | 0000010 | 011001 | Load Halfword FR register with Update Index |

| LDFU     | 0000010 | 011010 | Load FR register with Update Index          |

| LDDFU    | 0000010 | 011011 | Load Double FR register with Update Index   |

| LDBFI    | 0111000 | -      | Load Byte FR register (Immediate)           |

| LDHFI    | 0111001 | -      | Load Halfword FR register (Immediate)       |

| LDFI     | 0111010 | -      | Load FR register (Immediate)                |

| LDDFI    | 0111011 | -      | Load Double FR register (Immediate)         |

## Category

Integer

## **Instruction Format (Load/Store (R-R))**

| 2 | 31 30 2 | 9 28 27 26 25 | 5 24 23 22 21 20 19 | 18 1 | 17 16 15 | 5 14 13 | 3 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5 | 4 | 3 | 2  | 1 | 0 |

|---|---------|---------------|---------------------|------|----------|---------|------|----|----|----|---|---|---|---|---|---|----|---|---|

|   |         | FRk           | op                  |      | C        | iRi     |      |    |    | op | e |   |   |   |   | G | Rj |   |   |

## **Instruction Format (Load/Store (R-simm))**

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 9 8 7 6 5 4 3 2 1 0 | ) |

|----|-------------------|----------------------|-------------------|---------------------------|---|

|    | FRk               | op                   | GRi               | d12                       | 1 |

## **Assembler Syntax**

| LDBF  | @(GRi, GRj), FRk |

|-------|------------------|

| 2221  |                  |

| LDHF  | @(GRi, GRj), FRk |

| LDF   | @(GRi, GRj), FRk |

| LDDF  | @(GRi, GRj), FRk |

| LDBFU | @(GRi, GRj), FRk |

| LDHFU | @(GRi, GRj), FRk |

| LDFU  | @(GRi, GRj), FRk |

| LDDFU | @(GRi, GRj), FRk |

| LDBFI | @(GRi, d12), FRk |

| LDHFI | @(GRi, d12), FRk |

| LDFI  | @(GRi, d12), FRk |

| LDDFI | @(GRi, d12), FRk |

## Description

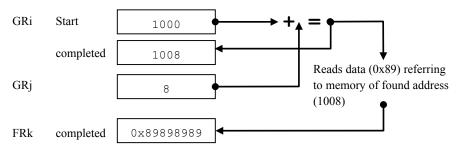

The floating-point Load instructions calculate "GRi + GRj" as an effective address (immediate instruction: " $GRi + sign\_ext$  (d12)") and copy data from memory to FR.

The LDBF instruction copies byte data from memory to all byte positions of FR without a signed extension.

The LDHF instruction copies halfword aligned data from memory to all halfword positions of FR without a signed extension.

The LDF instruction copies word aligned data from memory to FR.

The LDDF instruction copies doubleword aligned data from memory to FRk and FRk+1.

An instruction with "update" form calculates "GRi + GRj" as an effective address and writes the result in GRi.

The mem\_address\_not\_aligned exception occurs when the effective address is not aligned on a halfword boundary in halfword Load instruction, when it is not aligned on a word boundary in word Load instruction, when it is not aligned on a doubleword boundary in doubleword Load instruction.

The register\_exception (register\_not\_aligned) exception occurs when the register number of FRk is not an even number in doubleword Load instruction.

When an imprecise exception occurs in the Load with Update Index instruction, it completes to write the effective address in GRi and it does not complete to copy data from memory indicating by the effective address to FRk.

#### **Operation example**

LDBFU @(GRi,GRj),FRk

#### Registers altered (except destination register)

GRi ... Instruction with update only

#### **Occurrence Exceptions**

fp\_disabled

mem\_address\_not\_aligned

data\_access\_exception

data\_access\_MMU\_miss

data\_access\_error

register\_exception (unimplement\_exception, register\_not\_aligned)

## **Detected Exceptions**

#### **1.3.3.** Store GR

| Ope-code | op      | ope    | Operation                        |

|----------|---------|--------|----------------------------------|

| STB      | 0000011 | 000000 | Store Byte                       |

| STH      | 0000011 | 000001 | Store Halfword                   |

| ST       | 0000011 | 000010 | Store Word                       |

| STD      | 0000011 | 000011 | Store Double                     |

| STBU     | 0000011 | 010000 | Store Byte with Update Index     |

| STHU     | 0000011 | 010001 | Store Halfword with Update Index |

| STU      | 0000011 | 010010 | Store Word with Update Index     |

| STDU     | 0000011 | 010011 | Store Double with Update Index   |

| STBI     | 1010000 | -      | Store Byte (Immediate)           |

| STHI     | 1010001 | -      | Store Halfword (Immediate)       |

| STI      | 1010010 | =.     | Store Word (Immediate)           |

| STDI     | 1010011 | -      | Store Double (Immediate)         |

#### Category

Integer

#### **Instruction Format (Load/Store (R-R))**

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 9 8 7 6 | 5 4 3 2 1 0 |

|----|-------------------|----------------------|-------------------|---------------|-------------|

|    | GRk               | op                   | GRi               | ope           | GRj         |

#### **Instruction Format (Load/Store (R-simm))**

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 9 | 8 | 7 | 6 | 5  | 4 | 3 | 2 | 1 | 0 |

|----|-------------------|----------------------|-------------------|---------|---|---|---|----|---|---|---|---|---|

|    | GRk               | op                   | GRi               |         |   |   | d | 12 |   |   |   |   |   |

## **Assembler Syntax**

| STB  | GRk, @(GRi, GRj) |

|------|------------------|

| STH  | GRk, @(GRi, GRj) |

| ST   | GRk, @(GRi, GRj) |

| STD  | GRk, @(GRi, GRj) |

| STBU | GRk, @(GRi, GRj) |

| STHU | GRk, @(GRi, GRj) |

| STU  | GRk, @(GRi, GRj) |

| STDU | GRk, @(GRi, GRj) |

| STBI | GRk, @(GRi, d12) |

| STHI | GRk, @(GRi, d12) |

| STI  | GRk, @(GRi, d12) |

| STDI | GRk, @(GRi, d12) |

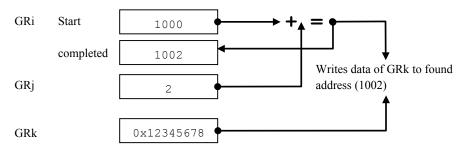

## Description

The integer Store instructions calculate "GRi + GRj" as an effective address (immediate instruction: "GRi + sign\_ext (d12)") and copy data from a general-purpose register(GRk) into memory. In doubleword Store instruction, it is necessary to set the register number of GRk as

an even number with software, and the high-order word is stored in memory from the even register and the low-order word from the odd. (sign ext (X): X extended with a sign)

An instruction with "update" form calculates "GRi + GRj" as an effective address and writes the result in GRi.

The mem\_address\_not\_aligned exception occurs when the effective address is not aligned on a halfword boundary in halfword Store instruction, when it is not aligned on a word boundary in word Store instruction or when it is not aligned on a doubleword boundary in doubleword Store instruction.

The register\_exception (register\_not\_aligned) occurs when the register number of GRk is an odd number in doubleword Store instruction.

When an imprecise exception occurs in the Store with Update Index instruction, it completes to write the effective address in GRi and it does not complete to copy data from GRk to memory indicating by the effective address.

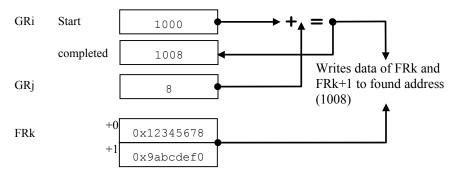

#### **Operation example**

STU GRk,@(GRi,GRj)

#### **Registers altered (except destination register)**

GRi ... Instruction with update only

#### **Occurrence Exceptions**

mem\_address\_not\_aligned (except byte Store)

data\_access\_exception

data\_access\_MMU\_miss

data\_access\_error

data\_store\_error

register\_exception (unimplement\_exception, register\_not\_aligned)

#### **Detected Exceptions**

#### 1.3.4. Store FR

| Ope-code | ор      | ope    | Operation                                    |

|----------|---------|--------|----------------------------------------------|

| STBF     | 0000011 | 001000 | Store Byte FR register                       |

| STHF     | 0000011 | 001001 | Store Halfword FR register                   |

| STF      | 0000011 | 001010 | Store FR register                            |

| STDF     | 0000011 | 001011 | Store Double FR register                     |

| STBFU    | 0000011 | 011000 | Store Byte FR register with Update Index     |

| STHFU    | 0000011 | 011001 | Store Halfword FR register with Update Index |

| STFU     | 0000011 | 011010 | Store FR register with Update Index          |

| STDFU    | 0000011 | 011011 | Store Double FR register with Update Index   |

| STBFI    | 1001110 | -      | Store Byte FR register (Immediate)           |

| STHFI    | 1001111 | -      | Store Halfword FR register (Immediate)       |

| STFI     | 1010101 | -      | Store FR register (Immediate)                |

| STDFI    | 1010110 | -      | Store Double FR register (Immediate)         |

## Category

Integer

## **Instruction Format (Load/Store (R-R))**

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 9 8 7 6 | 5 4 3 2 1 0 |

|----|-------------------|----------------------|-------------------|---------------|-------------|

|    | FRk               | op                   | GRi               | ope           | GRj         |

## **Instruction Format (Load/Store (R-simm))**

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 9 8 7 | 6 5 | 4 | 3 | 2 | 1 | 0 |

|----|-------------------|----------------------|-------------------|-------------|-----|---|---|---|---|---|

|    | FRk               | op                   | GRi               |             | d12 | 2 |   |   |   |   |

## **Assembler Syntax**

| STBF  | FRk, @(GRi, GRj) |

|-------|------------------|

| STHF  | FRk, @(GRi, GRj) |

| STF   | FRk, @(GRi, GRj) |

| STDF  | FRk, @(GRi, GRj) |

| STBFU | FRk, @(GRi, GRj) |

| STHFU | FRk, @(GRi, GRj) |

| STFU  | FRk, @(GRi, GRj) |

| STDFU | FRk, @(GRi, GRj) |

| STBFI | FRk, @(GRi, d12) |

| STHFI | FRk, @(GRi, d12) |

| STFI  | FRk, @(GRi, d12) |

| STDFI | FRk, @(GRi, d12) |

## Description

The floating-point Store instructions calculate "GRi + GRj" as an effective address (immediate instruction: " $GRi + sign\_ext$  (d12)") and copy data from FRk into memory.

The STBF instruction copies the lowest-order byte of FR to memory.

The STHF instruction copies low-order halfword data of FR to memory.

The STF instruction copies word data from FR to memory.

The STDF instruction copies doubleword data from FRk and FRk+1 to memory.

An instruction with "update" form calculates "GRi + GRj" as an effective address and writes the result in GRi.

The mem\_address\_not\_aligned exception occurs when the effective address is not aligned on a halfword boundary in halfword Store instruction, when it is not aligned on a word boundary in word Store instruction or when it is not aligned on a doubleword boundary in doubleword Store instruction

When an imprecise exception occurs in executing the Store with Update Index instruction, it completes to write the effective address in GRi and it does not complete to copy data from FRk to memory indicated by the effective address.

# Operation example

STDFU FRk,@(GRi,GRi)

#### Registers altered (except destination register)

GRi ... Instruction with update only

#### **Occurrence Exceptions**

fp\_disabled

mem\_address\_not\_aligned

data\_access\_exception

data\_access\_MMU\_miss

data\_access\_error

data\_store\_error

register exception (unimplement exception, register not aligned)

#### **Detected Exceptions**

#### 1.4. Data transfer Instructions

#### 1.4.1. Swap

| Ope-code | ор      | ope    | Operation                             |

|----------|---------|--------|---------------------------------------|

| SWAP     | 0000011 | 000101 | SWAP register with memory             |

| SWAPI    | 1001101 | -      | SWAP register with memory (Immediate) |

# Category

Control

# Instruction Format (Load/Store (R-R))

| <u>31 30 29 28 27 26 25</u> | <u>24 23 22 21 20 19 18</u> | 17 16 15 14 13 12 | 11 10 9 8 7 6 | 5 4 3 2 1 0 |

|-----------------------------|-----------------------------|-------------------|---------------|-------------|

| GRk                         | op                          | GRi               | ope           | GRj         |

## **Instruction Format (Load/Store (R-simm))**

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 9 | 8 7 | 6 | 5  | 4 | 3 | 2 | 1 | 0 |

|----|-------------------|----------------------|-------------------|---------|-----|---|----|---|---|---|---|---|

|    | GRk               | op                   | GRi               |         |     | d | 12 |   |   |   |   |   |

#### **Assembler Syntax**

SWAP @(GRi, GRj), GRk SWAPI @(GRi, d12), GRk

## **Description**

The swap instructions calculates "GRi+GRj" as an effective address (Immediate instruction: "GRi+sign\_ext (d12)") and exchange the contents of GRk with the contents of the word addressed memory location. The operation is performed atomically, that is, without allowing intervening interrupts. In a multiprocessor system, two or more processors executing SWAP or atomic Load-Store instruction addressing the same word or byte simultaneously are guaranteed to be executed without allowing intervening.

The mem\_address\_not\_aligned exception occurs when the effective address is not aligned on a word boundary.

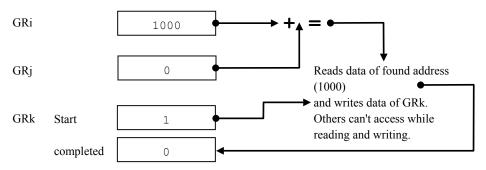

# Operation example

SWAP @(GRi,GRj),GRk

none

# **Occurrence Exceptions**

mem\_address\_not\_aligned

data\_access\_exception

data\_access\_MMU\_miss

data\_access\_error

data\_store\_error

register\_exception (unimplement\_exception)

# **Detected Exceptions**

#### 1.4.2. Move

| Ope-code  | op      | ope    | Operation            |

|-----------|---------|--------|----------------------|

| MOVGF     | 0000011 | 010101 | Move GR to FR        |

| MOVGFD    | 0000011 | 010110 | Move GR to FR Double |

| MOVFG     | 0000011 | 001101 | Move FR to GR        |

| MOVFGD    | 0000011 | 001110 | Move FR to GR Double |

| MOVGS(*1) | 0000011 | 000110 | Move GR to SPR       |

| MOVSG(*1) | 0000011 | 000111 | Move SPR to GR       |

<sup>(\*1)</sup> privileged instruction if source register or destination register is privileged.

#### Category

Integer, Control (MOVGS, MOVSG)

#### **Instruction Format (Register transfer instruction)**

| 31 | 30 29 28 27 26 25 | 24 23 22 21 20 19 18 | 17 16 15 14 13 12 | 11 10 9 8 7 6 | 5 4 3 2 1 0 |

|----|-------------------|----------------------|-------------------|---------------|-------------|

|    | FRk               | ор                   | sr                | ope           | GRj         |

#### **Assembler Syntax**

MOVGF GRj, FRk MOVGFD GRj, FRk MOVFG FRk, GRj MOVFGD FRk, GRj MOVGS GRj, SPR MOVSG SPR, GRj

("SPR" in assembler syntax is 12 bits field concatenating the FRk field and the sr field, following FRk with sr, in MOVGS instruction and MOVSG instruction.)

#### **Description**

The register transfer instructions copy the contents between GR, FR, and SPR.

The instruction MOVGF copies the contents of GRj to FRk.

The instruction MOVGFD copies the contents of GRj to FRk and from GRj+1 to FRk+1

The instruction MOVFG copies the contents of FRk to GRj.

The instruction MOVFGD copies the contents of FRk to GRj and from FRk+1 to GRj+1

The instruction MOVGS copies the contents of GRj to SPR.

The instruction MOVSG copies the contents of SPR to GRj.

The register\_exception (register\_not\_aligned) occurs when the register number of FRk or GRj is an odd number in doubleword transfer.

#### Registers altered (except destination register)

none

## **Occurrence Exceptions**

fp\_disabled register\_exception (unimplement\_exception, register\_not\_aligned) privileged\_instruction

# **Detected Exceptions**

#### 1.5. Control transfer Instructions

#### 1.5.1. Integer Conditional Branch

| Ope-code | op      | Operation                  |

|----------|---------|----------------------------|

| Bicc     | 0000110 | Integer Conditional Branch |

#### Category

Branch

#### **Instruction Format (Branch instruction)**