## DataGeneral

# ECLIPSE<sup>®</sup> S/140 Programmer's Reference

Warning: For devices compliant with FCC Rules This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instruction manual, may cause interference to radio communications. It has been tested and found to comply with the limits for Class A computing devices pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference, in which case the user, at his own expense, will be required to take whatever measures may be required to correct the interference.

## DataGeneral

# ECLIPSE<sup>®</sup> S/140 Programmer's Reference

## NOTICE

Data General Corporation (DGC) has prepared this document for use by DGC personnel, customers, and prospective customers. The information contained herein shall not be reproduced in whole or in part without DGC's prior written approval.

DGC reserves the right to make changes in specifications and other information contained in this document without prior notice, and the reader should in all cases consult DGC to determine whether any such changes have been made.

THE TERMS AND CONDITIONS GOVERNING THE SALE OF DGC HARDWARE PRODUCTS AND THE LICENSING OF DGC SOFTWARE CONSIST SOLELY OF THOSE SET FORTH IN THE WRITTEN CONTRACTS BETWEEN DGC AND ITS CUSTOMERS. NO REPRESENTATION OR OTHER AFFIRMATION OF FACT CONTAINED IN THIS DOCUMENT INCLUD-ING BUT NOT LIMITED TO STATEMENTS REGARD-ING CAPACITY, RESPONSE-TIME PERFORMANCE, SUITABILITY FOR USE OR PERFORMANCE OF PRODUCTS DESCRIBED HEREIN SHALL BE DEEMED TO BE A WARRANTY BY DGC FOR ANY PURPOSE, OR GIVE RISE TO ANY LIABILITY OF DGC WHATSOEVER.

IN NO EVENT SHALL DGC BE LIABLE FOR ANY INCIDENTAL, INDIRECT, SPECIAL OR CONSEQUEN-TIAL DAMAGES WHATSOEVER (INCLUDING BUT NOT LIMITED TO LOST PROFITS) ARISING OUT OF OR RELATED TO THIS DOCUMENT OR THE INFOR-MATION CONTAINED IN IT, EVEN IF DGC HAS BEEN ADVISED, KNEW OR SHOULD HAVE KNOWN OF THE POSSIBILITY OF SUCH DAMAGES.

DASHER, DATAPREP, ECLIPSE, ENTERPRISE, INFOS, microNOVA, NOVA, PROXI, SUPERNOVA, ECLIPSE MV/8000, TRENDVIEW, MANAP, and PRESENT are U.S. registered trademarks of Data General Corporation, and AZ-TEXT, DG/L, ECLIPSE MV/6000, REV-UP, SWAT, XODIAC, GENAP, DEFINE, CEO, SLATE, microECLIPSE, BusiPEN, BusiGEN, and BusiTEXT are U.S. trademarks of Data General Corporation.

Ordering No. 014-000642 © Data General Corporation, 1979, 1980, 1981, 1982, 1986 All Rights Reserved Printed in the United States of America Rev. 04, September 1986

## **CONTENTS**

## Chapter 1

## Introduction to the ECLIPSE S/140

- Main Storage I/O Management Main Processor

- 4 Packaging

- 4

- Software Support ECLIPSE/NOVA Line Compatibility 4

Chapter 2

3 3 3

## **Standard Features**

| 5<br>6  | Addressing Conventions<br>Addressing Modes                        |

|---------|-------------------------------------------------------------------|

| 7       | Auto-incrementing and Auto-decrementing                           |

| 7       | Bit Manipulation                                                  |

| 7       | Bit Instructions                                                  |

| 8       | Byte Manipulation                                                 |

| 8       | 이는 물건 그는 것 같아요. 그는 것 같아요. 물건 것을 물건을 가 전망가 많았다. 것 같아요. 전 것 같아요. 이것 |

| 0<br>8  | Byte Instructions                                                 |

| 9       | Number Manipulation                                               |

| 9<br>10 | Fixed Point Arithmetic Instructions                               |

| 575 B   | Decimal Arithmetic Instructions                                   |

| 10      | Logical Manipulation                                              |

| 10      | Logical Operations Instructions                                   |

| 11      | ALC Manipulation                                                  |

| 11      | ALC Instructions                                                  |

| 13      | The Stack                                                         |

| 13      | Stack Control Words                                               |

| 14      | Stack Protection                                                  |

| 15      | Initializing the Stack Control Words                              |

| 17      | Stack Instructions                                                |

| 17      | Reserved Storage Locations                                        |

| 18      | Program Execution                                                 |

| 18      | Program Flow Alteration                                           |

| 19      | Program Flow Interruption                                         |

| 19      | Program Flow Alteration Instructions                              |

| 21      | Extended Operation Feature                                        |

| 21      | Extended Operation Instructions                                   |

| 21      | Input/Output                                                      |

| 21      | Busy and Done Flags                                               |

| 21      | Programmed I/O                                                    |

| 21      | Data Channel I/O                                                  |

| 22      | I/O Interrupts                                                    |

| 24      | I/O Instructions                                                  |

|         |                                                                   |

| Basic I/O Devices                    |           |

|--------------------------------------|-----------|

| Real Time Clock                      |           |

| Asynchronous Line Controller         |           |

| Power Fail/Auto-restart              |           |

| Power Fail Instructions              |           |

| <b>Error Checking and Correction</b> |           |

| ERCC Instructions                    |           |

| Virtual Console                      |           |

| Cells                                |           |

| Cell Commands                        |           |

| Function Commands                    |           |

| Virtual Console Errors               |           |

| Memory Management and Protec         | tion Unit |

| MMPU Functions                       |           |

| MMPU Instructions                    |           |

## Chapter 3

28 30

33

34

36

38

38

38

38

39 39

75

90

## **Optional Features**

- Floating Point Instructions

- **Floating Point Arithmetic**

- Character Manipulation Instructions

- **Burst Multiplexor Channel**

- BMC Address Modes

- BMC Map

- BMC Instructions

## **Chapter 4**

## **Standard Machine Instructions**

Coding Aids Setting the Index Field

## **Chapter 5**

## I/O Instructions

- General I/O Instructions

- 76 Central Processor

- 78 Vectored I/O Instruction

- 81 Burst Multiplexor Channel

- 83 ERCC Error Correction

- 85 Memory Management and Protection Unit

- 90 Real Time Clock

- 90 Primary Asynchronous Line Input

- Primary Asynchronous Line Output

The Addressing Process

Standard I/O Device Codes

The ASCII Character Codes

## Chapter 1 Introduction to the ECLIPSE S/140

The Data General ECLIPSE S/140 is a scientific computer combining advanced architecture and high reliability. Four main components make up the ECLIPSE S/140, providing processing power and throughput capability. The components are:

- Main Storage system

- I/O Management system

- Main Processor

- Packaging

In addition, a generous selection of software supports the S/140 system, and the S/140 is compatible with DGC's NOVA computers.

## **Main Storage**

Maximum memory capacity of the ECLIPSE S/140 is 2 Mbytes (up to eight boards) in the form of semiconductor RAM. Each memory board contains four modules that support cycle times as low as 100 nanoseconds for a read operation and 200 nanoseconds for a write operation.

The ECLIPSE S/140 Memory Management and Protection Unit (MMPU) provides and protects individual user space within memory on a 2 Kbyte page basis. Protection modes include address validity, indirect, write, and I/O protections.

The Error Checking and Correction (ERCC) facility detects and corrects all single bit errors that occur on a memory board. The ERCC detects and reports errors by maintaining address and fault codes and requesting processor interrupts when errors occur. Memory cycle times are left unchanged if no error is detected. If an error is found, cycle time is increased by 200 nanoseconds.

## I/O Management

The S/140 is a powerful and highly reliable scientific computer. The advanced architectural features of this system provide configurational flexibility to match various computing needs. ECLIPSE S/140 supports an optional Burst Multiplexor Channel for high-speed data transfers.

The standard NOVA/ECLIPSE data channel provides I/O communication for both medium-speed and high-speed devices such as cartridge discs, magnetic tape, data channel line printers, and synchronous communications. Maximum data channel transfer rates are 2.0 Mbytes per second fast input, 1.4 Mbytes per second fast output.

Programmed I/O, with priority interrupt handling and vectoring capability for automatic dispatch to the correct interrupt handler, provides I/O communication for low-speed devices such as CRT terminals, paper tape punches, and card readers.

## **Main Processor**

The ECLIPSE S/140 main processor executes the standard ECLIPSE instruction set. Integer multiply/divide functions are implemented in firmware.

The main processor also executes the optional ECLIPSE floating point instruction set, using either Floating Point microcode, or the high-speed hardware Floating Point Processor.

The Character Instruction Set (CIS) simplifies the handling of strings of characters or bytes. It is especially useful in communications applications where long strings of bytes must be moved, compared, or checked against a reference.

On power up, the processor executes a self-test; if this test is successfully completed, the CPU enters virtual console mode. The virtual console replaces all but three switches on the front panel of the ECLIPSE S/140. Only the Power On/Off, Lock, and Reset/Program Load function switches remain.

## Packaging

The ECLIPSE S/140 is packaged in an easily accessed chassis that holds up to sixteen 15" x 15" printed circuit boards. The power supply consists of a 100-amp VNR unit and a slide-in power supply board. Battery back-up is standard.

## Software Support

Two proven operating systems and many advanced utilities and high level languages are available for the ECLIPSE S/140.

The Real-Time Disc Operating System (RDOS) supports real-time and batch operations, along with independent foreground/background processing. RDOS can manage up to 2 Mbytes of main memory in the ECLIPSE S/140.

The Advanced Operating System (AOS) uses adaptive resource management for efficient operation in multiuser environments. It can manage up to 2 Mbytes of main memory in the ECLIPSE S/140 and supports concurrent batch, timesharing, and real-time operations.

Many higher-level languages are also available, including FORTRAN IV, FORTRAN 5, Extended BASIC, PL/1, DG/L (an ALGOL-derivative, structured programming language), and Macroassembler.

## **ECLIPSE/NOVA Line Compatibility**

The ECLIPSE S/140 is compatible with Data General's NOVA line computers. You may execute any NOVA-based program on an ECLIPSE series computer, if several criteria are met. First, the program must not be dependent on instruction execution times or I/O transfer times, because ECLIPSE times may be faster. Second, the ECLIPSE system must contain at least as much memory and an equal number of I/O devices as your NOVA system. Third, it is important that your NOVA-based program *does not* use any of the following:

- ACL instructions specifying both the *no load* and the *never skip* options.

- The NOVA Memory Management and Protection Unit.

- The data channel increment or add-to-memory features.

- The instructions PUSH, POPA, SAV, MTSP, MTFP, MFSP, MFFP, LDB, STB, RET.

NOVA and ECLIPSE multiply/divide operations function the same way. However, each uses a different operation code.

NOVA and ECLIPSE floating point instructions are similar, but do not function the same way. Remember to check the instructions formats. Floating point data formats are the same for both machines.

## Chapter 2 Standard Features

In this chapter we discuss the standard features of the ECLIPSE S/140, and the assembly language instructions controlling these facilities. In the following chapter we describe optional facilities and their instructions. Chapters 4 and 5 contain complete instruction descriptions for standard and I/O instructions, respectively.

After explaining the standard addressing conventions of the ECLIPSE S/140, we discuss the functions of

Bit manipulation Byte manipulation Number manipulation Logical manipulation ALC manipulation The stack Reserved storage locations Program execution Extended operations I/O operation, interrupts, and vectoring I/O devices Power fail/auto-restart Error checking and correction The virtual console and Memory management and protection.

## **Addressing Conventions**

In this section we describe the various ways the ECLIPSE S/140 addresses locations in memory. We also define terms and concepts useful for understanding the addressing process in the ECLIPSE S/140.

Each addressed location in main memory consists of a 16-bit word. The first word in memory has the address 0, the next has the address 1, the next 2, and so forth.

The maximum amount of *logical* address space available to the programmer is 32,768 words. The *physical* address space, the amount of memory in the system, may be much larger. In the logical address space, the next sequential memory location after  $77777_8$  is location 0.

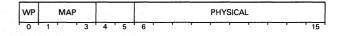

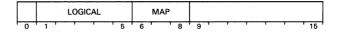

The MMPU controls the relationship between a logical address space and the physical address space. When the MMPU is enabled, it intercepts each memory reference and translates the 15-bit logical address into a 20-bit physical address. Unless the MMPU itself is being programmed, the translation process is invisible to the programmer.

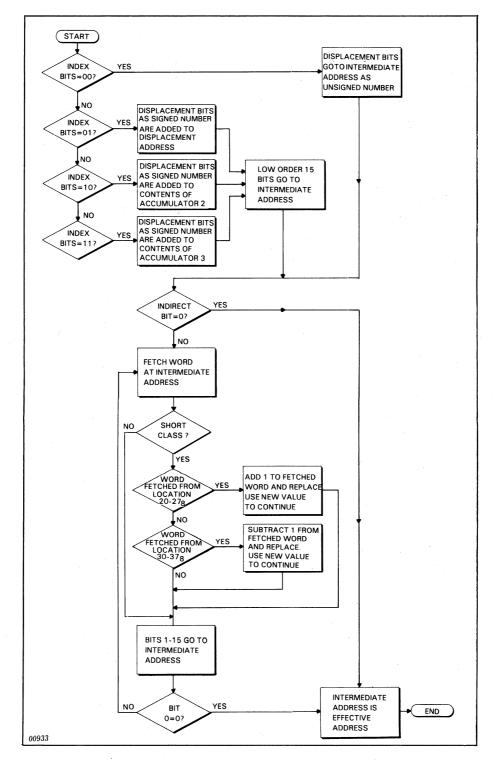

There are three modes of addressing: Absolute, P.C. Relative, and Accumulator Relative. You may use direct or indirect addressing in any of these modes. The following definitions are useful in understanding ECLIPSE S/140 addressing conventions.

Direct and Indirect Addressing — Direct addressing uses the intermediate address (the first address found) without modification. The intermediate address thus becomes the effective address.

Indirect addressing uses the intermediate address as a pointer to the next address. If bit 0 of that next address is 1, the address is used as a *pointer* to another address. A series of indirect addresses is called an *indirection chain*. The chain continues until an address is found with bit 0 equal to 0. Indirect protection is available to limit indirection levels to fifteen.

Indirect Bit — This is a bit in the instruction or address that is checked after each address calculation. If the indirect bit is 0, the effective address has been located. If it is 1, the word contains another indirect address.

*Index Bits* — These are bits in the instruction that control which of the three addressing modes the instruction uses. The correlation between index bits and addressing mode is shown in Table 1.1.

| Index Bits | Mode         |

|------------|--------------|

| 00         | Absolute     |

| 01         | PC relative  |

| 10         | AC2 relative |

| 11         | AC3 relative |

Table 1.1 Address mode selection

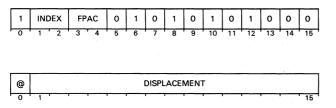

Displacement Bits — These are bits in the instruction that specify an address in memory. This address, added to an address specified by the mode, results in the effective address.

When the index bits are 00, the displacement is considered an unsigned integer. When the index bits are 01, 10, or 11, the displacement is considered a signed integer. Table 2.2 shows the range of the displacement field under various conditions.

| Index Bits | Range of Displacement Field           |                                           |  |  |

|------------|---------------------------------------|-------------------------------------------|--|--|

|            | Short Class                           | Extended Class                            |  |  |

| 00         | 0 to 377 <sub>8</sub>                 | 0 to 77777 <sub>8</sub>                   |  |  |

|            | or<br>0 to 255 <sub>10</sub>          | or<br>0 to 32,767 <sub>10</sub>           |  |  |

| 01         | -200 <sub>8</sub> to 177 <sub>8</sub> | -40000 <sub>8</sub> to 37777 <sub>8</sub> |  |  |

| 10         | or                                    | or                                        |  |  |

| 11         | -128 to +127 <sub>10</sub>            | -16,384 to<br>+ 16,383 <sub>10</sub>      |  |  |

Table 2.2 Ranges of displacement

*Effective Address Calculation* — This process converts the index, indirect, and displacement bits into an address to be used by the instruction.

*Intermediate Address* — This address is obtained by the effective address calculation before the indirect bit is checked.

Page Zero — The locations  $0-377_8$  in memory comprise page zero.

#### **Addressing Modes**

As mentioned earlier, three modes of addressing can be done in the ECLIPSE S/140. They are:

- Absolute addressing

- P.C. (program counter) relative addressing

- Accumulator relative addressing

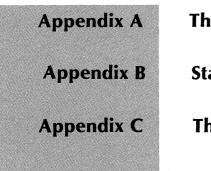

Figure 2.1 illustrates the three addressing modes.

Figure 2.1 Addressing modes

You can use direct or indirect addressing with each of these modes. With the right combination, any address in your logical address space is accessible.

Absolute Addressing Mode — In this mode, the intermediate address is set equal to the unmodified displacement. As a result, short class instructions specify locations in the range  $0-377_8$  in the absolute mode, because short class instructions are restricted to 8 bits in the displacement. Extended class instructions can reference any logical memory address using the absolute addressing mode.

Page zero thus is very important because any memory-reference instruction can address this area. You can use it as a common storage area for items that you frequently reference throughout a program. Note, however, that DGC reserves some of these locations for special purposes.

*P.C. Relative Addressing Mode* — The intermediate address is found by adding the displacement to the contents of the program counter.

Accumulator Relative Addressing Mode — The intermediate address is found by adding the displacement to the contents of bits 1-15 of the accumulator indicated by the index bits (you may use either AC2 or AC3).

#### Auto-incrementing and Auto-decrementing

During indirect addressing, certain reserved locations within the area of  $0-377_8$  (page zero) automatically increment or decrement their contents. The process is also called auto-indexing.

Auto-incrementing takes place if the intermediate address of a short class instruction falls into the range  $20-27_8$ , and the indirect bit is 1. The contents of the addressed location are incremented by 1, and the addressing chain continues, using the *incremented* value of the addressed location.

Auto-decrementing takes place if the intermediate address of a short class instruction falls into the range  $30-37_8$ , and the indirect bit is 1. The contents of the addressed location are decremented by 1, and the addressing chain continues, using the *decremented* value of the addressed location.

**NOTE:** The state of bit 0 before the increment or decrement determines whether the indirection chain is continued. Assume, for example, that an auto-increment location contains  $177777_8$  (all bits = 1, including bit 0), and the location is referenced as part of an indirection chain. After incrementing, the location contains all zeros. Because bit 0 was 1 before the increment, 000000 is treated as an intermediate address and the indirection chain continues.

You will find a flow diagram of the addressing process in Appendix A.

## **Bit Manipulation**

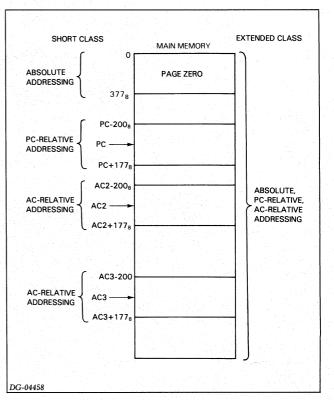

We use a 32-bit (2-word) *bit pointer* to address individual bits in memory. Bit 0 of the bit pointer is the indirect bit. If this bit is 1, the indirection chain (using bits 1-15 for the address each time) will be followed until a word is found with bit 0 set to 0. Bits 1-15 of this word become bits 1-15 of the bit pointer, and bits 0-15 of the next word become bits 16-31 of the bit pointer.

To determine the location of a desired bit, the address formed by the unsigned number contained in bits 1-15 of the bit pointer (the *base* address) is added to the number formed by the 12-bit unsigned number contained in bits 16-27 (the *offset*). The resulting address points to the word containing the desired bit. Bits 28-31 of the bit pointer contain a 4-bit unsigned number, which is the number of the desired bit in the addressed word.

Figure 2.2 diagrams the bit addressing process.

Figure 2.2 Bit addressing process

#### **Bit Instructions**

ECLIPSE S/140 instructions that manipulate bits do the following:

- Locate a bit in memory and set it to 0 or 1

- Test a bit, skipping the next word if the specified condition is true

- Add a number to the contents of one accumulator, based on the number of ones or high-order zeros found in the other accumulator

Some bit instructions use a bit pointer to locate a bit in memory. Others only affect bits within specified accumulators. In addition, a character instruction (**CMT**), uses a bit pointer, bit addressing and a bit table. Table 2.3 lists the bit instructions.

| Mnem | Instructions                       | Action                                                                                                               |

|------|------------------------------------|----------------------------------------------------------------------------------------------------------------------|

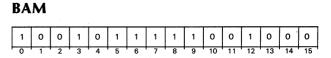

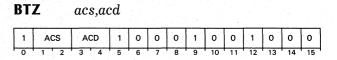

| вто  | Set Bit To One                     | Sets the bit addressed by the bit pointer to 1.                                                                      |

| BTZ  | Set Bit To Zero                    | Sets the bit addressed by the bit pointer to 0.                                                                      |

| СОВ  | Count Bits                         | Counts the number of ones in one<br>accumulator and adds that number to the<br>second accumulator.                   |

| LOB  | Locate Lead Bit                    | Counts the number of high-order zeros in<br>one accumulator and adds that number to<br>the second accumulator.       |

| LRB  | Locate And Reset<br>Lead Bit       | Performs a <i>Locate Lead Bit</i> instruction and sets the lead bit to 0.                                            |

| SNB  | Skip On Non-Zero<br>Bit            | Skips the next sequential word if the bit addressed by the bit pointer is 1.                                         |

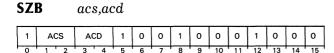

| SZB  | Skip On Zero Bit                   | Skips the next sequential word if the bit addressed by the bit pointer is 0.                                         |

| SZBO | Skip On Zero Bit<br>And Set To One | Sets the bit addressed by the bit pointer<br>to 1 and skips the next sequential word if<br>the bit was originally 0. |

Table 2.3 Bit instructions

## **Byte Manipulation**

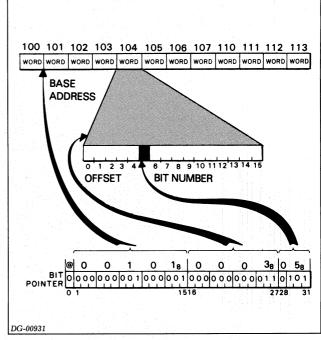

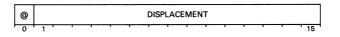

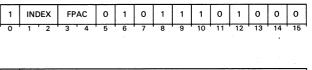

A byte in memory is selected by a sixteen bit byte pointer. Bits 0-14 of the byte pointer contain the memory address of a two byte word. Bit 15, the byte indicator, indicates which byte of the addressed location will be used. If bit 15 is 0, the high-order byte (bits 0-7) will be used. If bit 15 is 1, the low-order byte (bits 8-15) will be used. Figure 2.3 shows the format of a byte pointer.

#### **Byte Instructions**

The byte instructions are shown in Table 2.4. Note that when an instruction moves a byte to an accumulator it also clears the high-order half of the destination accumulator. When an instruction moves a byte from an accumulator to memory, it leaves unchanged the other byte contained in that word of memory.

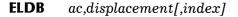

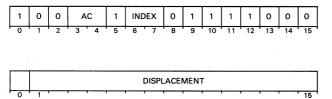

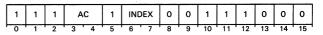

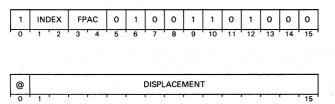

The two extended instructions, (**ELDB** and **ESTB**,) reference bytes with a byte pointer contained in the instruction coding. The two short class instructions (**LDB** and **STB**) use an accumulator to hold the byte pointer. The character instructions also use byte addressing.

Figure 2.3 Byte pointer format

| Mnem Instructions |            | Action                                                             |

|-------------------|------------|--------------------------------------------------------------------|

| LDB<br>ELDB       | Load Byte  | Places a byte of information into an<br>accumulator.               |

| STB<br>ESTB       | Store Byte | Stores the low order byte of an accumulator into a byte of memory. |

Table 2.4 Byte instructions

## **Number Manipulation**

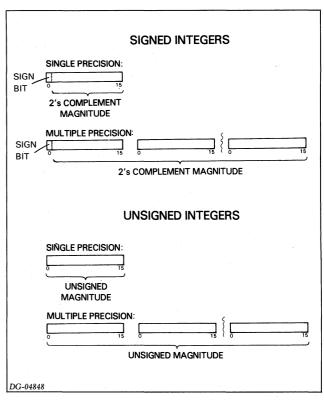

We represent a signed integer by a two's-complement number in one or more 16-bit words. The sign of the number is positive if bit 0 of the first word is 0 and negative if that bit is 1.

We represent an unsigned integer by using all the bits of one or more 16-bit words to represent the magnitude. Figure 2.4 illustrates integer format. Single precision integers are one word (16 bits) long, and multiple precision integers are two or more words long. As an example, Table 2.5 shows the range of single and double precision numbers represented by this format:

In addition, there is a value called *carry*. A change in the value of carry indicates an overflow during fixed point arithmetic operations.

## **Fixed Point Arithmetic Instructions**

There are twenty-six ECLIPSE S/140 instructions which perform fixed point arithmetic. These instructions:

- Perform binary arithmetic on operands in accumulators.

- Load data from memory to an accumulator.

- Store data from an accumulator into memory.

All of the fixed point arithmetic instructions are shown in Table 2.6. Some of the instructions appear in both a short form and a long or extended form. (The prefix "E" indicates an extended instruction form.)

Short form instructions (sixteen bits) directly specify either a memory address from 0 to  $377_8$ , or a small area in memory surrounding the present value of the program counter or an accumulator. Long form instructions, thirty-two bits long, directly specify any address from 0 to  $77777_8$ .

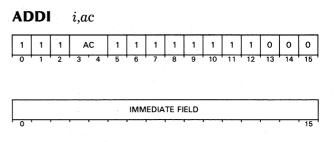

**ADI** and **ADDI** are short and long forms of the same instruction. The short form adds a 2-bit immediate in the range of 1-4, while the long form adds a 16-bit immediate in the range of -32,768 to +32,767.

Figure 2.4 Integer format

|          | Single<br>Precision   | Double<br>Precision                 |

|----------|-----------------------|-------------------------------------|

| Unsigned | 0 to 65,535           | 0 to 4,294,967,295                  |

| Signed   | -32,768 to<br>+32,767 | -2,147,483,648 to<br>+2,147,483,647 |

Table 2.5 Integer ranges

| Mnem         | Instructions                                                                                                          | Action                                                                                                                           |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ADC          | Add Complement                                                                                                        | Adds the one's complement of the<br>contents of one accumulator to the<br>contents of another accumulator.                       |  |  |  |  |  |

| ADD          | Add                                                                                                                   | Adds contents of two accumulators.                                                                                               |  |  |  |  |  |

| ADDI         | DDI Extended Add Adds a signed integer in the range -32<br>Immediate to +32,767 to the contents of an<br>accumulator. |                                                                                                                                  |  |  |  |  |  |

| ADI          | Add Immediate                                                                                                         | Adds an unsigned integer in the range 1-4 to the contents of an accumulator.                                                     |  |  |  |  |  |

| DIV          | Unsigned Divide                                                                                                       | Divides the unsigned 32-bit integer in two<br>accumulators by the unsigned contents of<br>a third accumulator.                   |  |  |  |  |  |

| DIVS         | Signed Divide                                                                                                         | Divides the signed 32-bit integer in two accumulators by the signed contents of a third accumulator.                             |  |  |  |  |  |

| DIVX         | Sign Extend And<br>Divide                                                                                             | Extends the sign of one accumulator into a second accumulator and performs a<br><i>Signed Divide</i> on the result.              |  |  |  |  |  |

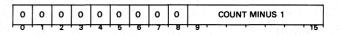

| DSZ<br>EDSZ  | Decrement And<br>Skip If Zero                                                                                         | Decrements the addressed word, then skips if the decremented value is zero.                                                      |  |  |  |  |  |

| HLV          | Halve                                                                                                                 | Divides the unsigned contents of an accumulator by 2.                                                                            |  |  |  |  |  |

| INC          | Increment Increments the contents of an accumulator.                                                                  |                                                                                                                                  |  |  |  |  |  |

| ISZ<br>EISZ  | Increment And<br>Skip If Zero                                                                                         | Increments the addressed word, then skips if the incremented value is zero.                                                      |  |  |  |  |  |

| LDA<br>ELDA  | Load<br>Accumulator                                                                                                   | Loads data from memory to an accumulator.                                                                                        |  |  |  |  |  |

| LEF<br>ELEF  | Load Effective<br>Address                                                                                             | Places an effective address in an accumulator.                                                                                   |  |  |  |  |  |

| MOV Move     |                                                                                                                       | Moves the contents of an accumulator through the Arithmetic Logic Unit (ALU).                                                    |  |  |  |  |  |

| MUL          | Unsigned<br>Multiply                                                                                                  | Multiplies the unsigned contents of two<br>accumulators and adds the results to the<br>unsigned contents of a third accumulator. |  |  |  |  |  |

| MULS         | Signed Multiply                                                                                                       | Multiplies the signed contents of two<br>accumulators and adds the results to the<br>signed contents of a third accumulator.     |  |  |  |  |  |

| NEG          | Negate                                                                                                                | Forms the two's complement of the contents of an accumulator.                                                                    |  |  |  |  |  |

| SBI          | Subtract<br>Immediate                                                                                                 | Subtracts an unsigned integer in the range 1-4 from the contents of an accumulator.                                              |  |  |  |  |  |

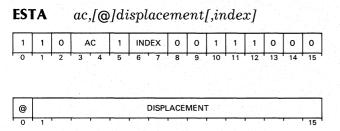

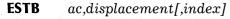

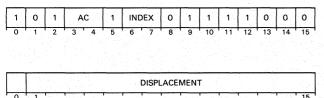

| STA,<br>ESTA | Store<br>Accumulator                                                                                                  | Stores data in memory from an accumulator.                                                                                       |  |  |  |  |  |

| SUB          | Subtract                                                                                                              | Subtracts contents of one accumulator from another.                                                                              |  |  |  |  |  |

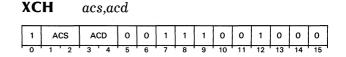

| хсн          | Exchange<br>Accumulators                                                                                              | Exchanges the contents of two accumulators.                                                                                      |  |  |  |  |  |

### **Decimal Arithmetic Instructions**

Unsigned decimal numbers are handled one decimal digit at a time. Each decimal digit is represented by bits 12-15 of a 16-bit word. Only the values  $0-9_{16}$  are used; carry is used for a decimal carry or borrow.

Two instructions in the ECLIPSE S/140 operate on decimal data. They are shown below, in Table 2.7.

| Mnem | em Instructions Action |                                                                                                                                 |  |  |  |

|------|------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DAD  | Decimal Add            | Adds together the decimal digits found in bits 12-15 of two accumulators.                                                       |  |  |  |

| DSB  | Decimal Subtract       | Subtracts the decimal digit in bits 12-15<br>of one accumulator from the decimal digit<br>in bits 12-15 of another accumulator. |  |  |  |

Table 2.7 Decimal arithmetic instructions

## **Logical Manipulation**

We represent logical entities as individual bits in a 16-bit word. Each bit is treated as a separate binary value. When an instruction operates on two words, only corresponding bits of each word interact. The following are examples of logical operations:

- Forming the logical AND of two words.

- Forming the logical complement of a word.

- Shifting the contents of a word left or right.

#### **Logical Operations Instructions**

All of the logical operations instructions are shown in Table 2.8.

The Load Effective Address and Extended Load Effective Address instructions are short and long forms of the same instruction. The sixteen bit short form directly specifies either a memory address from 0 to 255 or a small area in memory surrounding the present value of the program counter or an accumulator. The thirty-two bit long form directly specifies any address from 0 to  $77777_8$ .

Table 2.6 Fixed point arithmetic instructions

| Mnem        | Instructions                                                                                                                                      | ons Action                                                                                                                                             |  |  |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ANC         | AND With<br>Complemented<br>Source                                                                                                                | Forms the logical AND of the contents of<br>one accumulator and the logical<br>complement of the contents of another<br>accumulator.                   |  |  |  |  |  |

| AND         | AND                                                                                                                                               | Forms the logical AND of the contents of two accumulators.                                                                                             |  |  |  |  |  |

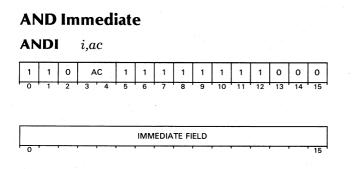

| ANDI        | AND Immediate                                                                                                                                     | Forms the logical AND of a 16-bit number<br>contained in the instruction and the<br>contents of an accumulator.                                        |  |  |  |  |  |

| СОМ         | Complement                                                                                                                                        | Forms the logical complement of the contents of an accumulator.                                                                                        |  |  |  |  |  |

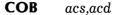

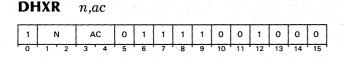

| DHXL        | Double Hex Shift<br>Left                                                                                                                          | Shifts the 32-bit contents of two<br>accumulators left 1 to 4 hex digits<br>depending on the value of a 2-bit number<br>contained in the instruction.  |  |  |  |  |  |

| DHXR        | Double Hex Shift<br>Right                                                                                                                         | Shifts the 32-bit contents of two<br>accumulators right 1 to 4 hex digits<br>depending on the value of a 2-bit number<br>contained in the instruction. |  |  |  |  |  |

| DLSH        | Double Logical Shifts the 32-bit contents of two accumulators left or right depending of the contents of a third accumulator.                     |                                                                                                                                                        |  |  |  |  |  |

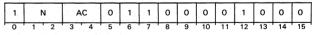

| HXL         | XL Hex Shift Left Shifts the contents of an accumulat<br>1 to 4 hex digits depending on the<br>of a 2-bit number contained in the<br>instruction. |                                                                                                                                                        |  |  |  |  |  |

| HXR         | Hex Shift Right                                                                                                                                   | Shifts the contents of an accumulator right<br>1 to 4 hex digits depending on the value<br>of a 2-bit number contained in the<br>instruction.          |  |  |  |  |  |

| IOR         | Inclusive OR                                                                                                                                      | Forms the logical inclusive OR of the contents of two accumulators.                                                                                    |  |  |  |  |  |

| IORI        | Inclusive OR<br>Immediate                                                                                                                         | Forms the logical inclusive OR of a 16-bit<br>number contained in the instruction and<br>the contents of an accumulator.                               |  |  |  |  |  |

| LEF<br>ELEF | Load Effective<br>Address                                                                                                                         | Places an effective address in an accumulator.                                                                                                         |  |  |  |  |  |

| LSH         | Logical Shift                                                                                                                                     | Shifts the contents of an accumulator left<br>or right depending on the contents of<br>another accumulator.                                            |  |  |  |  |  |

| XOR         | Exclusive OR                                                                                                                                      | Forms the logical exclusive OR of the<br>contents of two accumulators.                                                                                 |  |  |  |  |  |

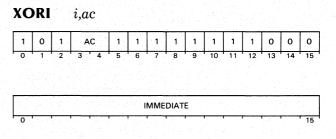

| XORI        | Exclusive OR<br>Immediate                                                                                                                         | Forms the logical exclusive OR of a 16-bi<br>number contained in the instruction and<br>the contents of an accumulator.                                |  |  |  |  |  |

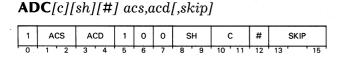

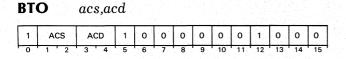

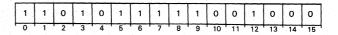

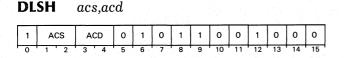

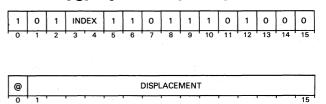

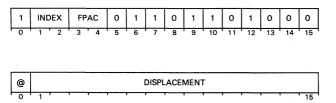

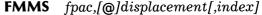

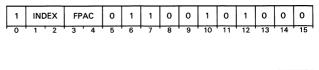

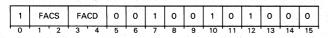

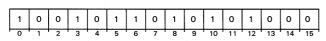

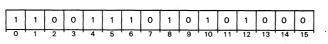

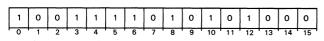

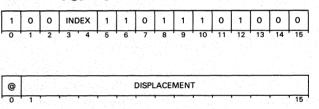

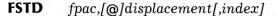

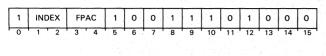

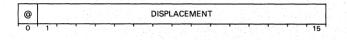

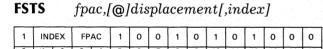

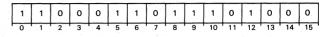

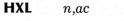

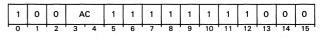

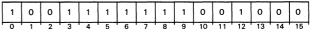

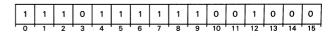

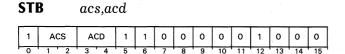

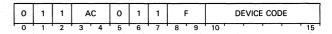

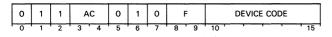

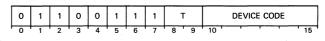

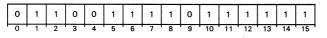

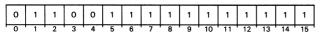

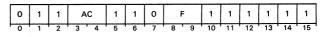

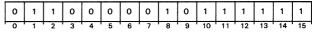

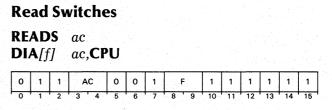

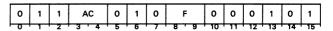

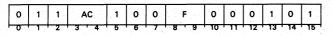

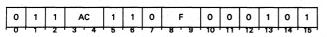

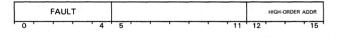

include shift operations, which rotate the data left or right, or swap the bytes. Also included are various tests that can be performed on the data. With each test the instructions can check the data for some condition and skip or not skip the next sequential word, depending on the outcome of the test. Finally, the instructions can load or not load the results of the specific and general functions into the destination accumulator and carry. The diagram below shows the format of the ALC instructions.

| ſ | 1 | A  | cs | A | CD | OP |     | SH |   | С  |    | #  | S  | KIP |

|---|---|----|----|---|----|----|-----|----|---|----|----|----|----|-----|

|   | 0 | 1. | 2  | 3 | 4  | 5  | ' 7 | 8  | 9 | 10 | 11 | 12 | 13 | 15  |

## **ALC Instructions**

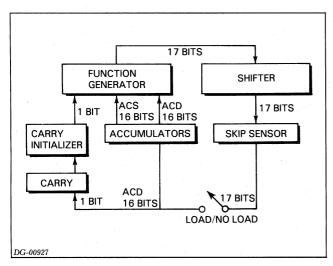

The ALC instructions are listed in Table 2.9. These instructions use an Arithmetic Logic Unit (ALU) to process data. The logical organization of the ALU is illustrated in Figure 2.5.

| Mnem | nem Instructions Action                                                      |                                                                     |  |  |  |  |

|------|------------------------------------------------------------------------------|---------------------------------------------------------------------|--|--|--|--|

| ADC  | Add Complement Adds an unsigned integer to the complement of another unsigne |                                                                     |  |  |  |  |

| ADD  | Add                                                                          | Adds contents of one accumulator to the contents of another.        |  |  |  |  |

| AND  | AND                                                                          | Forms the logical AND of the contents of two accumulators.          |  |  |  |  |

| СОМ  | Complement                                                                   | Forms the logical complement of the contents of an accumulator.     |  |  |  |  |

| INC  | Increment                                                                    | Increments the contents of an accumulator.                          |  |  |  |  |

| MOV  | Move                                                                         | Moves the contents of an accumulator through the ALU.               |  |  |  |  |

| NEG  | Negate                                                                       | Forms the two's complement of the contents of an accumulator.       |  |  |  |  |

| SUB  | Subtract                                                                     | Subtracts contents of one accumulator from the contents of another. |  |  |  |  |

Table 2.9 Arithmetic/logic class instructions

Table 2.8 Logical operations instructions

## **ALC Manipulation**

Each of the eight Arithmetic/Logic Class (ALC) instructions performs a specific function upon the contents of one or two accumulators and carry. The eight functions are Add, Subtract, Negate, Add Complement, Move, AND, Complement, and Increment. The instructions are identified by the mnemonics of the eight functions, which are ADD, SUB, NEG, ADC, MOV, AND, COM, and INC.

In addition to the specific functions performed by an individual instruction, there is a group of general functions all ALC instructions can perform. These general functions

e a

Figure 2.5 Logical organization of the ALU

When an ALC instruction begins execution, it loads the contents of carry and the contents of the accumulator(s) to be processed into the ALU. There are five distinct stages of ALU operation: carry, function, shift operations, skip tests, and load/no-load. We will discuss these stages separately.

#### Carry

The ALU begins its manipulation of the data by determining a new value for carry. This new value is based upon three things: the old value of carry, bits 10-11 of the ALC instruction, and the ALC instruction being executed. The ALU first determines the effect of the instruction bits 10-11 on the old value of carry. Table 2.10 shows each of the mnemonics that can be appended to the instruction mnemonic, the value of bits 10-11 for each choice, and the action each one takes.

| Symbols                                                  | Value | Operation                 |

|----------------------------------------------------------|-------|---------------------------|

| [c] omitted                                              | 00    | Leave carry<br>unchanged. |

| [c]= <b>Z</b>                                            | 01    | Initialize carry to 0.    |

| $[c] = \mathbf{Z}$ $[c] = \mathbf{O}$ $[c] = \mathbf{C}$ | 10    | Initialize carry to 1.    |

| [c]= <b>C</b>                                            | 11    | Complement carry.         |

Table 2.10 Selecting the value of carry

#### Function

The ALU next evaluates the effect of the specific function (bits 5-7) upon the data. For the instructions *Move*, *AND*, and *Complement* the ALU performs the function on the data word(s) and saves the result. The value of carry is as it was calculated above. For the instructions *Add*, *Add Complement*, *Subtract*, *Negate*, and *Increment* the result of the function's action upon the data word(s) may be larger than  $2^{16}$  - 1. An overflow results. In this situation, the ALU saves the low-order 16 bits of the function result, but it complements the value of carry calculated above.

#### **Data General Corporation**

**NOTE:** At this stage of operation, the ALU does not load either the saved value of the function result into the destination accumulator, or the calculated value of carry into carry.

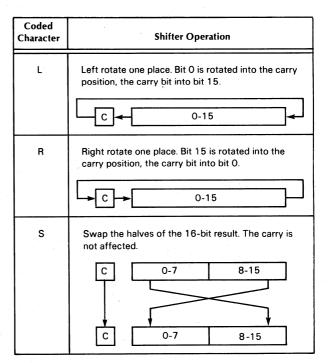

#### **Shift Operations**

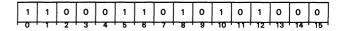

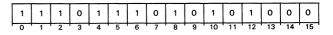

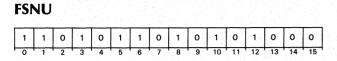

Next the ALU performs any specified shift operation on the 17 bits output from the function generator (16 bits of data plus the calculated value of the carry bit). Depending on which shift operation is specified in the instruction, the function generator output can be rotated left or right one bit, or have its bytes swapped. Table 2.11 shows the different shift operations that can be performed, the value of bits 8-9 for each choice, and the action each choice takes. Figure 2.6 shows how each shift operation works.

| Symbols        | Value | Operation                                                                          |

|----------------|-------|------------------------------------------------------------------------------------|

| [sh] omitted   | 00    | Do not shift the result of the ALC operation.                                      |

| [sh]=L         | 01    | Rotate left the 17-bit<br>combination of carry bit and ALC<br>operation result.    |

| [sh]= <b>R</b> | 10    | Rotate right the 17-bit<br>combination of carry bit and ALC<br>operation result.   |

| [sh]= <b>S</b> | 11    | Swap the two 8-bit halves of the ALC operation result without affecting carry bit. |

Table 2.11 Selecting the shift operation

Figure 2.6 Effects of shift operations

#### Skip Tests

The ALU can test the result of the shift operation for one of a variety of conditions, and skip or not skip the next instruction depending upon the result of the test. Table 2.12 shows the tests that can be performed, the value of bits 13-15 for each choice, and the action each choice takes.

| Symbol             | Value | Operation                                          |

|--------------------|-------|----------------------------------------------------|

| [skip] omitted     | 000   | No skip.                                           |

| [skip]=SKP         | 001   | Skip unconditionally.                              |

| [skip]= <b>SZC</b> | 010   | Skip if carry bit is zero.                         |

| [skip]=SNC         | 011   | Skip if carry bit is nonzero.                      |

| [skip]=SZR         | 100   | Skip if ALC result is zero.                        |

| [skip]=SNR         | 101   | Skip if ALC result is nonzero.                     |

| [skip]=SEZ         | 110   | Skip if either ALC result or carry bit is zero.    |

| [skip]=SBN         | 111   | Skip if both ALC result and carry bit are nonzero. |

Table 2.12 Selecting skip tests

#### Load/No-Load

If the no-load bit (bit 12) is 0, the ALU loads the result of the shift operation into the destination accumulator, and loads the new value of carry into carry. If the no-load bit is 1, then the ALU does not load the result of the shift operation into the destination accumulator, and does not load the new value of carry into carry, but all other operations, such as skip tests, take place. This no-load option is particularly convenient to use when you want to test for some condition without destroying the contents of the destination accumulator. Table 2.13 shows how to code the load/no-load operation.

| Symbol    | Value | Operation                                                                                               |

|-----------|-------|---------------------------------------------------------------------------------------------------------|

| # omitted | 0     | Load the result of the shift operation into ACD.                                                        |

| #         | 1     | Do not load the ALC operation result<br>into ACD; restore carry bit to value it<br>had before shifting. |

Table 2.13 Codes for the load/no load option

**NOTE:** These instructions must not have both the No-Load and the Never-Skip options specified at the same time. This bit combination is used to specify other non-ALC instructions.

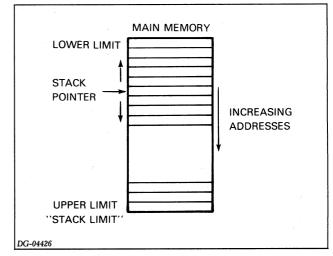

## The Stack

The stack is a series of consecutive locations in memory. In their simplest form, stack instructions add items in sequential order to the top of the stack and retrieve them in the reverse order. Several stack areas may be defined by the program, but only one stack may be in use at any time. The ECLIPSE S/140 uses the push-down stack concept to provide easily accessible temporary storage of data, variables, return addresses, and the like.

The simplest use of the stack is for temporary storage of the contents of up to four accumulators, which can be stored or retrieved with one instruction. More commonly, the stack is used to store a *return block* which greatly simplifies the process of entering and returning from subroutines.

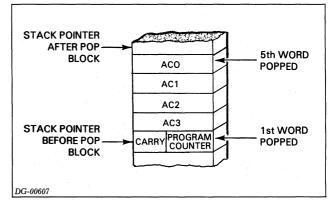

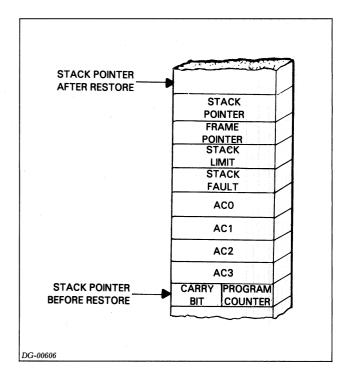

The return block can take several forms, but it usually consists of five words: the contents of the four accumulators in the first four words, and the program counter and carry in the last word pushed.

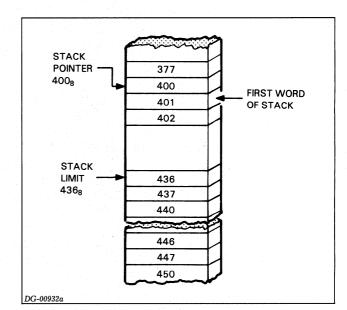

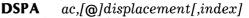

Three parameters define a stack: (1) the lower limit, or starting location; (2) the upper limit, or stack limit; and (3) the present top of the stack, or stack pointer. The lower and upper limits define the area in memory which is reserved for the stack, and the stack pointer defines the location of the last word placed onto the stack (or the next word available from the stack). A diagram of a stack area is shown in Figure 2.7.

Figure 2.7 The stack area

To use the stack, define the upper and lower limits, then use the stack instructions to put items on (*push onto*) or remove items from (*pop off*) the top of the stack. It is not necessary to keep track of the location of the top of the stack. This is done automatically by one of the stack control words (stack pointer).

#### **Stack Control Words**

The stack control words are:

- Stack pointer

- Frame pointer

- Stack limit

- Stack fault address

The locations and uses of the stack control words are discussed in detail below.

#### **Stack Pointer**

The stack pointer contains the address of the current top of the stack. As you do push or pop operations, the value of the stack pointer changes so that it always points to the top word of the stack. A push operation increments the stack pointer contents by one, then stores the word you want to push in the new location specified by the stack pointer. A pop operation takes the contents of the word addressed by the stack pointer and loads them into a register, then decrements the stack pointer value by 1.

When you set up the stack, you usually set the value of the stack pointer to be one less than the address of the first stack word.

Location  $40_8$  contains the current value of the stack pointer.

#### **Frame Pointer**

Unlike the stack pointer, the frame pointer does not change its value when push and pop operations occur. If you set the frame pointer to contain the original value of the stack pointer, you have a useful reference to the first stack location.

The *Save* and *Return* instructions use the frame pointer to save the value of the stack pointer when entering or exiting subroutines. Since the frame pointer remains unchanged, it allows you to call a subroutine, perform some operation, then return to the calling program without destroying the value of the stack pointer. This means you can restore the original state of the calling program when you return from the subroutine call.

Location  $41_8$  contains the value of the frame pointer.

#### **Stack Limit**

The stack limit contains the upper limit of the stack area. Each push operation compares the stack pointer with the stack limit to check if there is space enough to allow the push. If the stack pointer is greater than the stack limit, then you have exceeded the size of the stack (overflow condition). For more information, see the next section on "Stack Protection."

Location  $42_8$  contains the value of the stack limit.

#### **Stack Fault Address**

If you cause an overflow or underflow, control transfers to the stack fault routine. For more information, see the next section on "Stack Protection."

Location  $43_8$  contains the (possibly indirect) address of the stack fault routine.

#### **Stack Protection**

You can enable protection for two stack error conditions: *overflow* and *underflow*.

**Stack overflow** occurs when a program pushes data into the area beyond that allocated for the stack, i.e., beyond the stack limit. If this occurs, data may be pushed into areas which are reserved for other purposes, possibly overwriting other data or instructions.

Overflow protection is provided by the stack limit. If a stack instruction pushes data onto the stack beyond the stack limit, a return block is pushed onto the stack, and control is transferred to the stack fault handler. To disable overflow protection, the stack limit should be set to  $177777_8$ .

To be meaningful, the stack limit must be 10 to 23 addresses lower than the last word you reserve for the stack, because stack overflow is detected only at the end of a push operation (except in the case of the *Save* and the *Modify Stack Pointer* instructions - see details in Chapter 4). Thus, it is possible to push a 5- to 18-word return block starting at the stack limit. Stack overflow will not be sensed until the last word of the return block is pushed. After the last word is pushed, stack overflow will be detected, and another 5-word return block will be pushed by the stack overflow mechanism before control is transferred to the stack fault routine. Depending on the size of the initial return block (from the normal 5 words up to the 18 words used by the floating point instruction set), the potential overflow can be 10 to 23 words long.

**Stack underflow** occurs when a program pops data from the area below that allocated for the stack (i.e., pops more words off than were pushed on). If this occurs, the program will be operating with incorrect and unpredictable information. Furthermore, it is possible that the program will push data into the underflow area, overwriting data or instructions.

For underflow protection to be enabled, the area allocated to the stack must begin at location  $401_8$  and the stack pointer must be initialized to  $400_8$ . If the stack pointer is less than  $400_8$  after a pop operation, an underflow condition exists and a stack fault occurs.

Underflow protection can be disabled in two ways:

- Start the stack at a location greater than  $401_8$ . A stack fault will not occur then unless the program underflows the stack and then continues to pop words off the stack until the stack pointer is less than  $400_8$ . Note that this does not completely disable underflow protection it is always possible to pop enough words off the stack to underflow it.

- Set bit 0 of both the stack pointer and the stack limit to 1. If this is done, all or a portion of the stack may reside in page zero (locations  $0-377_8$ ), or the stack may

underflow into page zero, without interference from the stack underflow mechanism.

#### **Stack Overflow Protection**

The *Save* and the *Modify Stack Pointer* instructions check for overflow before executing. For every other instruction that pushes data onto the stack, a check is made for overflow after the execution of the instruction. In both cases, the stack pointer and stack limit are treated as unsigned 16-bit integers and compared. If overflow has occurred, the processor:

- Sets bit 0 of the stack pointer to 0.

- Sets bit 0 of the stack limit to 1.

- Pushes a return block onto the stack.

- Executes a jump indirect to the stack fault address.

Bit 0 of the stack pointer and stack limit are set as indicated so that the stack limit will (temporarily) be larger than the stack pointer. In this way, the return block pushed by the overflow mechanism itself will not be interpreted as yet another overflow fault, causing a loop condition. The program counter in the return block points to the instruction immediately following the stack instruction that caused the fault.

#### **Stack Underflow Protection**

After every operation that pops data off the stack, a check is made for underflow. If the stack pointer is less than  $400_8$ , and bit 0 of the stack limit is 0, a stack underflow condition exists. In that case, the processor:

- Sets the stack pointer equal to the stack limit.

- Sets bit 0 of the stack pointer to 0.

- Sets bit 0 of the stack limit to 1.

- Pushes a return block onto the stack.

- Executes a jump indirect to the stack fault address.

Bit 0 of the stack pointer and stack limit are set as indicated so that the stack limit will (temporarily) be larger than the stack pointer. In this way, the return block being pushed onto the stack by the underflow mechanism (starting at the stack limit) will not cause an overflow fault. The program counter in the return block points to the instruction immediately following the stack instruction that caused the fault.

#### **Stack Fault Handler**

The stack fault handler (created by the programmer) determines the nature of the fault. It also resets the appropriate values, and takes any other appropriate action, such as allocating more stack space or terminating the program. Note that the stack fault handler must reset bit 0 of the stack pointer and stack limit to their original values.

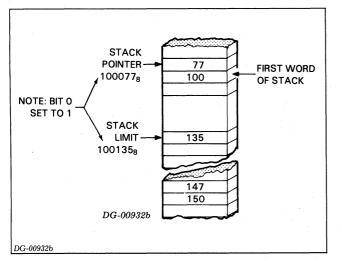

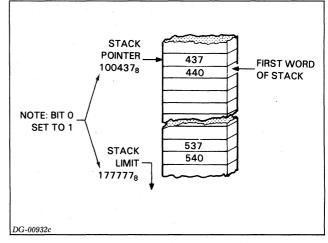

#### **Initializing the Stack Control Words**

Initialize the stack control words before performing the first operation on the stack. The initialization rules are discussed below, while Figures 2.8 through 2.10 illustrate protected and unprotected stack areas. Figure 2.8 shows a stack area of  $50_8$  words with underflow protection; Figure 2.9 shows a stack area of  $50_8$  words in page zero with overflow protection; and Figure 2.10 shows a stack area of  $100_8$  words with no protection.

Initialize the stack pointer to the beginning address of the stack minus one. If you wish stack underflow protection, initialize the stack pointer to  $400_8$  and start the stack at  $401_8$ . Otherwise, start the stack at a location greater than  $401_8$ . To place all or a portion of the stack in page zero, or to disable underflow protection, set bit 0 of the stack pointer and the stack limit to 1.

Initialize the stack limit to a value greater than the stack pointer. If you wish stack overflow protection, initialize the stack limit to the last allocated stack address minus at least  $10_{10}$ . Otherwise, initialize the stack limit to  $77777_8$ . To place all or a portion of the stack in page zero, set bit 0 of the stack pointer and the stack limit to 1.

*Initialize the stack fault address* to an address (determined by the programmer) that contains the routine to handle stack overflow or underflow. Bit 0 may be set to 1 to indicate an indirect address.

The frame pointer will have no meaning until the first use of the *Save* instruction.

Figure 2.8 Underflow protected stack area

Figure 2.9 Overflow protected page zero stack area

Figure 2.10 Unprotected stack area

## **Stack Instructions**

The instructions that control use of the stack are listed in Table 2.14.

| Mnem | Instructions                             | Action                                                                                                                                                               |

|------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

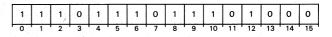

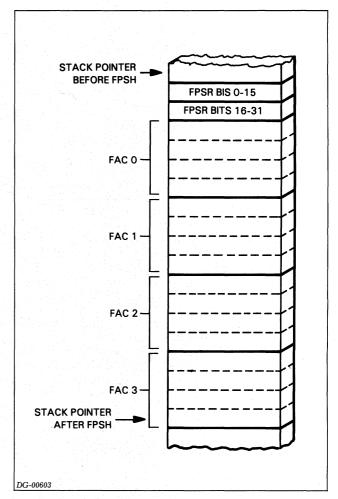

| FPOP | Pop Floating<br>Point State              | Pops an 18-word floating point return block off the stack.                                                                                                           |

| FPSH | Push Floating<br>Point State             | Pushes an 18-word floating point return block onto the stack.                                                                                                        |

| MSP  | Modify Stack<br>Pointer                  | Changes the value of the stack pointer and checks for overflow.                                                                                                      |

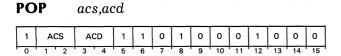

| POP  | Pop Multiple<br>Accumulators             | Pops 1 to 4 words off the stack and places them in the indicated accumulators.                                                                                       |

| POPB | Pop Block                                | Returns control from a <i>System Call</i><br>routine or an I/O interrupt handler that<br>does not use the stack change facility of<br>the <i>Vector</i> instruction. |

| POPJ | Pop PC And Jump                          | Pops the top word off the stack and places it in the program counter.                                                                                                |

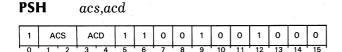

| PSH  | Push Multiple<br>Accumulators            | Pushes the contents of 1 to 4 accumulators on the stack.                                                                                                             |

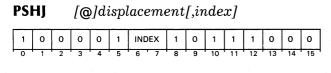

| PSHJ | Push Jump                                | Pushes the address of the next sequential<br>instruction on the stack and places an<br>effective address into the program counter.                                   |

| PSHR | Push Return<br>Address                   | Pushes the address of the PC, plus 2, onto the stack.                                                                                                                |

| RSTR | Restore                                  | Returns control from certain types of I/O interrupts.                                                                                                                |

| RTN  | Return                                   | Returns control from subroutines that issue a $Save$ instruction at their entry points.                                                                              |

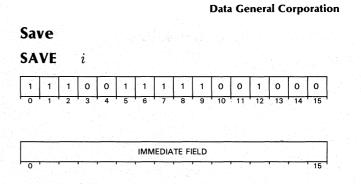

| SAVE | Save                                     | Saves the information required by the <i>Return</i> instruction.                                                                                                     |

| SYC  | System Call                              | Pushes a return block and indirectly places the address of the $System\ Call$ handler in the program counter.                                                        |

| VCT  | Vector on<br>Interrupting<br>Device Code | Performs various interrupt functions. See the I/O section in this chapter.                                                                                           |

## **Reserved Storage Locations**

The following are reserved storage locations in the ECLIPSE S/140. The CPU uses them for specific functions; you should not use them during normal operations.

The addresses, names, and functions of these locations are given below. The notation *indirectable* means that bit 0 may be set to indicate that this is an indirect address.

The locations shown in Table 2.15 are in unmapped logical address space.

| Loc | Name                   | Function                                                                            |

|-----|------------------------|-------------------------------------------------------------------------------------|

| 0   | I/O RETURN<br>ADDRESS  | Return address from I/O<br>interrupt; first instruction of<br>Auto-restart routine. |

| 1   | I/O HANDLER<br>ADDRESS | Address of the I/O interrupt handler (indirectable).                                |

| 2   | SC HANDLER<br>ADDRESS  | Address of the <i>System Call</i><br>instruction handler<br>(indirectable).         |

| 3   | PF HANDLER<br>ADDRESS  | Address of the protection fault handler (indirectable).                             |

Table 2.15 Reserved locations in unmapped logical address space

Table 2.14 Stack instructions

The locations shown in Table 2.16 may be in unmapped logical address space or in Map A or Map B logical address space. They are used by the **VCT** instruction.

| Loc | Name                             | Function                                                                                   |

|-----|----------------------------------|--------------------------------------------------------------------------------------------|

| 4   | VECTOR STACK<br>POINTER          | Address of the start of the vector stack (not indirectable).                               |

| 5   | CURRENT<br>MASK                  | Current interrupt priority mask.                                                           |

| 6   | VECTOR STACK<br>LIMIT            | Address of the last normally<br>usable location in the vector<br>stack (not indirectable). |

| 7   | VECTOR STACK<br>FAULT<br>ADDRESS | Address of the vector stack faul<br>handler (indirectable).                                |

Table 2.16 Reserved locations used by the Vector instruction

The locations shown in Table 2.17 are in the same address space as the instructions using them.

| Loc    | Name                               | Function                                                                      |

|--------|------------------------------------|-------------------------------------------------------------------------------|

| 20-27  | AUTO-INCO<br>through<br>AUTO-INC7  | Auto-incrementing locations.                                                  |

| 30-37  | AUTO-DECO<br>through<br>AUTO-DEC7  | Auto-decrementing locations.                                                  |

| 40     | STACK<br>POINTER                   | Address of the top of the stack (not indirectable).                           |

| 41     | FRAME<br>POINTER                   | Address of the frame reference within the stack (not indirectable).           |

| 42     | STACK LIMIT                        | Address of the last normally usable location in the stack (not indirectable). |

| 43     | STACK FAULT<br>ADDRESS             | Address of the stack fault handler (indirectable).                            |

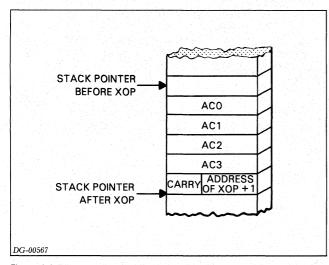

| 44     | XOP ORIGIN<br>ADDRESS              | Address of the start of XOP (not indirectable).                               |

| 45     | FLOATING<br>POINT FAULT<br>ADDRESS | Address of the floating point fault handler (indirectable).                   |

| 46- 47 |                                    | Reserved for future use.                                                      |

Table 2.17 Reserved locations in the same address space as the instructions using them

#### **Program Execution**

A 15-bit register called the *program counter* always contains the address of the instruction currently being executed. During *sequential operation*, the program counter is incremented by one after each instruction. It can normally address the complete logical address space, i.e., 0 through  $77777_8$ , inclusive, a total of 32,768 word locations. The address after  $77777_8$  is 0, and no indication is given when the counter rolls from  $77777_8$  to 0 in the course of sequential processing.

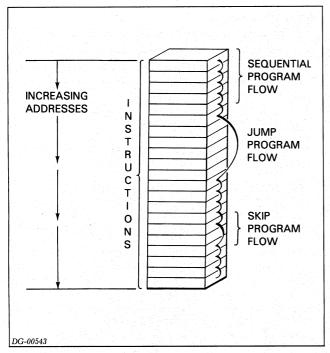

#### **Program Flow Alteration**

You can alter the program flow from sequential operation in two ways. Jump instructions alter the program flow by inserting a new value into the program counter. Conditional skip instruction alter the program flow by incrementing the program counter an extra time if a specified test condition is true. In either case, sequential operation continues with the instruction addressed by the updated value of the program counter. Figure 2.11 illustrates the effects of these instructions.

**NOTE:** Do not use a conditional skip immediately before a 2-word instruction. The conditional instruction causes a 1-word skip, which results in an attempt to execute the second word of the instruction as a 1-word instruction.

Figure 2.11 Program flow alteration

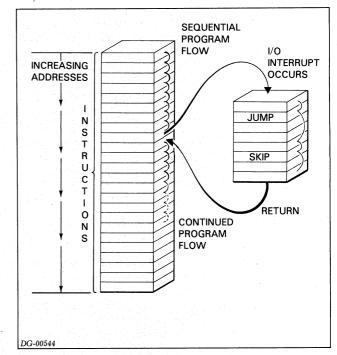

### **Program Flow Interruption**

The normal flow of a program may be interrupted by external or exceptional internal conditions, such as I/O interrupts or MMPU faults. When this occurs, the contents of the program counter are saved, so that after the interrupt is serviced, control will return to the right place. The address of the starting instruction for the proper fault or interrupt handler is then placed in the program counter and sequential operation continues within that program. When the fault or interrupt handler has serviced the interrupt, control is returned to the interrupted program at the saved address. Figure 2.12 is a diagram of the effect of an interrupt on normal program flow.

Figure 2.12 Program flow interruption

#### **Program Flow Alteration Instructions**

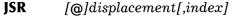

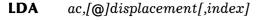

Program flow alteration and conditional instructions are shown in Tables 2.18 through 2.21. In Table 2.18, several instructions have both short and long forms. The sixteen bit short form directly specifies either a memory address from 0 to 255 or a small area in memory surrrounding the present value of the program counter or an accumulator. The thirty-two bit long form directly specifies any address from 0 to 777778.

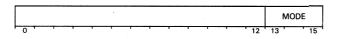

Table 2.19 summarizes the skip instructions that test condition codes in the floating point status register. Table 2.20 summarizes the condition tests available for the **SKP** [t] instruction. (This instruction tests the condition codes of a peripheral device, the power-fail monitor or the interrupt system.) And Table 2.21 summarizes the *skip* options of the ALC instructions.

| Mnem              | Instructions                                   | Action                                                                                                                                                                                                                                             |

|-------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLM               | Compare To<br>Limits                           | Compares a signed integer with two other<br>numbers and skips if first integer is<br>between the other two.                                                                                                                                        |

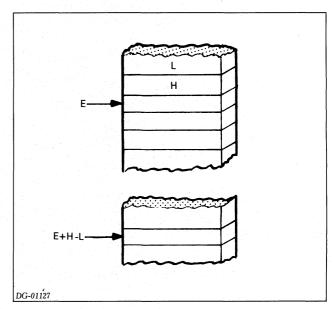

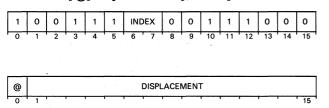

| DSPA              | Dispatch                                       | Compares a signed integer with two other<br>numbers and continues sequential<br>execution if the integer is not between the<br>others; otherwise, uses the integer as an<br>index into a table and places indexed value<br>in the program counter. |

| DSZ<br>EDSZ       | Decrement And<br>Skip If Zero                  | Decrements the addressed word, then skips if the decremented value is zero.                                                                                                                                                                        |

| ISZ<br>EISZ       | Increment And<br>Skip If Zero                  | Increments the addressed word, then skips<br>if the incremented value is zero.                                                                                                                                                                     |

| JMP<br>EJMP       | Jump                                           | Places an effective address in the program<br>counter.                                                                                                                                                                                             |

| JSR<br>EJSR       | Jump To<br>Subroutine                          | Increments program counter and stores<br>incremented value in AC3; then places a<br>new address in the program counter.                                                                                                                            |

| POPB              | Pop Block                                      | Pops a return block off of the stack.                                                                                                                                                                                                              |

| POPJ              | Pop PC And Jump                                | Pops the top word off the stack and places it in the program counter.                                                                                                                                                                              |

| PSHJ              | Push                                           | Pushes the address of the next sequential<br>instruction onto the stack and places a<br>new address in the program counter.                                                                                                                        |

| RSTR              | Restore                                        | Returns control from I/O interrupt handlers that use the stack change facility of the <b>VCT</b> instruction.                                                                                                                                      |

| RTN               | Return                                         | Returns control from a subroutine entered via <i>Save</i> instruction.                                                                                                                                                                             |

| SGE               | Skip If ACS<br>Greater Than Or<br>Equal To ACD | Compares two signed integers in two<br>accumulators and skips if the first is greater<br>than or equal to the second.                                                                                                                              |

| SGT               | Skip If ACS<br>Greater Than<br>ACD             | Compares two signed integers in<br>accumulators; skips if first is greater than<br>the second.                                                                                                                                                     |