# RISC-V Specification for CHERI Extensions

Authors: Hesham Almatary, Andres Amaya Garcia, John Baldwin, David Chisnall, Jessica Clarke, Brooks Davis, Nathaniel Wesley Filardo, Franz A. Fuchs, Timothy Hutt, Alexandre Joannou, Tariq Kurd, Ben Laurie, A. Theodore Markettos, David McKay, Jamie Melling, Stuart Menefy, Simon W. Moore, Peter G. Neumann, Robert Norton, Alexander Richardson, Michael Roe, Peter Rugg, Peter Sewell, Carl Shaw, Robert N. M. Watson, Jonathan Woodruff

Version v0.0.1-prerelease, 2024-01-20: Draft

# Table of Contents

|                                                                                  |    |

|----------------------------------------------------------------------------------|----|

| Preamble .....                                                                   | 1  |

| Copyright and license information .....                                          | 2  |

| Contributors .....                                                               | 3  |

| 1. Introduction .....                                                            | 4  |

| 1.1. CHERI Concepts and Terminology .....                                        | 4  |

| 1.2. CHERI Extensions to RISC-V .....                                            | 5  |

| 1.3. Risks and Known Uncertainty .....                                           | 6  |

| 1.3.1. Pending Extensions .....                                                  | 6  |

| 1.3.2. Incompatible Extensions .....                                             | 6  |

| 1.3.3. Suggested Mnemonic Renaming .....                                         | 6  |

| 2. Anatomy of Capabilities in Zcheri_purecap .....                               | 8  |

| 2.1. Components of a Capability .....                                            | 8  |

| 2.1.1. Tag .....                                                                 | 8  |

| 2.1.2. Architectural Permissions (AP) .....                                      | 8  |

| Permission Encoding .....                                                        | 9  |

| 2.1.3. Software-Defined Permissions (SDP) .....                                  | 10 |

| 2.1.4. Sealed (S) Bit .....                                                      | 10 |

| 2.1.5. Bounds .....                                                              | 11 |

| 2.1.6. Address .....                                                             | 12 |

| 2.1.7. Reserved Bits .....                                                       | 12 |

| 2.2. Capability Encoding .....                                                   | 12 |

| 2.3. NULL and Infinite Capabilities .....                                        | 15 |

| 2.4. Representable Limit Check .....                                             | 15 |

| 2.5. Malformed Capability Bounds .....                                           | 16 |

| 3. Integrating Zcheri_purecap with the RISC-V Base Integer Instruction Set ..... | 17 |

| 3.1. Memory .....                                                                | 17 |

| 3.2. Programmer's Model for Zcheri_purecap .....                                 | 17 |

| 3.3. Capability Instructions .....                                               | 18 |

| 3.3.1. Capability Inspection Instructions .....                                  | 18 |

| 3.3.2. Capability Manipulation Instructions .....                                | 18 |

| 3.3.3. Capability Load and Store Instructions .....                              | 19 |

| 3.3.4. Unconditional Integer Address Jumps .....                                 | 20 |

| 3.4. Existing RISC-V Instructions .....                                          | 20 |

| 3.4.1. Integer Computational Instructions .....                                  | 20 |

| 3.4.2. Control Transfer Instructions .....                                       | 20 |

| Unconditional Jumps .....                                                        | 20 |

| Conditional Branches .....                                                       | 21 |

| 3.4.3. Integer Load and Store Instructions .....                                 | 21 |

| 3.5. Zicsr, Control and Status Register (CSR) Instructions .....                 | 21 |

| 3.5.1. CSR Instructions .....                                                    | 22 |

|                                                                                   |    |

|-----------------------------------------------------------------------------------|----|

| 3.6. Control and Status Registers (CSRs) . . . . .                                | 22 |

| 3.7. Machine-Level CSRs . . . . .                                                 | 23 |

| 3.7.1. Machine ISA Register (misa) . . . . .                                      | 23 |

| 3.7.2. Machine Status Registers (mstatus and mstatush) . . . . .                  | 24 |

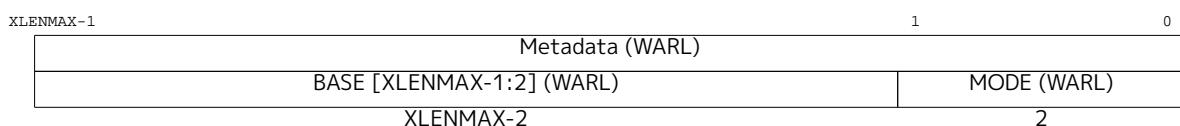

| 3.7.3. Machine Trap-Vector Base-Address Registers (mtvec) . . . . .               | 24 |

| 3.7.4. Machine Trap-Vector Base-Address Capability Registers (mtvec) . . . . .    | 24 |

| 3.7.5. Machine Scratch Register (mscratch) . . . . .                              | 25 |

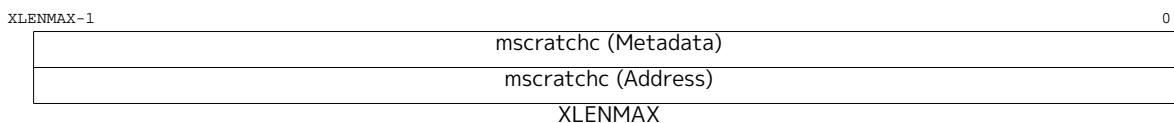

| 3.7.6. Machine Scratch Register Capability (mscratchc) . . . . .                  | 25 |

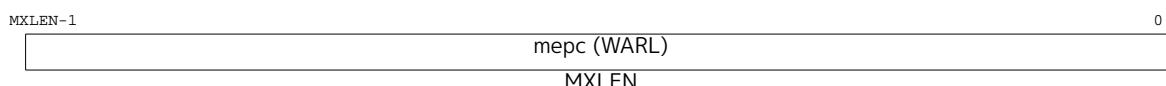

| 3.7.7. Machine Exception Program Counter (mepc) . . . . .                         | 25 |

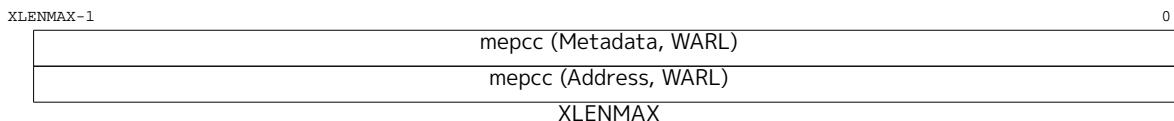

| 3.7.8. Machine Exception Program Counter Capability (mepcc) . . . . .             | 26 |

| 3.7.9. Machine Cause Register (mcause) . . . . .                                  | 26 |

| 3.7.10. Machine Trap Delegation Register (medeleg) . . . . .                      | 27 |

| 3.7.11. Machine Trap Value Register (mtval) . . . . .                             | 27 |

| 3.8. Supervisor-Level CSRs . . . . .                                              | 28 |

| 3.8.1. Supervisor Trap Vector Base Address Registers (stvec) . . . . .            | 28 |

| 3.8.2. Supervisor Trap Vector Base Address Registers (stvec) . . . . .            | 28 |

| 3.8.3. Supervisor Scratch Register (sscratch) . . . . .                           | 29 |

| 3.8.4. Supervisor Scratch Registers (sscratchc) . . . . .                         | 29 |

| 3.8.5. Supervisor Exception Program Counter (sepc) . . . . .                      | 29 |

| 3.8.6. Supervisor Exception Program Counter Capability (sepcc) . . . . .          | 29 |

| 3.8.7. Supervisor Cause Register (scause) . . . . .                               | 30 |

| 3.8.8. Supervisor Trap Value Register (stval) . . . . .                           | 30 |

| 3.9. Unprivileged CSRs . . . . .                                                  | 31 |

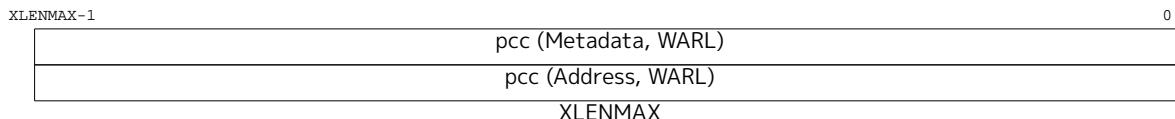

| 3.9.1. Program Counter Capability (pcc) . . . . .                                 | 31 |

| 3.10. CHERI Exception handling . . . . .                                          | 31 |

| 3.11. Physical Memory Attributes (PMA) . . . . .                                  | 32 |

| 3.12. Page-Based Virtual-Memory Systems . . . . .                                 | 32 |

| 3.12.1. Invalid Address Handling . . . . .                                        | 33 |

| 4. Integrating Zcheri_purecap with Sdext . . . . .                                | 34 |

| 4.1. Debug Mode . . . . .                                                         | 34 |

| 4.2. Core Debug Registers . . . . .                                               | 34 |

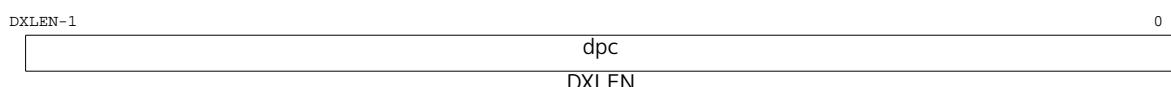

| 4.2.1. Debug Program Counter (dpc) . . . . .                                      | 34 |

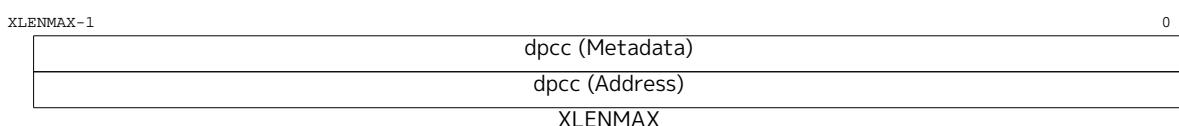

| 4.2.2. Debug Program Counter Capability (dpcc) . . . . .                          | 34 |

| 4.2.3. Debug Scratch Register 0 (dscratch0) . . . . .                             | 35 |

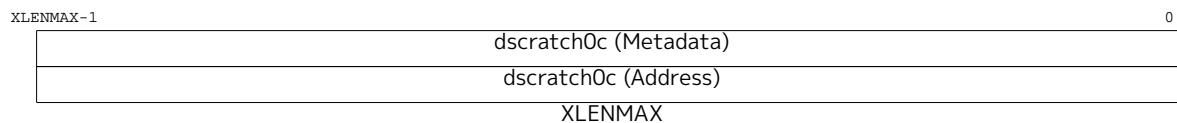

| 4.2.4. Debug Scratch Register 0 (dscratch0c) . . . . .                            | 35 |

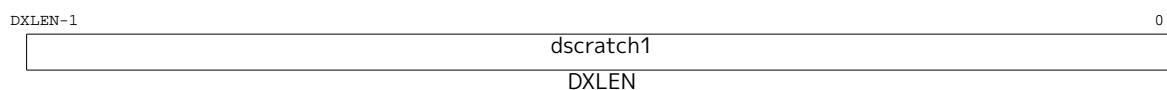

| 4.2.5. Debug Scratch Register 1 (dscratch1) . . . . .                             | 35 |

| 4.2.6. Debug Scratch Register 1 (dscratch1c) . . . . .                            | 35 |

| 5. "Zcheri_pte" Extension for CHERI Page-Based Virtual-Memory Systems . . . . .   | 36 |

| 5.1. Extending the Page Table Entry Format . . . . .                              | 36 |

| 5.2. Extending the Machine Environment Configuration Register (menvcfg) . . . . . | 37 |

| 6. "Zcheri_legacy" Extension for CHERI Legacy Mode . . . . .                      | 39 |

| 6.1. CHERI Execution Mode . . . . .                                               | 39 |

| 6.2. Zcheri_legacy Instructions . . . . .                                         | 40 |

|                                                                                     |    |

|-------------------------------------------------------------------------------------|----|

| 6.2.1. Capability Load and Store Instructions .....                                 | 40 |

| 6.2.2. Unconditional Capability Jumps .....                                         | 40 |

| 6.3. Existing RISC-V Instructions .....                                             | 40 |

| 6.3.1. Control Transfer Instructions .....                                          | 40 |

| 6.3.2. Conditional Branches .....                                                   | 41 |

| 6.3.3. Load and Store Instructions .....                                            | 41 |

| 6.3.4. CSR Instructions .....                                                       | 41 |

| 6.4. Integrating Zcheri_legacy with Sdext .....                                     | 42 |

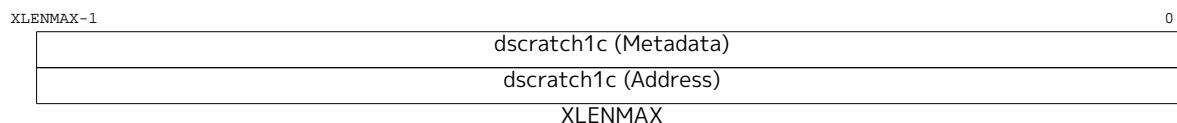

| 6.5. Debug Default Data Capability (dddc) .....                                     | 42 |

| 6.6. Disabling CHERI Features .....                                                 | 42 |

| 6.7. Added CLEN-wide CSRs .....                                                     | 43 |

| 6.7.1. Machine ISA Register (misa) .....                                            | 43 |

| 6.7.2. Machine Status Registers (mstatus and mstatush) .....                        | 43 |

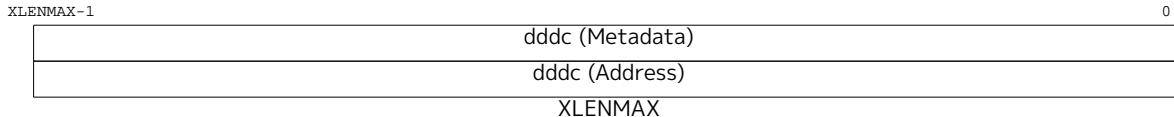

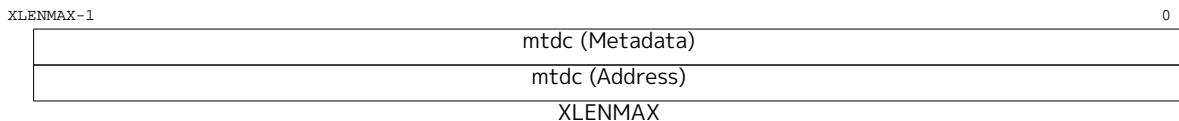

| 6.7.3. Machine Trap Default Capability Register (mtdc) .....                        | 44 |

| 6.7.4. Machine Environment Configuration Register (menvcfg) .....                   | 44 |

| 6.7.5. Supervisor Trap Default Capability Register (stdc) .....                     | 44 |

| 6.7.6. Supervisor Environment Configuration Register (senvcfg) .....                | 44 |

| 6.7.7. Default Data Capability (ddc) .....                                          | 45 |

| 7. "Zcheri_mode" Extension for CHERI Execution Mode .....                           | 46 |

| 7.1. CHERI Execution Mode .....                                                     | 46 |

| 7.2. Zcheri_mode Instructions .....                                                 | 46 |

| 7.2.1. Capability Manipulation Instructions .....                                   | 47 |

| 7.2.2. Mode Change Instructions .....                                               | 47 |

| 7.2.3. Unconditional Capability Jumps .....                                         | 47 |

| 7.3. Integrating Zcheri_mode with Sdext .....                                       | 47 |

| 8. RISC-V Instructions and Extensions Reference .....                               | 48 |

| 8.1. "Zcheri_purecap", "Zcheri_legacy" and "Zcheri_mode" Extensions for CHERI ..... | 49 |

| 8.1.1. JALR.PCC .....                                                               | 50 |

| 8.1.2. JALR.CAP .....                                                               | 50 |

| 8.1.3. CMOVE .....                                                                  | 52 |

| 8.1.4. CMODESWITCH .....                                                            | 53 |

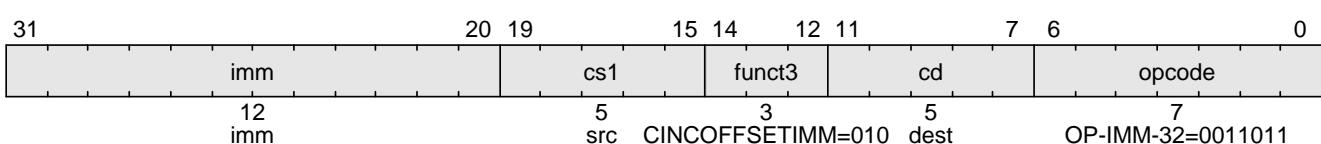

| 8.1.5. CINCOFFSETIMM .....                                                          | 54 |

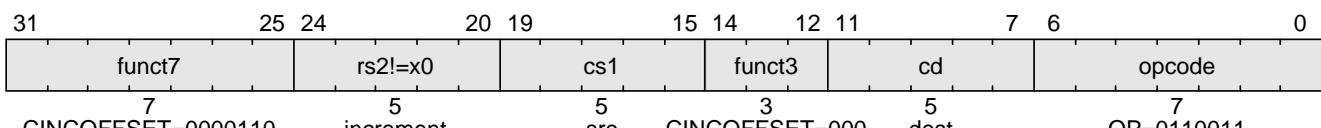

| 8.1.6. CINCOFFSET .....                                                             | 54 |

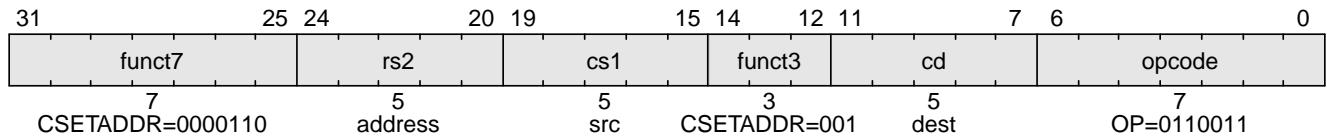

| 8.1.7. CSETADDR .....                                                               | 55 |

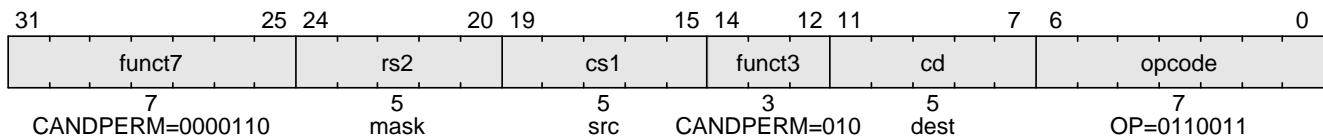

| 8.1.8. CANDPERM .....                                                               | 56 |

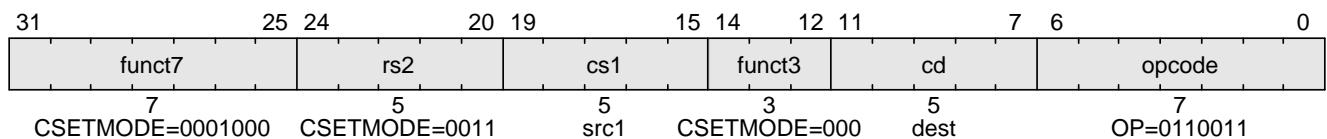

| 8.1.9. CSETMODE .....                                                               | 57 |

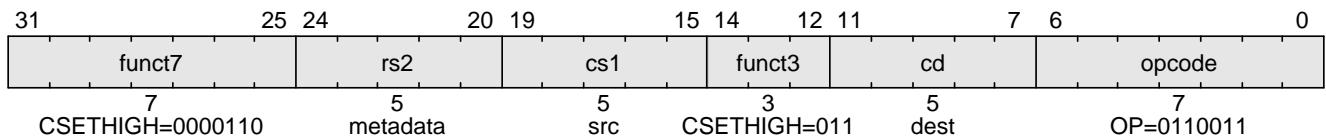

| 8.1.10. CSETHIGH .....                                                              | 58 |

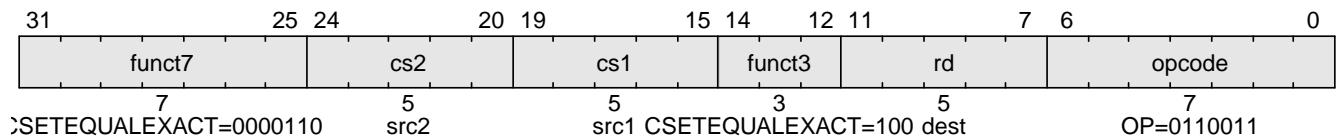

| 8.1.11. CSETEQUALEXACT .....                                                        | 59 |

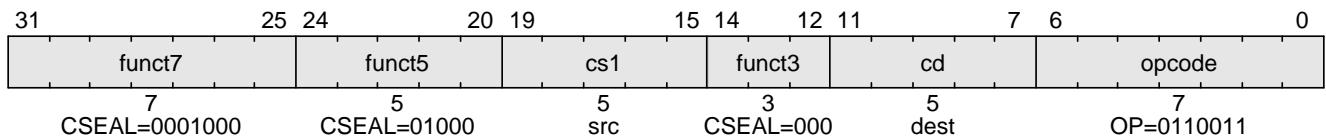

| 8.1.12. CSEAL .....                                                                 | 60 |

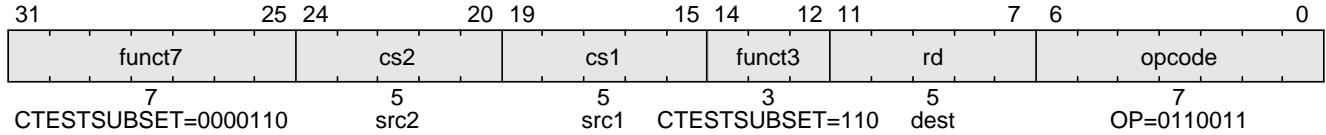

| 8.1.13. CTESTSUBSET .....                                                           | 61 |

| 8.1.14. CBUILDCAP .....                                                             | 62 |

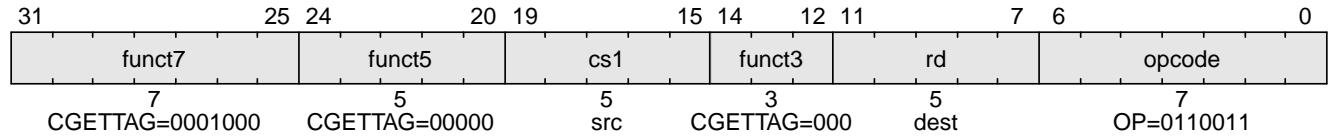

| 8.1.15. CGETTAG .....                                                               | 63 |

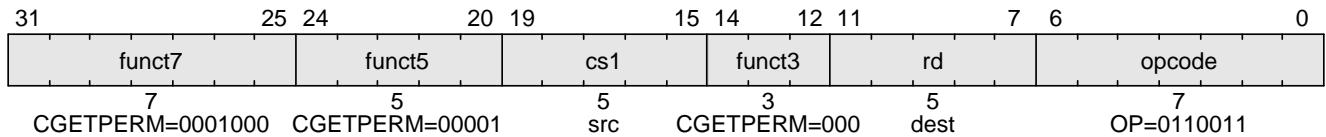

| 8.1.16. CGETPERM .....                                                              | 64 |

|                                                              |    |

|--------------------------------------------------------------|----|

| 8.1.17. CGETHIGH .....                                       | 65 |

| 8.1.18. CGETBASE .....                                       | 66 |

| 8.1.19. CGETLEN .....                                        | 67 |

| 8.1.20. CSETBOUNDSIMM .....                                  | 68 |

| 8.1.21. CSETBOUNDS .....                                     | 68 |

| 8.1.22. CSETBOUNDSINEXACT .....                              | 69 |

| 8.1.23. CRAM .....                                           | 70 |

| 8.1.24. LC .....                                             | 71 |

| 8.1.25. CLC .....                                            | 71 |

| 8.1.26. SC .....                                             | 73 |

| 8.1.27. CSC .....                                            | 73 |

| 8.2. RV32I/E and RV64I/E Base Integer Instruction Sets ..... | 75 |

| 8.2.1. AUIPC .....                                           | 76 |

| 8.2.2. AUIPCC .....                                          | 76 |

| 8.2.3. BEQ, BNE, BLT[U], BGE[U] .....                        | 77 |

| 8.2.4. CJALR .....                                           | 78 |

| 8.2.5. CJAL, JALR .....                                      | 78 |

| 8.2.6. CJAL .....                                            | 80 |

| 8.2.7. CJAL, JAL .....                                       | 80 |

| 8.2.8. CLWU .....                                            | 81 |

| 8.2.9. CLW .....                                             | 81 |

| 8.2.10. CLHU .....                                           | 81 |

| 8.2.11. CLH .....                                            | 81 |

| 8.2.12. CLBU .....                                           | 81 |

| 8.2.13. CLB .....                                            | 81 |

| 8.2.14. LD .....                                             | 81 |

| 8.2.15. LWU .....                                            | 81 |

| 8.2.16. LW .....                                             | 81 |

| 8.2.17. LHU .....                                            | 81 |

| 8.2.18. LH .....                                             | 81 |

| 8.2.19. LBU .....                                            | 81 |

| 8.2.20. LB .....                                             | 81 |

| 8.2.21. CLD .....                                            | 82 |

| 8.2.22. CSW .....                                            | 84 |

| 8.2.23. CSH .....                                            | 84 |

| 8.2.24. CSB .....                                            | 84 |

| 8.2.25. SD .....                                             | 84 |

| 8.2.26. SW .....                                             | 84 |

| 8.2.27. SH .....                                             | 84 |

| 8.2.28. SB .....                                             | 84 |

| 8.2.29. CSD .....                                            | 85 |

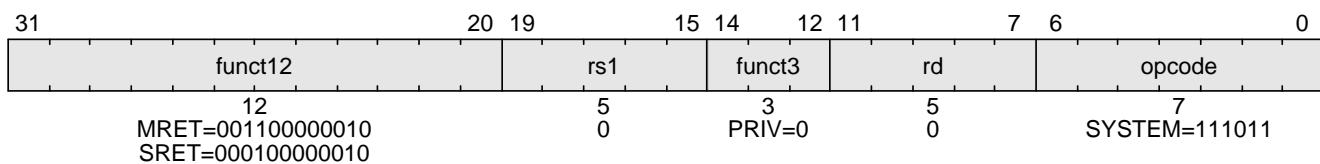

| 8.2.30. SRET .....                                           | 87 |

| 8.2.31. MRET .....                                           | 87 |

|                                                                               |     |

|-------------------------------------------------------------------------------|-----|

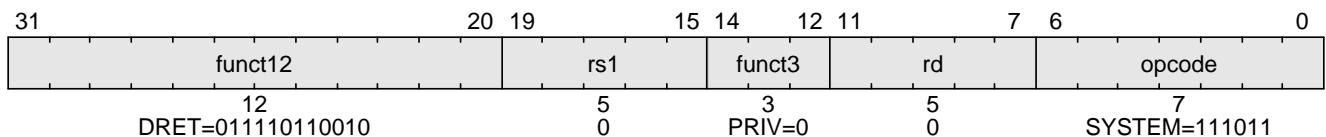

| 8.2.32. DRET .....                                                            | 88  |

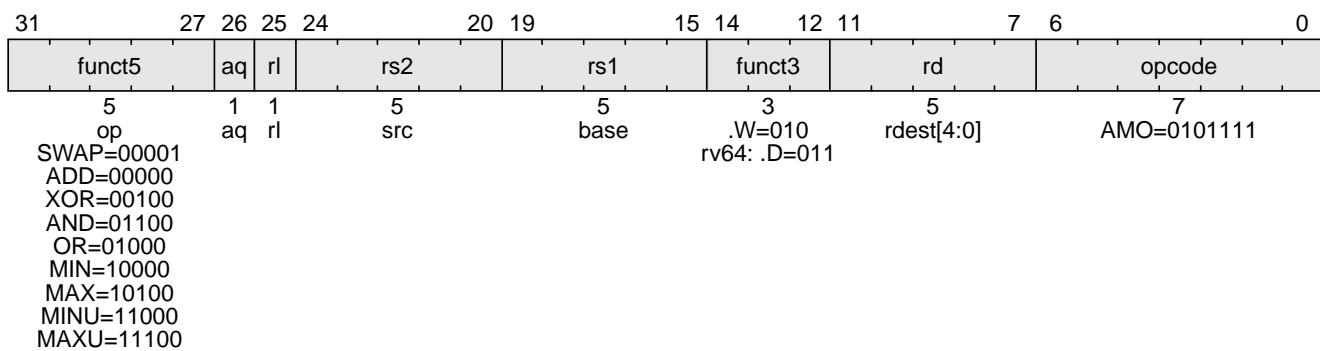

| 8.3. "A" Standard Extension for Atomic Instructions .....                     | 89  |

| 8.3.1. CAMO<OP>.W .....                                                       | 90  |

| 8.3.2. CAMO<OP>.D .....                                                       | 90  |

| 8.3.3. AMO<OP>.W .....                                                        | 90  |

| 8.3.4. CAMO<OP>.W .....                                                       | 91  |

| 8.3.5. AMOSWAP.C .....                                                        | 93  |

| 8.3.6. CAMOSWAP.C .....                                                       | 93  |

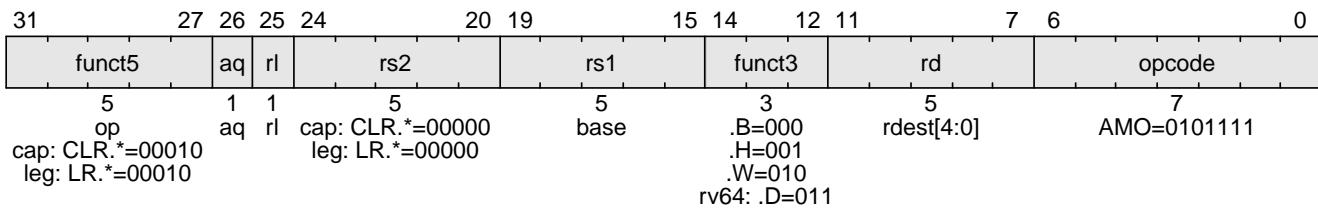

| 8.3.7. CLR.D .....                                                            | 95  |

| 8.3.8. CLR.W .....                                                            | 95  |

| 8.3.9. CLR.H .....                                                            | 95  |

| 8.3.10. CLR.B .....                                                           | 95  |

| 8.3.11. LR.D .....                                                            | 95  |

| 8.3.12. LR.W .....                                                            | 95  |

| 8.3.13. LR.H .....                                                            | 95  |

| 8.3.14. LR.B .....                                                            | 96  |

| 8.3.15. LR.C .....                                                            | 98  |

| 8.3.16. CLR.C .....                                                           | 98  |

| 8.3.17. CSC.D .....                                                           | 100 |

| 8.3.18. CSC.W .....                                                           | 100 |

| 8.3.19. CSC.H .....                                                           | 100 |

| 8.3.20. CSC.B .....                                                           | 100 |

| 8.3.21. SC.D .....                                                            | 100 |

| 8.3.22. SC.W .....                                                            | 100 |

| 8.3.23. SC.H .....                                                            | 100 |

| 8.3.24. SC.B .....                                                            | 101 |

| 8.3.25. SC.C .....                                                            | 103 |

| 8.3.26. CSC.C .....                                                           | 103 |

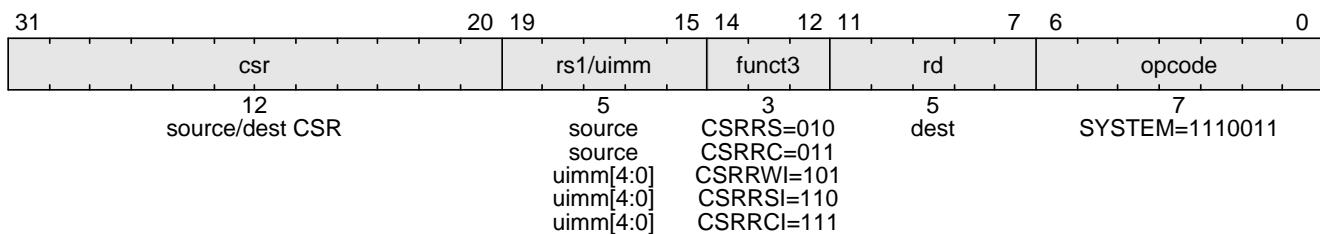

| 8.4. "Zicsr", Control and Status Register (CSR) Instructions .....            | 105 |

| 8.4.1. CSRRW .....                                                            | 106 |

| 8.4.2. CSRRWI .....                                                           | 107 |

| 8.4.3. CSRRS .....                                                            | 107 |

| 8.4.4. CSRRSI .....                                                           | 107 |

| 8.4.5. CSRRC .....                                                            | 107 |

| 8.4.6. CSRRCI .....                                                           | 108 |

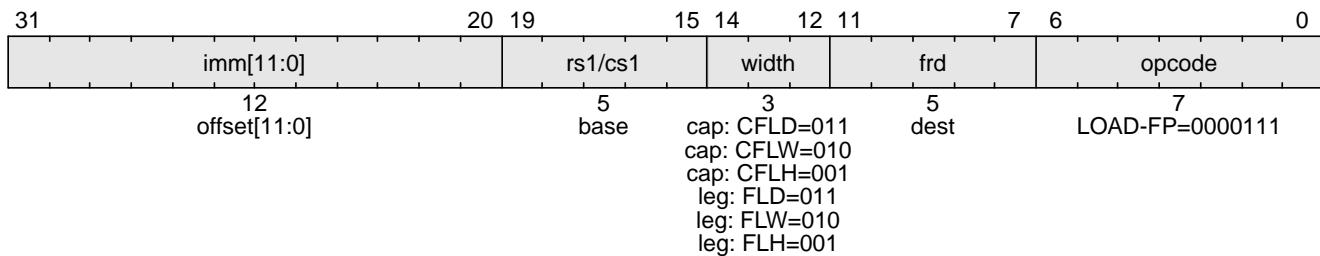

| 8.5. "Zfh", "Zfhmin", "F" and "D" Standard Extension for Floating-Point ..... | 109 |

| 8.5.1. CFLD .....                                                             | 110 |

| 8.5.2. CFLW .....                                                             | 110 |

| 8.5.3. CFLH .....                                                             | 110 |

| 8.5.4. FLD .....                                                              | 110 |

| 8.5.5. FLW .....                                                              | 110 |

| 8.5.6. FLH .....                                                              | 111 |

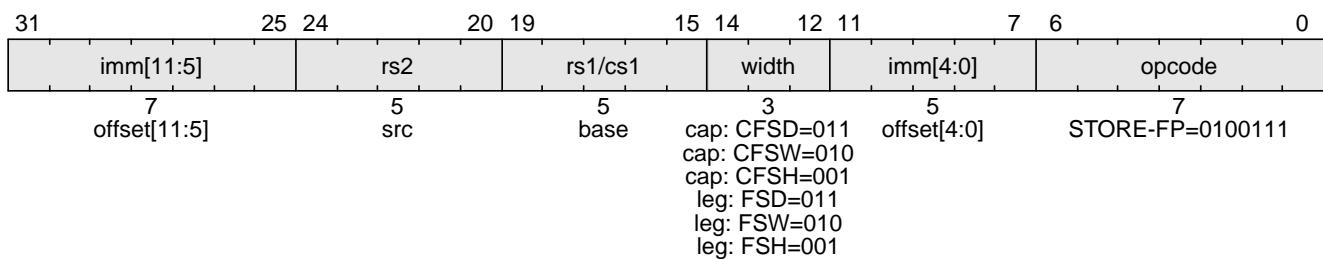

| 8.5.7. CFSD .....                                                             | 113 |

|                                                               |     |

|---------------------------------------------------------------|-----|

| 8.5.8. CFSW .....                                             | 113 |

| 8.5.9. CFSH .....                                             | 113 |

| 8.5.10. FSD .....                                             | 113 |

| 8.5.11. FSW .....                                             | 113 |

| 8.5.12. FSH .....                                             | 114 |

| 8.6. "C" Standard Extension for Compressed Instructions ..... | 116 |

| 8.6.1. C.BEQZ, C.BNEZ .....                                   | 117 |

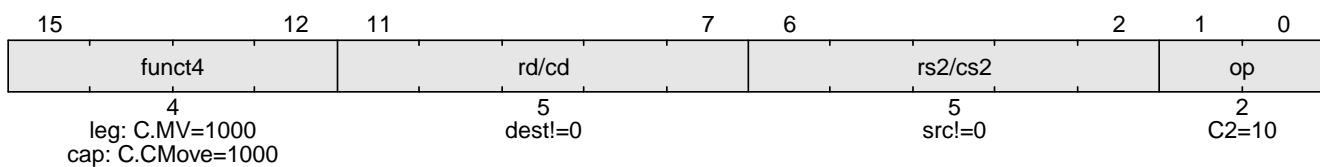

| 8.6.2. C.MV .....                                             | 118 |

| 8.6.3. C.CMOVE .....                                          | 118 |

| 8.6.4. C.ADDI16SP .....                                       | 119 |

| 8.6.5. C.CINCOFFSET16CSP .....                                | 119 |

| 8.6.6. C.ADDI4SPN .....                                       | 120 |

| 8.6.7. C.CINCOFFSET4CSPN .....                                | 120 |

| 8.6.8. C.CMODESWITCH .....                                    | 121 |

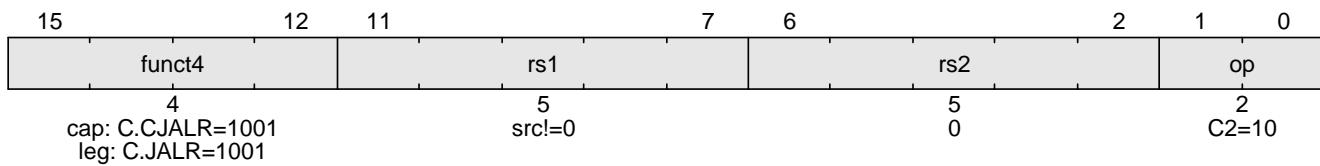

| 8.6.9. C.JALR .....                                           | 122 |

| 8.6.10. C.CJALR .....                                         | 122 |

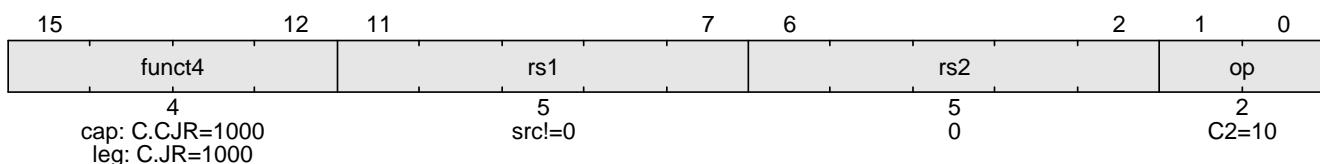

| 8.6.11. C.CJR .....                                           | 123 |

| 8.6.12. C.JR .....                                            | 123 |

| 8.6.13. C.JAL .....                                           | 124 |

| 8.6.14. C.CJAL .....                                          | 124 |

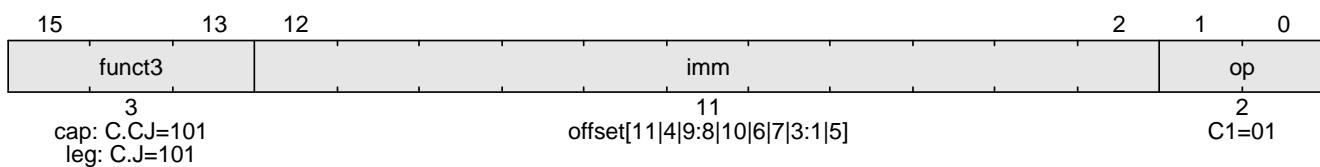

| 8.6.15. C.J .....                                             | 125 |

| 8.6.16. C.CJ .....                                            | 125 |

| 8.6.17. C.CLD .....                                           | 126 |

| 8.6.18. C.CLW .....                                           | 126 |

| 8.6.19. C.LD .....                                            | 126 |

| 8.6.20. C.LW .....                                            | 127 |

| 8.6.21. C.CLWSP .....                                         | 129 |

| 8.6.22. C.CLDSP .....                                         | 129 |

| 8.6.23. C.LWSP .....                                          | 129 |

| 8.6.24. C.LDSP .....                                          | 130 |

| 8.6.25. C.FLW .....                                           | 132 |

| 8.6.26. C.FLWSP .....                                         | 132 |

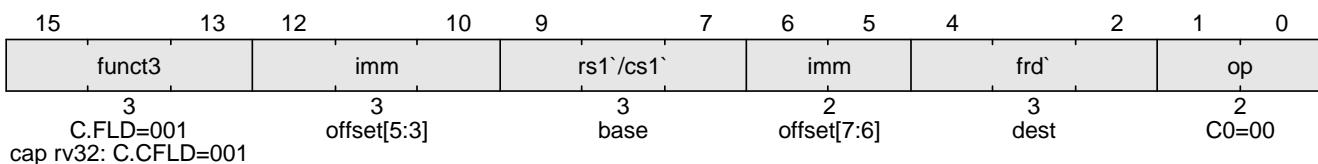

| 8.6.27. C.CFLD .....                                          | 133 |

| 8.6.28. C.FLD .....                                           | 133 |

| 8.6.29. C.CFLDSP .....                                        | 133 |

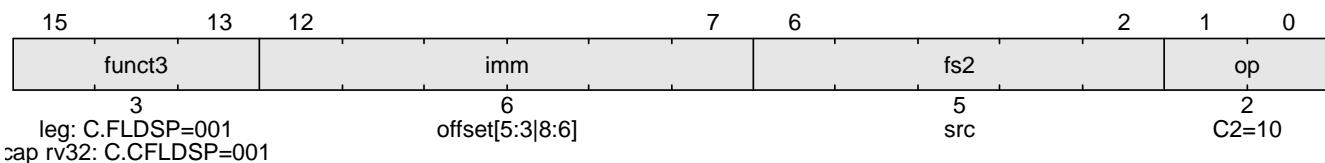

| 8.6.30. C.FLDSP .....                                         | 134 |

| 8.6.31. C.CLC .....                                           | 136 |

| 8.6.32. C.CLCSP .....                                         | 136 |

| 8.6.33. C.CSD .....                                           | 137 |

| 8.6.34. C.CSW .....                                           | 137 |

| 8.6.35. C.SD .....                                            | 137 |

| 8.6.36. C.SW .....                                            | 138 |

| 8.6.37. C.CSWSP .....                                         | 140 |

|                                                                                                  |     |

|--------------------------------------------------------------------------------------------------|-----|

| 8.6.38. C.CSDSP .....                                                                            | 140 |

| 8.6.39. C.SWSP .....                                                                             | 140 |

| 8.6.40. C.SDSP .....                                                                             | 141 |

| 8.6.41. C.FSW .....                                                                              | 143 |

| 8.6.42. C.FSWSP .....                                                                            | 143 |

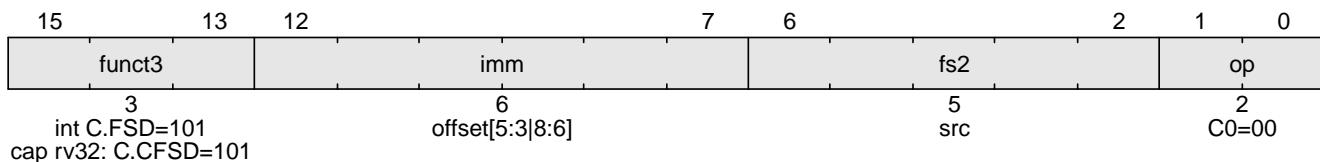

| 8.6.43. C.CFSD .....                                                                             | 144 |

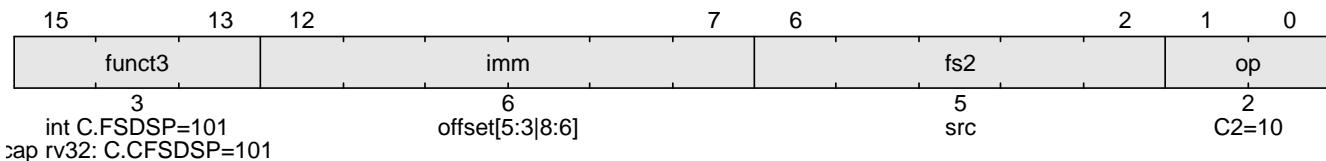

| 8.6.44. C.CFSDSP .....                                                                           | 144 |

| 8.6.45. C.FSD .....                                                                              | 144 |

| 8.6.46. C.FSDSP .....                                                                            | 145 |

| 8.6.47. C.CSC .....                                                                              | 147 |

| 8.6.48. C.CSC, C.CSCSP .....                                                                     | 147 |

| 8.7. "Zicbom", "Zicbop", "Zicboz" Standard Extensions for Base Cache Management Operations ..... | 149 |

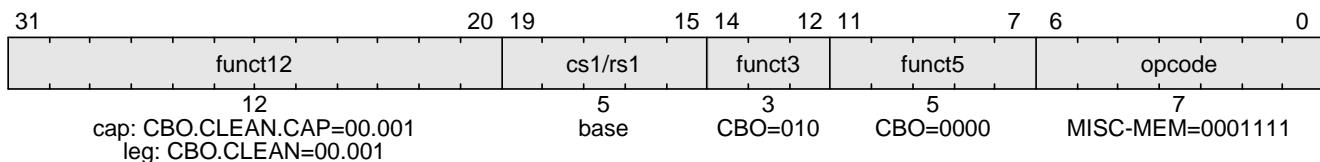

| 8.7.1. CBO.CLEAN .....                                                                           | 150 |

| 8.7.2. CBO.CLEAN.CAP .....                                                                       | 150 |

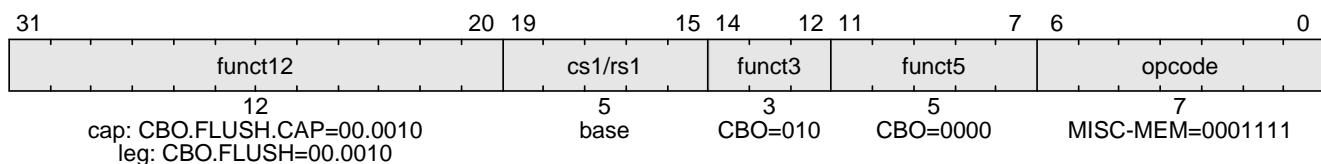

| 8.7.3. CBO.FLUSH .....                                                                           | 151 |

| 8.7.4. CBO.FLUSH.CAP .....                                                                       | 151 |

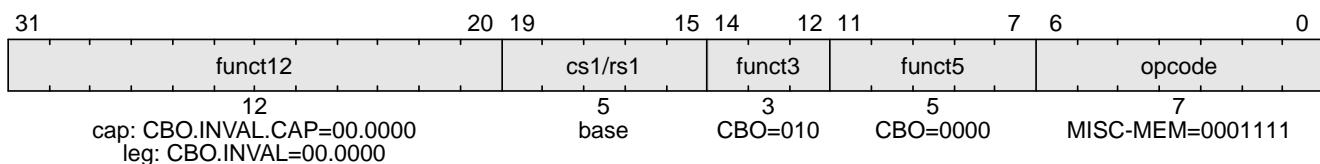

| 8.7.5. CBOINVAL .....                                                                            | 152 |

| 8.7.6. CBOINVAL.CAP .....                                                                        | 152 |

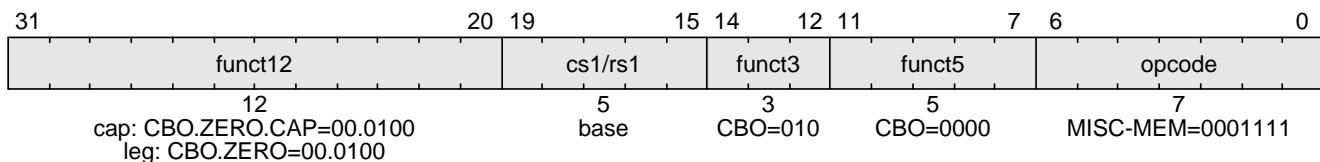

| 8.7.7. CBO.ZERO .....                                                                            | 154 |

| 8.7.8. CBO.ZERO.CAP .....                                                                        | 154 |

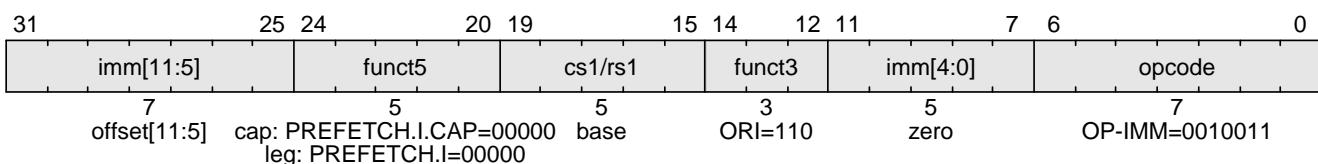

| 8.7.9. PREFETCH.I .....                                                                          | 156 |

| 8.7.10. PREFETCH.I.CAP .....                                                                     | 156 |

| 8.7.11. PREFETCH.R .....                                                                         | 158 |

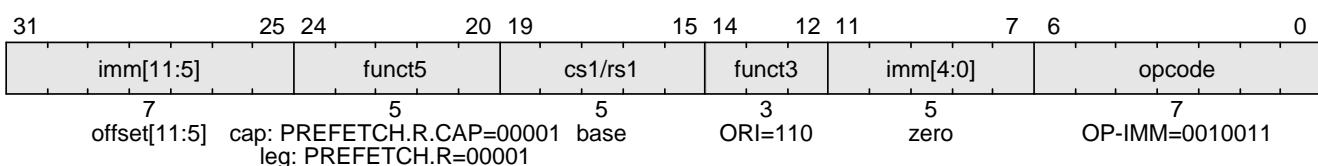

| 8.7.12. PREFETCH.R.CAP .....                                                                     | 158 |

| 8.7.13. PREFETCH.W .....                                                                         | 160 |

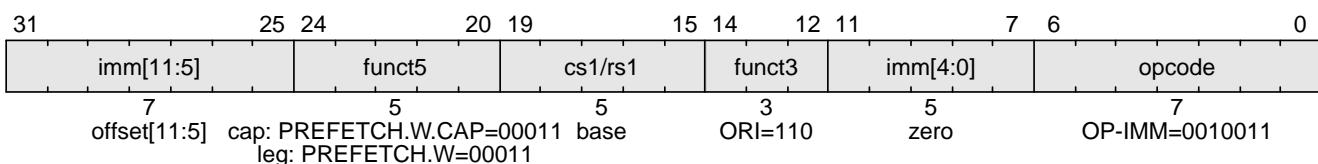

| 8.7.14. PREFETCH.W.CAP .....                                                                     | 160 |

| 8.8. "Zba" Extension for Bit Manipulation Instructions .....                                     | 161 |

| 8.8.1. CSH1ADD .....                                                                             | 162 |

| 8.8.2. CSH2ADD .....                                                                             | 162 |

| 8.8.3. CSH3ADD .....                                                                             | 162 |

| 8.8.4. SH1ADD .....                                                                              | 162 |

| 8.8.5. SH2ADD .....                                                                              | 162 |

| 8.8.6. SH3ADD .....                                                                              | 163 |

| 8.8.7. CSH1ADD.UW .....                                                                          | 164 |

| 8.8.8. CSH2ADD.UW .....                                                                          | 164 |

| 8.8.9. CSH3ADD.UW .....                                                                          | 164 |

| 8.8.10. SH1ADD.UW .....                                                                          | 164 |

| 8.8.11. SH2ADD.UW .....                                                                          | 164 |

| 8.8.12. SH3ADD.UW .....                                                                          | 165 |

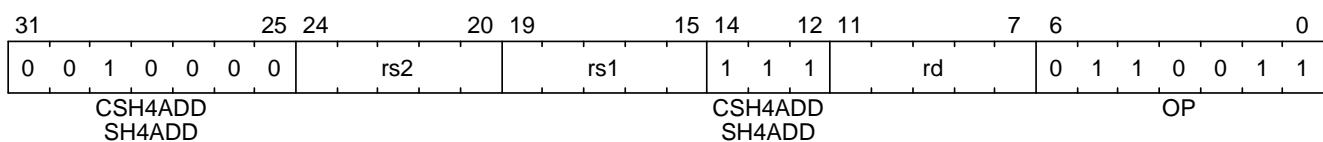

| 8.8.13. SH4ADD .....                                                                             | 166 |

| 8.8.14. CSH4ADD .....                                                                            | 166 |

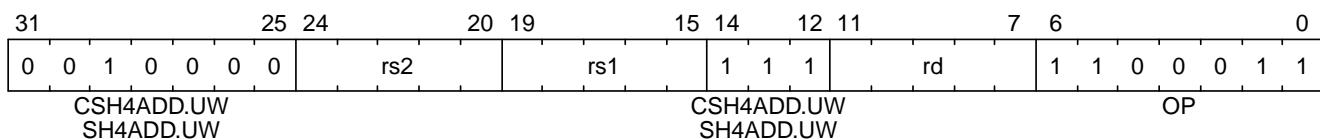

| 8.8.15. SH4ADD.UW .....                                                                          | 167 |

| 8.8.16. CSH4ADD.UW .....                                                                         | 167 |

|                                                               |     |

|---------------------------------------------------------------|-----|

| 8.9. "Zcb" Standard Extension For Code-Size Reduction .....   | 168 |

| 8.9.1. C.CLH .....                                            | 169 |

| 8.9.2. C.CLHU .....                                           | 169 |

| 8.9.3. C.CLBU .....                                           | 169 |

| 8.9.4. C.LH .....                                             | 169 |

| 8.9.5. C.LHU .....                                            | 169 |

| 8.9.6. C.LBU .....                                            | 170 |

| 8.9.7. C.CSH .....                                            | 172 |

| 8.9.8. C.CSB .....                                            | 172 |

| 8.9.9. C.SH .....                                             | 172 |

| 8.9.10. C.CSH, C.CSB, C.SH, C.SB .....                        | 173 |

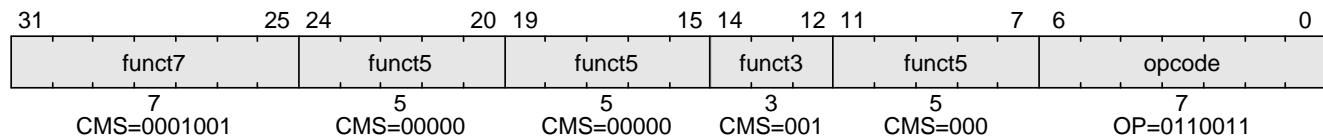

| 8.10. "Zcmp" Standard Extension For Code-Size Reduction ..... | 175 |

| 8.10.1. CM.PUSH .....                                         | 176 |

| 8.10.2. CM.CPUSH .....                                        | 176 |

| 8.10.3. CM.POP .....                                          | 178 |

| 8.10.4. CM.CPOP .....                                         | 178 |

| 8.10.5. CM.POPRET .....                                       | 180 |

| 8.10.6. CM.CPOPRET .....                                      | 180 |

| 8.10.7. CM.POPRETZ .....                                      | 182 |

| 8.10.8. CM.CPOPRETZ .....                                     | 182 |

| 8.10.9. CM.MVSA01 .....                                       | 184 |

| 8.10.10. CM.CMVSA01 .....                                     | 184 |

| 8.10.11. CM.MVA01S .....                                      | 185 |

| 8.10.12. CM.CMVA01S .....                                     | 185 |

| 8.11. "Zcmt" Standard Extension For Code-Size Reduction ..... | 186 |

| 8.11.1. Jump Vector Table CSR (jvt) .....                     | 186 |

| 8.11.2. Jump Vector Table CSR (jvtc) .....                    | 186 |

| 8.11.3. CM.JALT .....                                         | 187 |

| 8.11.4. CM.CJALT .....                                        | 187 |

| 8.11.5. CM.JT .....                                           | 189 |

| 8.11.6. CM.CJT .....                                          | 189 |

| 9. Extension summary .....                                    | 191 |

| 9.1. Zbhlrsc .....                                            | 191 |

| 9.2. Zcheri_purecap .....                                     | 191 |

| 9.3. Zcheri_legacy .....                                      | 194 |

| 9.4. Zcheri_mode .....                                        | 196 |

| 9.5. Instruction Modes .....                                  | 196 |

| 10. Capability Width CSR Summary .....                        | 202 |

| 10.1. Other tables .....                                      | 203 |

| Bibliography .....                                            | 207 |

# Preamble

*This document is in the [Development state](#)*

*Expect potential changes. This draft specification is likely to evolve before it is accepted as a standard. Implementations based on this draft may not conform to the future standard.*

# Copyright and license information

This specification is licensed under the Creative Commons Attribution 4.0 International License (CC-BY 4.0). The full license text is available at [creativecommons.org/licenses/by/4.0/](https://creativecommons.org/licenses/by/4.0/).

Copyright 2024 by RISC-V International.

# Contributors

This RISC-V specification has been contributed to directly or indirectly by:

- Hesham Almatary <[hesham.almatary@cl.cam.ac.uk](mailto:hesham.almatary@cl.cam.ac.uk)>

- Andres Amaya Garcia <[andres.amaya@codasip.com](mailto:andres.amaya@codasip.com)>

- John Baldwin <[jhb61@cl.cam.ac.uk](mailto:jhb61@cl.cam.ac.uk)>

- David Chisnall <[david.chisnall@cl.cam.ac.uk](mailto:david.chisnall@cl.cam.ac.uk)>

- Jessica Clarke <[jessica.clarke@cl.cam.ac.uk](mailto:jessica.clarke@cl.cam.ac.uk)>

- Brooks Davis <[brooks.davis@sri.com](mailto:brooks.davis@sri.com)>

- Nathaniel Wesley Filardo <[nwf20@cam.ac.uk](mailto:nwf20@cam.ac.uk)>

- Franz A. Fuchs <[faf28@cam.ac.uk](mailto:faf28@cam.ac.uk)>

- Timothy Hutt <[timothy.hutt@codasip.com](mailto:timothy.hutt@codasip.com)>

- Alexandre Joannou <[alexandre.joannou@cl.cam.ac.uk](mailto:alexandre.joannou@cl.cam.ac.uk)>

- Tariq Kurd <[tariq.kurd@codasip.com](mailto:tariq.kurd@codasip.com)>

- Ben Laurie <[benl@google.com](mailto:benl@google.com)>

- A. Theodore Markettos <[theo.markettos@cl.cam.ac.uk](mailto:theo.markettos@cl.cam.ac.uk)>

- David McKay <[david.mckay@codasip.com](mailto:david.mckay@codasip.com)>

- Jamie Melling <[jamie.melling@codasip.com](mailto:jamie.melling@codasip.com)>

- Stuart Menefy <[stuart.menefy@codasip.com](mailto:stuart.menefy@codasip.com)>

- Simon W. Moore <[simon.moore@cl.cam.ac.uk](mailto:simon.moore@cl.cam.ac.uk)>

- Peter G. Neumann <[neumann@csl.sri.com](mailto:neumann@csl.sri.com)>

- Robert Norton <[robert.norton@cl.cam.ac.uk](mailto:robert.norton@cl.cam.ac.uk)>

- Alexander Richardson <[alexrichardson@google.com](mailto:alexrichardson@google.com)>

- Michael Roe <[mr101@cam.ac.uk](mailto:mr101@cam.ac.uk)>

- Peter Rugg <[peter.rugg@cl.cam.ac.uk](mailto:peter.rugg@cl.cam.ac.uk)>

- Peter Sewell <[peter.sewell@cl.cam.ac.uk](mailto:peter.sewell@cl.cam.ac.uk)>

- Carl Shaw <[carl.shaw@codasip.com](mailto:carl.shaw@codasip.com)>

- Robert N. M. Watson <[robert.watson@cl.cam.ac.uk](mailto:robert.watson@cl.cam.ac.uk)>

- Jonathan Woodruff <[jonathan.woodruff@cl.cam.ac.uk](mailto:jonathan.woodruff@cl.cam.ac.uk)>

# Chapter 1. Introduction

## 1.1. CHERI Concepts and Terminology

Current CPU architectures (including RISC-V) allow memory access solely by specifying and dereferencing a memory address stored as an integer value in a register or in memory. Any accidental or malicious action that modifies such an integer value can result in unrestricted access to the memory that it addresses. Unfortunately, this weak memory protection model has resulted in the majority of software security vulnerabilities present in software today.

CHERI enables software to efficiently implement fine-grained memory protection and scalable software compartmentalization by providing strong, efficient hardware mechanisms to support software execution and enable it to prevent and mitigate vulnerabilities.

Design goals include incremental adoptability from current ISAs and software stacks, low performance overhead for memory protection, significant performance improvements for software compartmentalization, formal grounding, and programmer-friendly underpinnings. It has been designed to provide strong, non-probabilistic protection rather than depending on short random numbers or truncated cryptographic hashes that can be leaked and reinjected, or that could be brute forced.

CHERI enhances the CPU to add hardware memory access control. It has an additional memory access mechanism that protects *references to code and data* (pointers), rather than the *location of code and data* (integer addresses). This mechanism is implemented by providing a new primitive, called a **capability**, that software components can use to implement strongly protected pointers within an address space.

Capabilities are unforgeable and delegatable tokens of authority that grant software the ability to perform a specific set of operations. In CHERI, integer-based pointers can be replaced by capabilities to provide memory access control. In this case, a memory access capability contains an integer memory address that is extended with metadata to protect its integrity, limit how it is manipulated, and control its use. This metadata includes:

- an out-of-band *tag* implementing strong integrity protection (differentiating valid and invalid capabilities). This prevents confusion between data and capabilities.

- *bounds* limiting the range of addresses that may be dereferenced

- *permissions* controlling the specific operations that may be performed

- *sealing* which is used to support higher-level software encapsulation

The CHERI model is motivated by the *principle of least privilege*, which argues that greater security can be obtained by minimizing the privileges accessible to running software. A second guiding principle is the *principle of intentional use*, which argues that, where many privileges are available to a piece of software, the privilege to use should be explicitly named rather than implicitly selected. While CHERI does not prevent the expression of vulnerable software designs, it provides strong vulnerability mitigation: attackers have a more limited vocabulary for attacks, and should a vulnerability be successfully exploited, they gain fewer rights, and have reduced access to further attack surfaces.

Protection properties for capabilities include the ISA ensuring that capabilities are always derived via valid manipulations of other capabilities (*provenance*), that corrupted in-memory capabilities cannot be dereferenced (*integrity*), and that rights associated with capabilities shall only ever be equal or less permissive (*monotonicity*). Tampering or modifying capabilities in an attempt to elevate their rights will

yield an invalid capability as the tag will be cleared. Attempting to dereference via an invalid capability will result in a hardware exception.

CHERI capabilities may be held in registers or in memories, and are loaded, stored, and dereferenced using CHERI-aware instructions that expect capability operands rather than integer addresses. On hardware reset, initial capabilities are made available to software via special and general-purpose capability registers. All other capabilities will be derived from these initial valid capabilities through valid capability transformations.

Developers can use CHERI to build fine-grained spatial and temporal memory protection into their system software and applications and significantly improve their security.

## 1.2. CHERI Extensions to RISC-V

This specification is based on publicly available documentation including ([Watson et al., 2023](#)) and ([Woodruff et al., 2019](#)). It defines the following extensions to support CHERI alongside RISC-V:

### Zcheri\_purecap

Introduces key, minimal CHERI concepts and features to the RISC-V ISA. The resulting extended ISA is not backwards-compatible with RISC-V

### Zcheri\_legacy

Extends Zcheri\_purecap with features to ensure that the ISA extended with CHERI allows backwards binary compatibility with RISC-V

### Zcheri\_mode

Adds a mode bit in the encoding of capabilities to allow changing the current CHERI execution mode using indirect jump instructions

### Zcheri\_pte

CHERI extension for RISC-V harts supporting page-based virtual-memory

### Zcheri\_vectorcap

CHERI extension for the RISC-V Vector (V) extension. It adds support for storing CHERI capabilities in vector registers, intended for vectorised memory copying

*The extension names are provisional and subject to change.*

Zcheri\_purecap is defined as the base extension which all CHERI RISC-V implementations must support. Zcheri\_legacy, Zcheri\_mode and Zcheri\_pte are optional extensions in addition to Zcheri\_purecap. Zcheri\_mode requires supporting both Zcheri\_purecap and Zcheri\_legacy.

If a standard vector extension is present (indicated in this document as "V", but it could equally be one of the subsets defined by a Zve\* extension) then Zcheri\_vectorcap may optionally be added in addition to Zcheri\_purecap.

We refer to software as *purecap* if it utilizes CHERI capabilities for all memory accesses — including loads, stores and instruction fetches — rather than integer addresses. Purecap software requires the CHERI RISC-V hart to support Zcheri\_purecap. We refer to software as *hybrid* if it uses integer addresses or CHERI capabilities for memory accesses. Hybrid software requires the CHERI RISC-V hart to support Zcheri\_purecap, Zcheri\_legacy and Zcheri\_mode.

See [Chapter 8](#) for compatibility with other RISC-V extensions.

## 1.3. Risks and Known Uncertainty

- All extensions could be divided up differently in future, including after ratification

- The RISC-V Architecture Review Committee (ARC) are likely to update all encodings

- The ARC are likely to update all CSR addresses

- Instruction mnemonics may be renamed

- The instruction mnemonics could be the same regardless of CHERI mode

- Any changes will affect assembly code, but assembler aliases can provide backwards compatibility

- There is no clarity on how the new Page Table Entry (PTE) bits from Zcheri\_pte will be implemented

- The PTE bits introduce a dependency between exceptions and the stored tag bit

- There is debate on whether different permission encodings are needed for XLENMAX=32 and XLENMAX=64

### 1.3.1. Pending Extensions

The base RISC-V ISAs, along with most extensions, have been reviewed for compatibility with CHERI. However, the following extensions are yet to be reviewed:

- "V" Standard Extension for Vector Operations

- "H" Hypervisor Extension

- Core-Local Interrupt Controller (CLIC)

*The list above is not complete!*

### 1.3.2. Incompatible Extensions

There are RISC-V extensions in development that may duplicate some aspects of CHERI functionality or directly conflict with CHERI and should not be available on a CHERI-enabled hart. These include:

- RISC-V CFI specification

- "J" Pointer Masking

*The list above is not complete!*

### 1.3.3. Suggested Mnemonic Renaming

[Table 1](#) lists the currently proposed renames. Please update the table when new renames are proposed or confirmed.

| Current Name  | Suggestion |

|---------------|------------|

| CMOVE         | CMV        |

| CINCOFFSET    | CADD       |

| CINCOFFSETIMM | CADDI      |

| Current Name      | Suggestion  |

|-------------------|-------------|

| C.CINCOFFSET16CSP | C.CADDI16SP |

| C.CINCOFFSET4CSPN | C.CADDI4SPN |

| CLC/LC            | CLCAP/LCAP  |

| CSC/SC            | CSCAP/SCAP  |

Table 1. Suggested instruction names

*Renaming SC is not a choice. The store capability instruction must be renamed because it conflicts with store conditional from the RISC-V A extension.*

Further to the new proposed mnemonics in [Table 1](#), the following general proposals have been discussed:

- Do not use the letter 'c' to indicate 'capability' or 'CHERI' because this conflicts with the already ratified RISC-V C extension

- We previously discussed using other letters like 'p' for 'pointer' or 'f' for 'fat pointer' although 'f' is already used for floating point

- Do not change instruction mnemonics based on the current CHERI execution mode

- For example, LW is always load word regardless of the CHERI mode, so the mnemonic CLW disappears

- This facilitates writing the ISA specification as well as code maintenance in systems software like Linux

- However, it also goes against intentionality and can make assembly code (which occurs very infrequently in real-world code) more difficult to understand without additional context

- Both options could be supported by using assembler aliases

# Chapter 2. Anatomy of Capabilities in Zcheri\_purecap

RISC-V defines variants of the base integer instruction set characterized by the width of the integer registers and the corresponding size of the address space. There are two primary ISA variants, RV32I and RV64I, which provide 32-bit and 64-bit address spaces respectively. The term XLEN refers to the width of an integer register in bits (either 32 or 64). The value of XLEN may change dynamically at run-time depending on the values written to CSRs, so we define XLENMAX to be widest XLEN that the implementation supports.

Zcheri\_purecap defines capabilities of size CLEN corresponding to  $2 * \text{XLENMAX}$  without including the tag bit. The value of CLEN is always calculated based on XLENMAX regardless of the effective XLEN value.

## 2.1. Components of a Capability

Capabilities contain the software accessible fields described in this section.

### 2.1.1. Tag

An additional hardware managed bit added to addressable memory and registers. It is stored separately and may be referred to as "out of band". It indicates whether a register or CLEN-aligned memory location contains a valid capability. If the tag is set, the capability is valid and can be dereferenced (contingent on checks such as permissions or bounds).

The capability is invalid if the tag is clear. Using an invalid capability to dereference memory or authorize any operation gives rise to exceptions. All capabilities derived from invalid capabilities are themselves invalid i.e. their tags are 0.

All locations in registers or memory able to hold a capability are CLEN+1 bits wide including the tag bit. Those locations are referred as being *CLEN-bit* or *capability wide* in this specification.

### 2.1.2. Architectural Permissions (AP)

**CHERI v9 Note:** *The permissions are encoded differently in this specification.*

This field encodes architecturally defined permissions of the capability. Permissions grant access subject to the tag being set, the capability being unsealed (see [Section 2.1.4](#)), and bounds checks (see [Section 2.1.5](#)). An operation is also contingent on requirements imposed by other RISC-V architectural features, such as virtual memory, PMP and PMAs, even if the capability grants sufficient permissions. The permissions currently defined in Zcheri\_purecap are listed in below.

#### Read Permission (R)

Allow reading integer data from memory. Tags are always read as zero when reading integer data.

#### Write Permission (W)

Allow writing integer data to memory. Tags are always written as zero when writing integer data. Every CLEN aligned word in memory has a tag, if any byte is overwritten with integer data then the tag for all CLEN-bits is cleared.

## Capability Permission (C)

Allow reading capability data from memory if the authorising capability also grants [R-permission](#).

Allow writing capability data to memory if the authorising capability also grants [W-permission](#).

## Execute Permission (X)

Allow instruction execution.

## Access System Registers Permission (ASR)

Allow access to privileged CSRs.

## Permission Encoding

The bit width of the permissions field depends on the value of XLENMAX as shown in [Table 2](#). A 4-bit vector encodes the permissions when XLENMAX=32. For this case, the legal encodings of permissions are listed in [Table 3](#). Certain combinations of permissions are impractical. For example, [G-permission](#) is superfluous when the capability does not grant either [R-permission](#) or [W-permission](#). Therefore, it is only possible to encode a subset of all combinations.

| XLENMAX | Permissions width |

|---------|-------------------|

| 32      | 4                 |

| 64      | 5                 |

*Table 2. Permissions widths depending on XLENMAX*

| Encoding | R | W | C        | X | ASR |

|----------|---|---|----------|---|-----|

| 0b0000   |   |   |          |   |     |

| 0b0001   |   |   | reserved |   |     |

| 0b0010   |   | ✓ |          |   |     |

| 0b0011   |   | ✓ | ✓        |   |     |

| 0b0100   | ✓ |   |          |   |     |

| 0b0101   | ✓ |   |          | ✓ |     |

| 0b0110   | ✓ | ✓ |          |   |     |

| 0b0111   | ✓ | ✓ | ✓        |   |     |

| 0b1000   | ✓ |   |          |   | ✓   |

| 0b1001   | ✓ |   |          | ✓ | ✓   |

| 0b1010   | ✓ | ✓ |          |   | ✓   |

| 0b1011   | ✓ | ✓ | ✓        | ✓ |     |

| 0b1100   | ✓ |   |          | ✓ | ✓   |

| 0b1101   | ✓ |   | ✓        | ✓ | ✓   |

| 0b1110   | ✓ | ✓ |          | ✓ | ✓   |

| 0b1111   | ✓ | ✓ | ✓        | ✓ | ✓   |

*Table 3. Encoding of architectural permissions for XLENMAX=32*

The encoding in [Table 3](#) is chosen to facilitate hardware implementations. Therefore, it can be worked out if the permissions are granted as follows:

- [C-permission](#): bit 0 is set

- [W-permission](#): bit 1 is set

- [X-permission](#): bit 3 is set

- [R-permission](#): bits 3 or 2 are set

- **ASR-permission**: bits 3 and 2 are set

A 5-bit vector encodes the permissions when XLENMAX=64. In this case, there is a bit per permission as shown in [Table 4](#). A permission is granted if its corresponding bit is set, otherwise the capability does not grant that permission.

| Bit | Name           |

|-----|----------------|

| 0   | C-permission   |

| 1   | W-permission   |

| 2   | R-permission   |

| 3   | X-permission   |

| 4   | ASR-permission |

*Table 4. Encoding of architectural permissions for XLENMAX=64*

*TODO: Confirm that we need a separate permissions format for 32-bit and 64-bit.*

*Valid capabilities must not have the permissions field set to a reserved value according to [Table 3](#) when XLENMAX=32.*

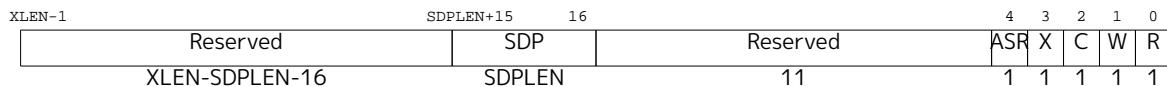

### 2.1.3. Software-Defined Permissions (SDP)

*CHERI v9 Note: CHERI v9 had no software-defined permissions for RV32*

A bit vector used by the kernel or application programs for software-defined permissions (SDP).

*Software is completely free to define the usage of these bits. For example, a program may decide to use an SDP bit to indicate the "ownership" of objects. Therefore, a capability grants permission to free the memory it references if that SDP bit is set because it "owns" that object.*

| XLENMAX | SDP width |

|---------|-----------|

| 32      | 2         |

| 64      | 4         |

*Table 5. SDP widths depending on XLENMAX*

### 2.1.4. Sealed (S) Bit

*CHERI v9: The sealing bit is new (1-bit otype) and the old CHERI v9 otype no longer exists.*

Indicates that a capability is sealed if the bit is 1 or unsealed if it is 0. Sealed capabilities cannot be dereferenced to access memory and are immutable such that modifying any of its fields clears the tag of the output capability.

In Zcheri\_purecap, the sealing bit is used to implement immutable capabilities that describe function entry points. A program may jump to a sealed capability to begin executing the instructions it references. The jump instruction automatically unseals the capability and installs it to the program counter capability (see [Section 3.2](#)). The [CJALR](#) instruction also seals the return address capability (if any) since it is the entry point to the caller function.

## 2.1.5. Bounds

**CHERI v9 Note:** The bounds mantissa width is different in XLENMAX=32. Also, the old IE bit is renamed to Exponent Format (EF); the function of IE is the inverse of EF i.e. IE=0 has the same effect as EF=1.

**CHERI v9 Note:** The mantissa width for RV32 was increased to 10.

**CHERI v9 Note:** The sense of the exponent is reversed, so an encoded value of 0 represents CAP\_MAX\_E, and CAP\_MAX\_E represents 0 from the previous specification.

The bounds encode the base and top addresses that constrain memory accesses. The capability can be used to access any memory location A in the range  $\text{base} \leq A < \text{top}$ . The bounds are encoded in compressed format, so it is not possible to encode any arbitrary combination of base and top addresses. An invalid capability with tag cleared is produced when attempting to construct a capability that is not *representable* because its bounds cannot be correctly encoded. The bounds are decoded as described in [Section 2.2](#).

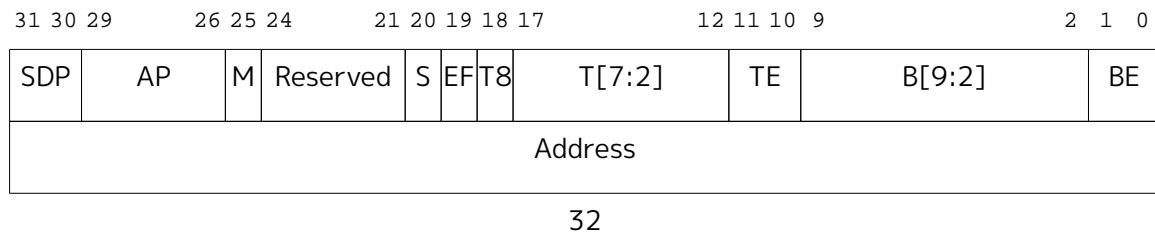

The bounds field has the following components:

- **T:** Value substituted into the capability's address to decode the top address

- **B:** Value substituted into the capability's address to decode the base address

- **E:** Exponent that determines the position at which B and T are substituted into the capability's address

- **EF:** Exponent format flag indicating the encoding for T, B and E

- The exponent is stored in T and B if EF=0, so it is 'internal'

- The exponent is zero if EF=1, so it is 'embedded'

The bit width of T and B are defined in terms of the mantissa width (MW) which is set depending on the value of XLENMAX as shown in [Table 6](#).

| XLENMAX | MW |

|---------|----|

| 32      | 10 |

| 64      | 14 |

*Table 6. Mantissa width (MW) values depending on XLENMAX*

The exponent E indicates the position of T and B within the capability's address as described in [Section 2.2](#). The bit width of the exponent (EW) is set depending on the value of XLENMAX. The maximum value of the exponent is calculated as follows:

$$\text{CAP\_MAX\_E} = \text{XLENMAX} - \text{MW} + 2$$

The possible values for EW and CAP\_MAX\_E are shown in [Table 7](#).

| XLENMAX | EW | CAP_MAX_E |

|---------|----|-----------|

| 32      | 5  | 24        |

| 64      | 6  | 52        |

*Table 7. Exponent widths and CAP\_MAX\_E depending on XLENMAX*

*The address and bounds must be representable in valid capabilities i.e. when the tag is set*

(see [Section 2.5](#)).

## 2.1.6. Address

XLENMAX integer value that encodes the byte-address of a memory location.

| XLENMAX | Address width |

|---------|---------------|

| 32      | 32            |

| 64      | 64            |

Table 8. Address widths depending on XLENMAX

## 2.1.7. Reserved Bits

Reserved bits available for future extensions to Zcheri\_purecap.

Reserved bits must be 0 in valid capabilities.

## 2.2. Capability Encoding

**CHERI v9 Note:** The encoding changes eliminate the concept of the in-memory format, and also increase precision for RV32. When  $EF=0$ ,  $T$  and  $B$  are now shifted right rather than left within the address. Also, the bounds decoding for  $XLENMAX=32$  uses a trick (see bit  $T8$ ) to save one bit when encoding the exponent.

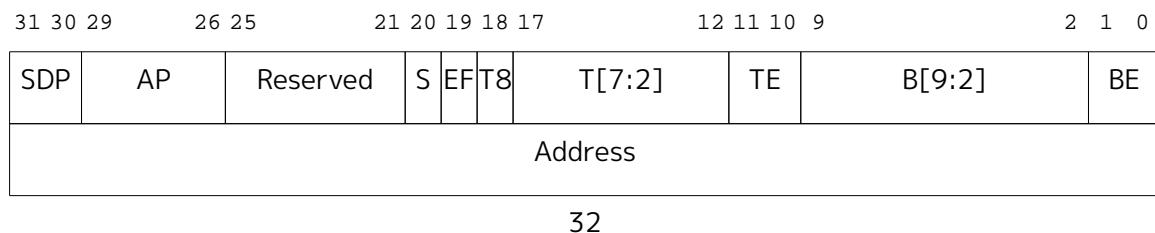

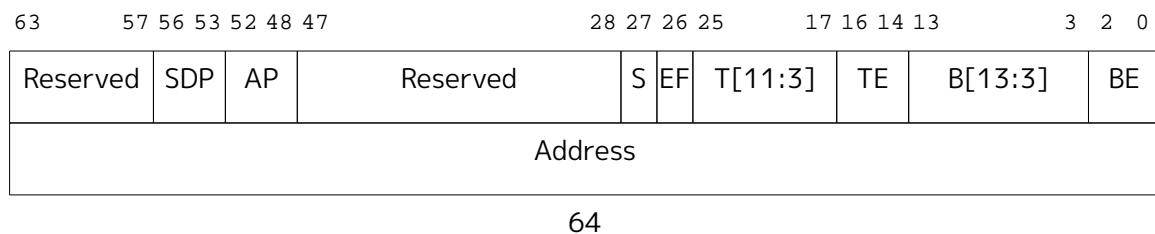

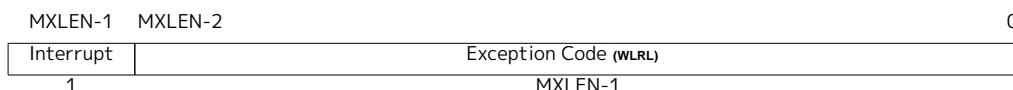

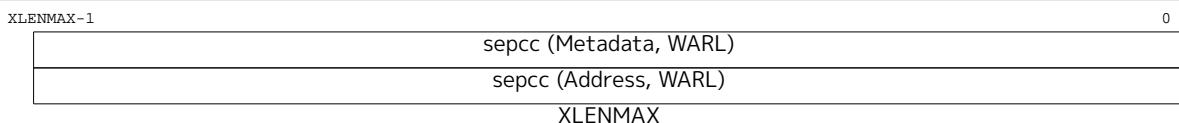

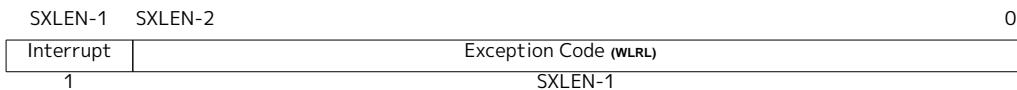

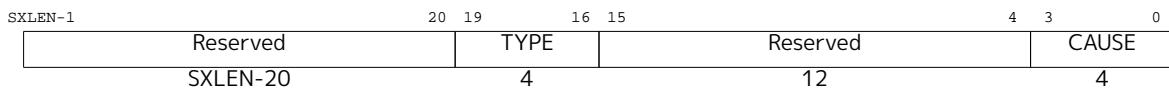

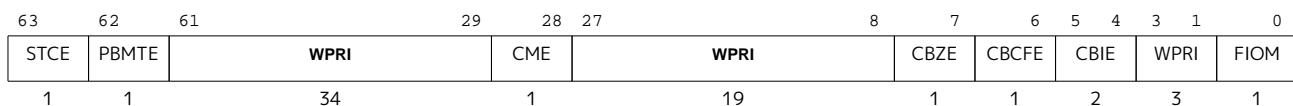

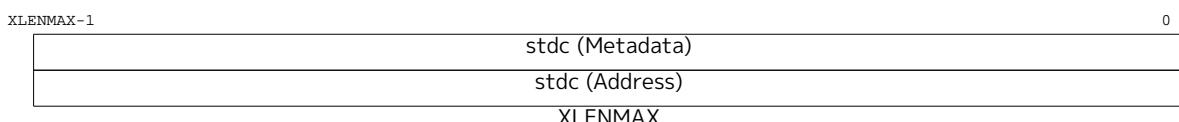

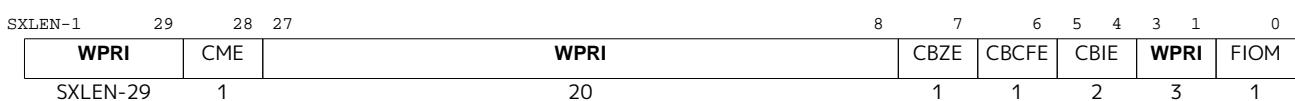

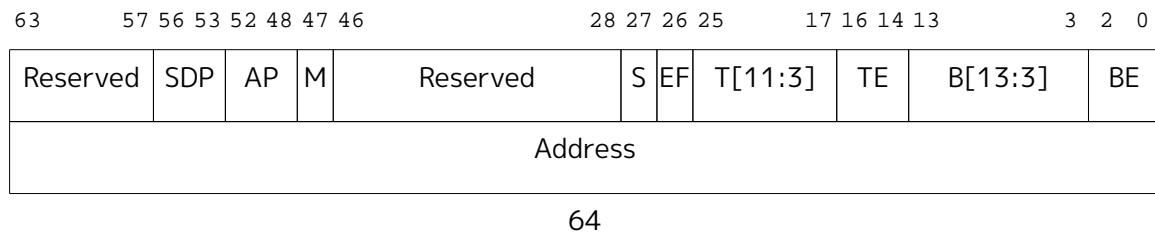

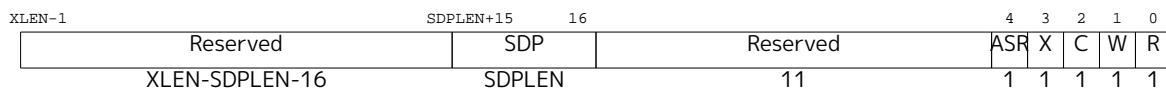

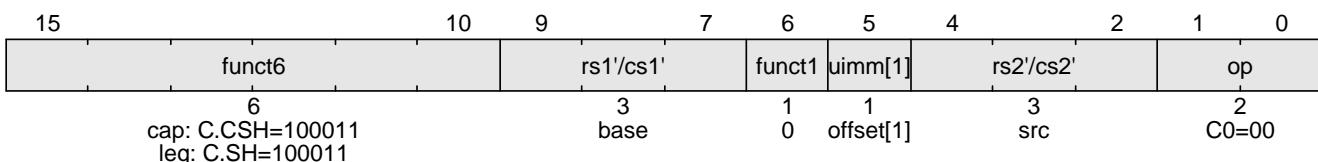

The components of a capability are encoded as shown in [Figure 1](#) and [Figure 2](#) when  $XLENMAX=32$  and  $XLENMAX=64$  respectively.

Figure 1. Capability encoding when  $XLENMAX=32$

Figure 2. Capability encoding when  $XLENMAX=64$

Each memory location or register able to hold a capability must also store the tag as out of band information that software cannot directly set or clear. The capability metadata is held in the most significant bits and the address is held in the least significant bits.

The metadata is encoded in a compressed format ([Woodruff et al., 2019](#)). It uses a floating point representation to encode the bounds relative to the capability address. The base and top addresses from the bounds are decoded as shown below.

*TODO: The pseudo-code below does not have a formal notation. It is simply a place-holder while the Sail implementation is available. In this notation,  $/$  means "integer division",  $[]$  are the bit-select operators, and arithmetic is signed.*

```

EW      = (XLENMAX == 32) ? 5 : 6

CAP_MAX_E = XLENMAX - MW + 2

If EF = 1:

E      = 0

T[EW / 2 - 1:0] = TE

B[EW / 2 - 1:0] = BE

LCout      = (T[MW - 3:0] < B[MW - 3:0]) ? 1 : 0

LMSB       = (XLENMAX == 32) ? T8 : 0

else:

E      = CAP_MAX_E - ( (XLENMAX == 32) ? { T8, TE, BE } : { TE, BE } )

T[EW / 2 - 1:0] = 0

B[EW / 2 - 1:0] = 0

LCout      = (T[MW - 3:EW / 2] < B[MW - 3:EW / 2]) ? 1 : 0

LMSB       = 1

```

Reconstituting the top two bits of T:

$$T[MW - 1:MW - 2] = B[MW - 1:MW - 2] + LCout + LMSB$$

Decoding the bounds:

```

top:   t = { a[XLENMAX - 1:E + MW] + ct, T[MW - 1:0] , {E{1'b0}} }

base:  b = { a[XLENMAX - 1:E + MW] + cb, B[MW - 1:0] , {E{1'b0}} }

```

The corrections  $c_t$  and  $c_b$  are calculated as shown below using the definitions in [Table 9](#) and [Table 10](#).

```

Ac = a[E + MW - 1:E + MW - 3]

Bc = B[MW - 1:MW - 3]

Tc = T[MW - 1:MW - 3]

R = Bc - 1

```

| $A_c < R$ | $T_c < R$ | $c_t$ |

|-----------|-----------|-------|

| false     | false     | 0     |

| false     | true      | +1    |

| true      | false     | -1    |

| true      | true      | 0     |

*Table 9. Calculation of top address correction*

| $A_c < R$ | $B_c < R$ | $c_b$ |

|-----------|-----------|-------|

| false     | false     | 0     |

| false     | true      | +1    |

| true      | false     | -1    |

| true      | true      | 0     |

*Table 10. Calculation of base address correction*

The base,  $b$ , and top,  $t$ , addresses are derived from the address by substituting  $a[E + MW - 1:E]$  with  $B$  and  $T$  respectively and clearing the lower  $E$  bits. The most significant bits of  $a$  may be adjusted up or

down by 1 using corrections  $c_b$  and  $c_t$  to allow encoding memory regions that span alignment boundaries.

The EF bit selects between two cases:

1. EF = 1: The exponent is 0 for regions less than  $2^{MW-2}$  bytes long

2. EF = 0: The exponent is *internal* with E stored in the lower bits of T and B along with  $T_8$  when XLENMAX=32. E is chosen so that the most significant non-zero bit of the length of the region aligns with  $T[MW - 2]$  in the decoded top. Therefore, the most significant two bits of T can be derived from B using the equality  $T = B + L$ , where  $L[MW - 2]$  is known from the values of EF and E and a carry out is implied if  $T[MW - 3:0] < B[MW - 3:0]$  since it is guaranteed that the top is larger than the base.

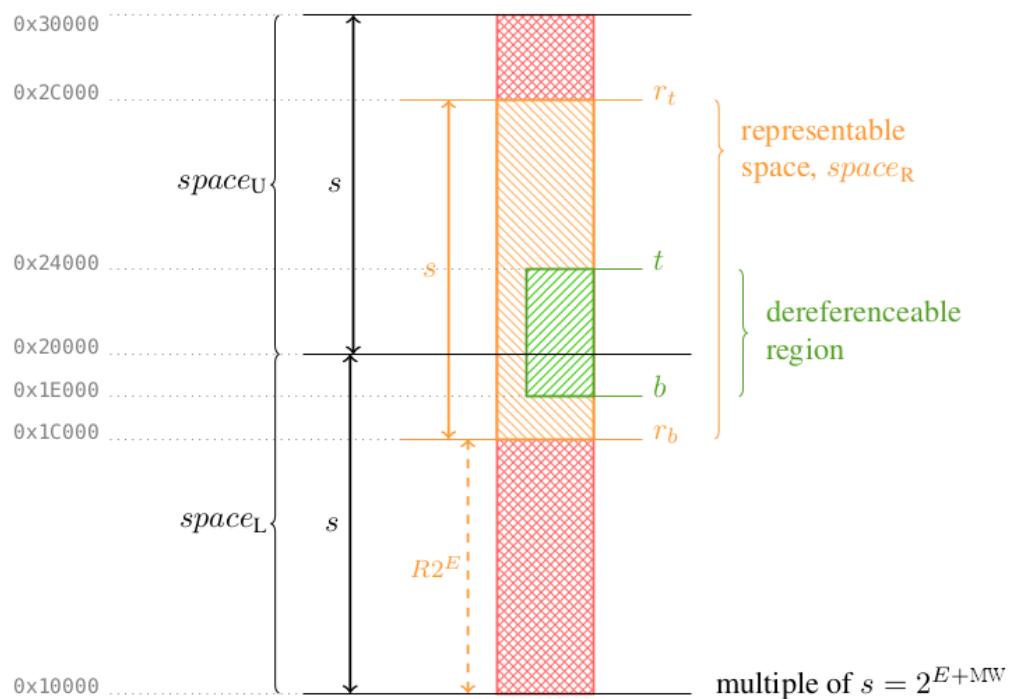

The compressed bounds encoding allows the address to roam over a large *representable* region while maintaining the original bounds. This relies on using the 'spare' encodings where  $T < B$  to define a space boundary R, relative to the base, calculated by subtracting 1 from the top three bits of B. If B, T or  $a[E + MW - 1:E]$  is less than R, it is inferred that they lie in the  $2^{E+MW}$  aligned region above R labelled  $space_U$  in Figure 3 and the corrections  $c_t$  and  $c_b$  are computed accordingly. The overall effect is that at least  $2^{E+MW}/8$  bytes below the base address and  $2^{E+MW}/4$  bytes above the top address can roam out-of-bounds while still allowing the bounds to be correctly decoded.

Figure 3. Memory address bounds encoded within a capability

A capability whose bounds cover the entire address space has 0 base and top equals  $2^{XLENMAX}$ , i.e.  $t$  is a XLENMAX + 1 bit value. However,  $b$  is a XLENMAX bit value and the size mismatch introduces additional complications when decoding, so the following condition is required to correct  $t$  for capabilities whose representable region wraps the edge of the address space:

```

if ( (E < (CAP_MAX_E - 1)) & (t[XLENMAX: XLENMAX - 1] - b[XLENMAX - 1] > 1) )

t[XLENMAX] = !t[XLENMAX]

```

That is, invert the most significant bit of  $t$  if the decoded length of the capability is larger than E.

## 2.3. NULL and Infinite Capabilities

CHERI v9 Note: Encoding **NULL** as zeros removes the need for the difference between in-memory and architectural format.

The **NULL** capability is represented with 0 in all fields. This implies that **NULL** has no permissions and its exponent E is CAP\_MAX\_E e.g. 52 when XLENMAX=64, so its bounds cover the entire address space such that the expanded base is 0 and top is  $2^{XLENMAX}$ . In contrast, the **Infinity** capability grants all permissions while its bounds also cover the whole address space.

The **Infinity** capability is also known as 'default', 'almighty', or 'root' capability.

| Field          | Value | Comment                           |

|----------------|-------|-----------------------------------|

| SDP            | zeros | Grants no permissions             |

| AP             | zeros | Grants no permissions             |

| S              | zero  | Unsealed                          |

| EF             | zero  | Internal exponent format          |

| T <sub>8</sub> | zeros | Top address bit (XLENMAX=32 only) |

| T              | zeros | Top address bits                  |

| T <sub>E</sub> | zeros | Exponent bits                     |

| B              | zeros | Base address bits                 |

| B <sub>E</sub> | zeros | Exponent bits                     |

| Address        | zeros | Capability address                |

Table 11. Field values of the **NULL** capability

| Field          | Value | Comment                           |

|----------------|-------|-----------------------------------|

| SDP            | ones  | Grants all permissions            |

| AP             | ones  | Grants all permissions            |

| S              | zero  | Unsealed                          |

| EF             | zero  | Internal exponent format          |

| T <sub>8</sub> | zeros | Top address bit (XLENMAX=32 only) |

| T              | zeros | Top address bits                  |

| T <sub>E</sub> | zeros | Exponent bits                     |

| B              | zeros | Base address bits                 |

| B <sub>E</sub> | zeros | Exponent bits                     |

| Address        | zeros | Capability address                |

Table 12. Field values of the **Infinite** capability

## 2.4. Representable Limit Check

Pointer arithmetic on capabilities must be checked to ensure that the new address is within the capability's representable region described in [Section 2.2](#). The new address, after pointer arithmetic, is within the representable region if decompressing the capability's bounds with the original and new addresses yields the same base and top addresses. In other words, given a capability with address  $a$  and the new address  $a' = a + x$ , the bounds  $b$  and  $t$  are decoded using  $a$  and the new bounds  $b'$  and  $t'$  are decoded using  $a'$ . The new address is within the capability's representable region if  $b == b' \& \& t == t'$ .

Changing a capability's address to a value outside the representable region unconditionally clears the capability's tag.

The encoding of the bounds depends upon the leading 1 of the address which is used to determine the exponent. If the leading 1 of the address moves then the bounds will need to be recalculated. Instructions like `CINCOFFSET` and `CSETADDR` update the address field but do not recalculate the bounds. Therefore, if the leading 1 moves relative to when the bounds were calculated then the tag is cleared on the result as the encoding has been invalidated.

## 2.5. Malformed Capability Bounds

A capability is *malformed* if its encoding does not describe a valid capability because its bounds cannot be correctly decoded. The following check indicates whether a capability is malformed.

```

malformedMSB = (E == CAP_MAX_E     && B[MW - 1:MW - 2] != 0)

|| (E == CAP_MAX_E - 1 && B[MW - 1]        != 0)

malformedLSB = (E < 0)

malformed    = !EF && (malformedMSB || malformedLSB)

```

The check is for malformed bounds, so it does not include reserved bits!

Capabilities with malformed bounds are always invalid anywhere in the system i.e. their tags are always 0.

# Chapter 3. Integrating Zcheri\_purecap with the RISC-V Base Integer Instruction Set

Zcheri\_purecap is an extension to the RISC-V ISA. The extension adds a carefully selected set of instructions and CSRs that are sufficient to implement new security features in the ISA. To ensure compatibility, Zcheri\_purecap also requires some changes to the primary base integer variants: RV32I, providing 32-bit addresses with 64-bit capabilities, and RV64I, providing 64-bit addresses with 128-bit capabilities. The remainder of this chapter describes these changes for both the unprivileged and privileged components of the base integer RISC-V ISAs.

*The changes described in this specification also ensure that Zcheri\_purecap is compatible with RV32E.*

## 3.1. Memory

A hart supporting Zcheri\_purecap has a single byte-addressable address space of  $2^{XLEN}$  bytes for all memory accesses. Each memory region capable of holding a capability also stores a tag bit for each naturally aligned CLEN bits (e.g. 16 bytes in RV64), so that capabilities with their tag set can only be stored in naturally aligned addresses. Tags must be atomically bound to the data they protect.

The memory address space is circular, so the byte at address  $2^{XLEN} - 1$  is adjacent to the byte at address zero. A capability's representable region described in [Section 2.2](#) is also circular, so address 0 is within the representable region of a capability where address  $2^{XLENMAX} - 1$  is within the bounds.

## 3.2. Programmer's Model for Zcheri\_purecap

For Zcheri\_purecap, the 32 unprivileged **x** registers of the base integer ISA are extended so that they are able to hold a capability. Therefore, each **x** register is CLEN bits wide and has an out of band tag bit. The **x** notation refers to the address field of the capability in an unprivileged register while the **c** notation is used to refer to the full capability (i.e. address, metadata and tag) held in the same unprivileged register.

Register **c0** is hardwired with all bits, including the capability metadata and tag, equal to 0. In other words, **c0** is hardwired to the [NULL](#) capability.

An authorising capability with appropriate permissions is required to execute instructions in Zcheri\_purecap. Therefore, the unprivileged program counter (**pc**) register is extended so that it is able to hold a capability. The extended register is called the program counter capability (**pcc**). The **pcc** address field is effectively the **pc** in the base RISC-V ISA that the hardware automatically increments as instructions are executed. The **pcc**'s metadata and tag are reset to the [Infinity](#) capability metadata and tag.

The hardware performs the following checks on **pcc** for each instruction executed in addition to the checks already required by the base RISC-V ISA. A failing check causes a CHERI exception.

- The tag must be set

- The capability must not be sealed

- The capability must grant execute permission

- All bytes of the instruction must be in bounds

## 3.3. Capability Instructions

**CHERI v9 Note:** Some instructions from the original CHERI specification were removed to save encoding space, or because they relate to features which are not yet in this specification. Instructions were removed if they do not harm performance and can be emulated using other instructions.

Zcheri\_purecap introduces new instructions to the base RISC-V integer ISA to inspect and operate on capabilities held in registers.

### 3.3.1. Capability Inspection Instructions

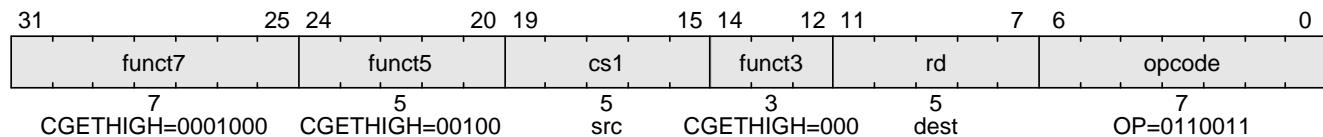

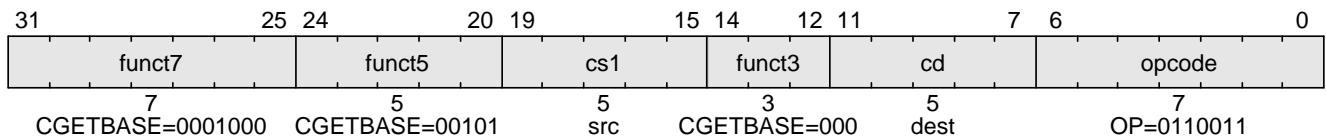

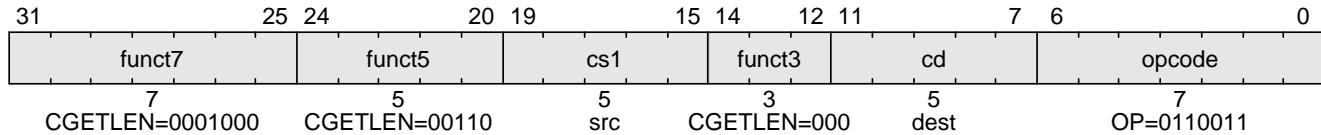

These instructions allow software to inspect the fields of a capability held in a **c** register. The output is an integer value written to an **x** register representing the decoded field of the capability, such as the permissions or bounds. These instructions do not cause exceptions.

- **CGETTAG**: inspects the tag of the input capability. The output is 1 if the tag is set and 0 otherwise

- **CGETPERM**: outputs the architectural (AP) and software-defined (SDP) permission fields of the input capability

- **CGETBASE**: outputs the expanded base address of the input capability

- **CGETLEN**: outputs the length of the input capability. Length is defined as **top** - **base**. The output is  $2^{\text{XLEN}} - 1$  when the capability's length is  $2^{\text{XLENMAX}}$

- **CRAM**: outputs the nearest bounds alignment that a valid capability can represent

- **CGETHIGH**: outputs the compressed capability metadata

- **CSETEQUALEXACT**: compares two capabilities including tag, metadata and address

- **CTESTSUBSET**: tests whether the bounds and permissions of a capability are a subset of those from another capability

**CGETBASE** and **CGETLEN** output 0 when a capability with malformed bounds is provided as an input (see [Section 2.5](#)).

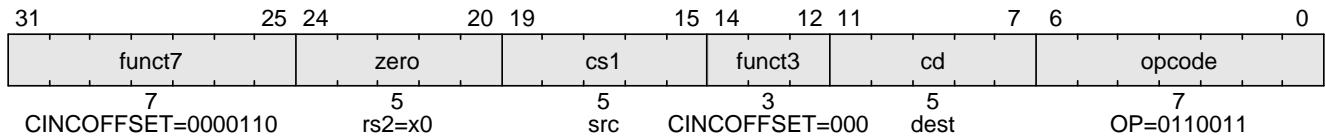

### 3.3.2. Capability Manipulation Instructions

These instructions allow software to manipulate the fields of a capability held in a **c** register. The output is a capability written to a **c** register with its fields modified. The output capability has its tag set to 0 if the input capability did not have a tag set, the output capability has more permissions or larger bounds compared to the input capability, or the operation results in a capability with malformed bounds. These instructions do not give rise to exceptions.

- **CSETADDR**: set the address of a capability to an arbitrary address

- **CINCOFFSET**, **CINCOFFSETIMM**: increment the address of the input capability by an arbitrary offset

- **CSETHIGH**: replace a capability's metadata with an arbitrary value. The output tag is always 0

- **CANDPERM**: bitwise AND of a mask value with a bit map representation of the architectural (AP)

and software-defined (SDP) permissions fields

- **CSETBOUNDS**: set the base and length of a capability. The tag is cleared, if the encoding cannot represent the bounds exactly

- **CSETBOUNDSINEXACT**: set the base and length of a capability. The base will be rounded down and/or the length will be rounded up if the encoding cannot represent the bounds exactly

- **CSEAL**: seal capability

- **CBUILDCAP**: replace the base, top, address, permissions and mode fields of a capability with the fields from another capability

- **CMOVE**: move a capability from a **c** register to another **c** register

*CBUILDCAP outputs a capability with tag set to 0 if the input capability's bounds are malformed.*

**CHERI v9 Note:** **CSETBOUNDS** and **CSETBOUNDSIMM** perform the role of the old **CSETBOUNDSINEXACT** while the new **CSETBOUNDSINEXACT** is the old **CSETBOUNDS**.

### 3.3.3. Capability Load and Store Instructions

A load capability instruction, **CLC**, reads CLEN bits from memory together with its tag and writes the result to a **c** register. The capability authorising the memory access is provided in a **c** source register, so the effective address is obtained by incrementing that capability with the sign-extended 12-bit offset.

A store capability instruction, **CSC**, writes CLEN bits and the tag in a **c** register to memory. The capability authorising the memory access is provided in a **c** source register, so the effective address is obtained by incrementing that capability with the sign-extended 12-bit offset.

**CLC** and **CSC** instructions cause CHERI exceptions if the authorising capability fails any of the following checks:

- The tag is zero

- The capability is sealed

- At least one byte of the memory access is outside the capability's bounds

- For loads, the read permission must be set in AP

- For stores, the write permission must be set in AP

Capability load and store instructions also cause load or store/AMO address misaligned exceptions if the address is not naturally aligned to a CLEN boundary.

For loads, the tag of the capability loaded from memory is cleared if the authorising capability does not grant permission to read capabilities (i.e. both **R-permission** and **G-permission** must be set in AP). For stores, the tag of the capability written to memory is cleared if the authorising capability does not grant permission to write capabilities (i.e. both **W-permission** and **C-permission** must be set in AP).

*TODO: these cases may cause exceptions in the future - we need a way for software to discover and/or control the behaviour*

### 3.3.4. Unconditional Integer Address Jumps

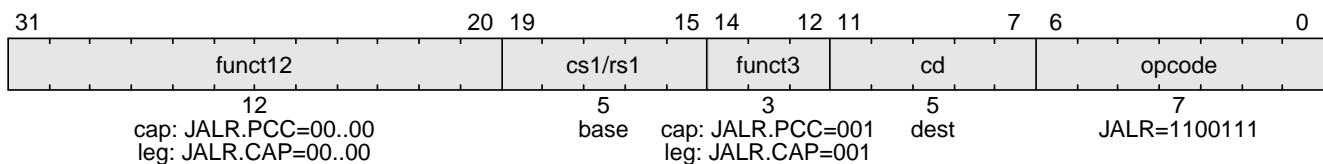

The indirect jump and link [pcc \(JALR.PCC\)](#) instruction allows unconditional jumps to a target address. The target address is provided in an **x** register; the new address is installed in the address field of the [pcc](#). The address of the instruction following the jump ([pc + 4](#)) is written to an **x** register. [JALR.PCC](#) causes an exceptions when a minimum sized instruction at the target address is not within the bounds of the [pcc](#) or the target address is misaligned.

**CHERI v9 Note:** *This instruction is now modal and shares the same encoding with [JALR.CAP](#) when both `Zcheri_purecap` and `Zcheri_legacy` are supported.*

## 3.4. Existing RISC-V Instructions

The operands or behavior of some instructions in the base RISC-V ISA changes in `Zcheri_purecap`.

### 3.4.1. Integer Computational Instructions

Most integer computational instructions operate on XLEN bits of values held in **x** registers. Therefore, these instructions only operate on the address field if the input register of the instruction holds a capability. The output is XLEN bits written to an **x** register; the tag and capability metadata of that register are zeroed.

The add upper immediate to [pcc](#) instruction ([AUIPCC](#)) replaces the add upper immediate to [pc](#) instruction ([AUIPC](#)) at the same encoding. [AUIPCC](#) is used to build [pcc](#)-relative capabilities. [AUIPCC](#) forms a 32-bit offset from the 20-bit immediate and filling the lowest 12 bits with zeros. The [pcc](#) address is then incremented by the offset and a representability check is performed so the capability's tag is cleared if the new address is outside the [pcc](#)'s representable region. The resulting CLEN value along with the new tag are written to a **c** register.

### 3.4.2. Control Transfer Instructions

Control transfer instructions operate as described in the base RISC-V ISA. They also may cause metadata updates and/or cause exceptions in addition to the base behaviour as described below.

#### Unconditional Jumps

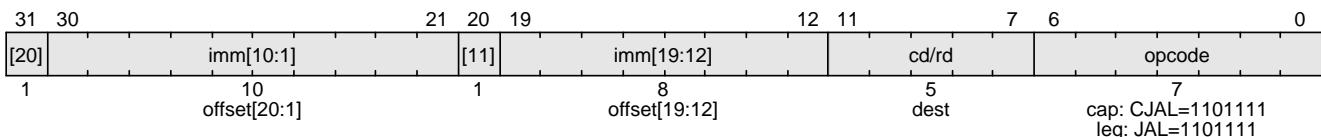

The capability jump and link ([CJAL](#)) instruction replaces jump and link ([JAL](#)) at the same encoding. [CJAL](#) sign-extends the offset and adds it to the address of the jump instruction to form the target address. The target address is installed in the address field of [pcc](#). The capability with the address of the instruction following the jump ([pcc + 4](#)) is written to a **c** register.

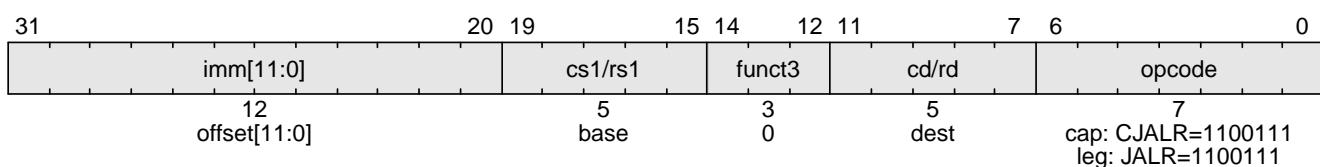

The capability jump and link register ([CJALR](#)) instruction replaces the jump and link register ([JALR](#)) instruction at the same encoding. This instruction allows unconditional jumps to a target capability. The target capability is obtained by incrementing the capability in the **c** register operand by the sign-extended 12-bit immediate, then setting the least significant bit of the result to zero. The capability with the address of the instruction following the jump ([pcc + 4](#)) is written to a **c** register.

All jumps cause CHERI exceptions when a minimum sized instruction at the target address is not within the bounds of the [pcc](#).

[CJALR](#) causes a CHERI exception when:

- The target capability's tag is zero

- A minimum sized instruction at the target capability's address is not within bounds

- The target capability does not grant execute permission

[CJAL](#) and [CJALR](#) can also cause instruction address misaligned exceptions following the standard RISC-V rules for [JAL](#) and [JALR](#).

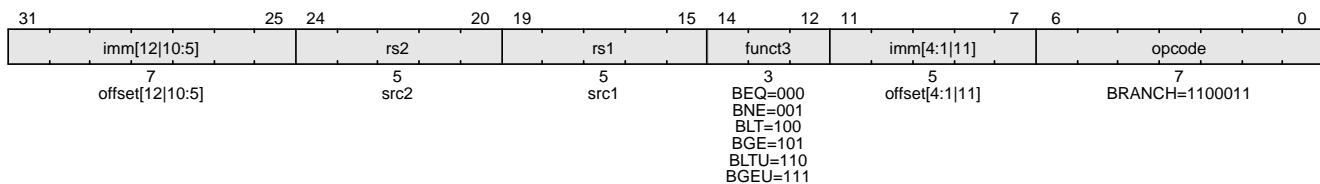

## Conditional Branches

Branch instructions (see [Conditional branches \(BEQ, BNE, BLT\[U\], BGE\[U\]\)](#)) encode signed offsets in multiples of 2 bytes. The offset is sign-extended and added to the address of the branch instruction to form the target address.

Branch instructions compare two **x** registers as described in the base RISC-V ISA, so the metadata and tag values are disregarded in the comparison if the operand registers hold capabilities. If the comparison evaluates to true, then the target address is installed in the [pcc](#)'s address field. These instructions cause CHERI exceptions when a minimum sized instruction at the target address is not within the [pcc](#)'s bounds.

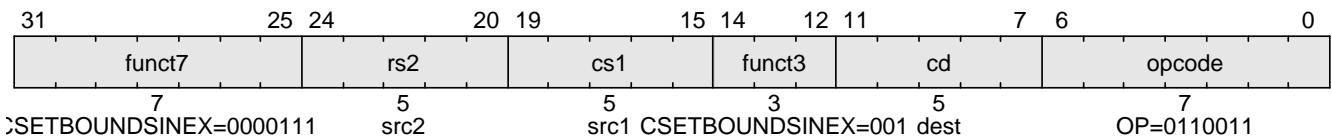

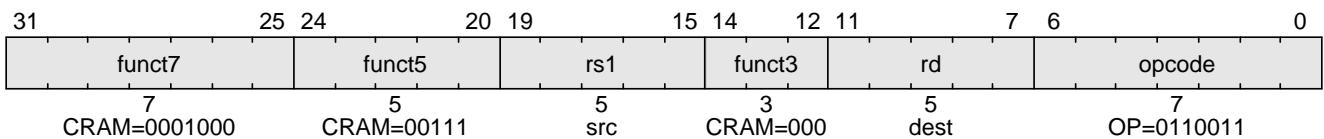

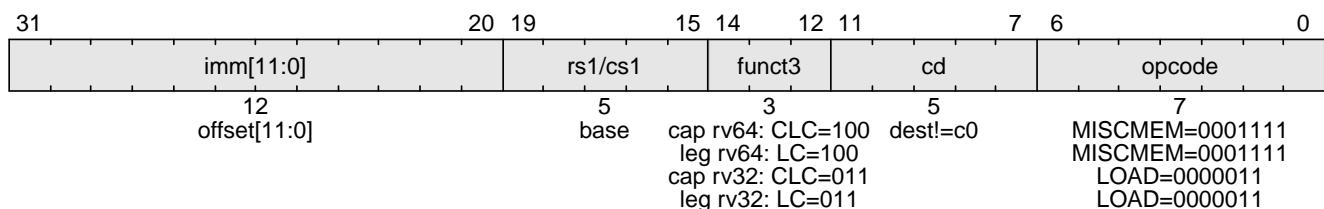

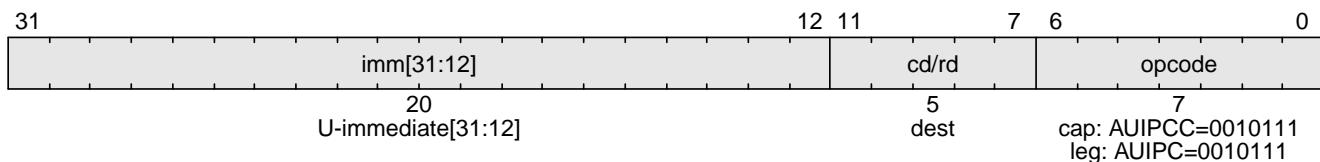

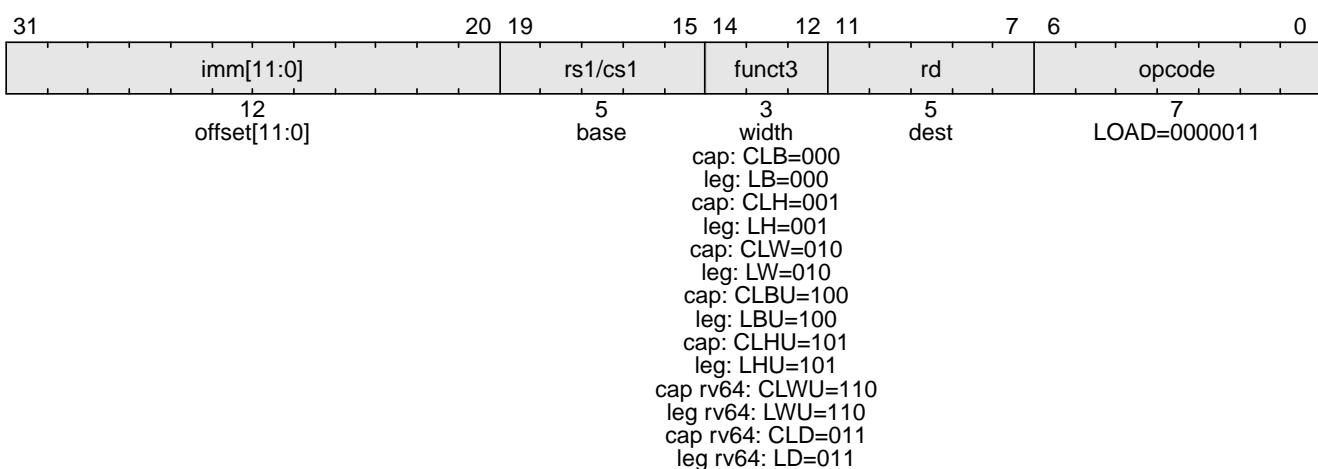

### 3.4.3. Integer Load and Store Instructions