# RISC-V Specification for CHERI Extensions

Authors: Thomas Aird, Hesham Almatary, Andres Amaya Garcia, John Baldwin, Paul Buxton, David Chisnall, Jessica Clarke, Brooks Davis, Nathaniel Wesley Filardo, Franz A. Fuchs, Timothy Hutt, Alexandre Joannou, Martin Kaiser, Tariq Kurd, Ben Laurie, Marno van der Maas, Maja Malenko, A. Theodore Markettos, David McKay, Jamie Melling, Stuart Menefy, Simon W. Moore, Peter G. Neumann, Robert Norton, Alexander Richardson, Michael Roe, Peter Rugg, Peter Sewell, Carl Shaw, Ricki Tura, Robert N. M. Watson, Toby Wenman, Jonathan Woodruff, Jason Zhijingcheng Yu

Version v0.9.3, 2025-01-16: Draft

# Table of Contents

|                                                                                        |           |

|----------------------------------------------------------------------------------------|-----------|

| <b>Preamble</b> .....                                                                  | <b>1</b>  |

| <b>Copyright and license information</b> .....                                         | <b>2</b>  |

| <b>Contributors</b> .....                                                              | <b>3</b>  |

| <b>1. Quick Start</b> .....                                                            | <b>5</b>  |

| 1.1. Capability Properties .....                                                       | 5         |

| 1.2. Added State .....                                                                 | 5         |

| 1.3. Checking Memory .....                                                             | 6         |

| 1.4. Added Instructions .....                                                          | 6         |

| 1.5. Existing Instructions .....                                                       | 6         |

| <b>2. Introduction</b> .....                                                           | <b>7</b>  |

| 2.1. CHERI Concepts and Terminology .....                                              | 7         |

| 2.2. CHERI Extensions to RISC-V .....                                                  | 8         |

| 2.3. Risks and Known Uncertainty .....                                                 | 9         |

| 2.3.1. Partially Incompatible Extensions .....                                         | 9         |

| <b>3. Anatomy of Capabilities in Zcheripurecap</b> .....                               | <b>10</b> |

| 3.1. Capability Encoding .....                                                         | 10        |

| 3.2. Components of a Capability .....                                                  | 11        |

| 3.2.1. Tag .....                                                                       | 11        |

| 3.2.2. Address .....                                                                   | 11        |

| 3.2.3. Architectural Permissions (AP) .....                                            | 11        |

| Description .....                                                                      | 11        |

| Permission Encoding .....                                                              | 12        |

| Permission Transitions .....                                                           | 16        |

| 3.2.4. Software-Defined Permissions (SDP) .....                                        | 16        |

| 3.2.5. Capability Type (CT) Bit .....                                                  | 16        |

| 3.2.6. Bounds (EF, T, TE, B, BE) .....                                                 | 17        |

| Concept .....                                                                          | 17        |

| Decoding .....                                                                         | 18        |

| Malformed Capability Bounds .....                                                      | 20        |

| 3.3. Special Capabilities .....                                                        | 21        |

| 3.3.1. NULL Capability .....                                                           | 21        |

| 3.3.2. Infinite Capability .....                                                       | 22        |

| 3.4. Representable Range Check .....                                                   | 23        |

| 3.4.1. Concept .....                                                                   | 23        |

| 3.4.2. Practical Information .....                                                     | 23        |

| <b>4. Integrating Zcheripurecap with the RISC-V Base Integer Instruction Set</b> ..... | <b>25</b> |

| 4.1. Memory .....                                                                      | 25        |

| 4.2. Programmer's Model for Zcheripurecap .....                                        | 25        |

| 4.2.1. PCC - The Program Counter Capability .....                                      | 26        |

| 4.3. Capability Instructions .....                                                     | 26        |

| 4.3.1. Capability Inspection Instructions .....                                        | 26        |

|                                                                               |    |

|-------------------------------------------------------------------------------|----|

| 4.3.2. Capability Manipulation Instructions .....                             | 27 |

| 4.3.3. Capability Load and Store Instructions .....                           | 27 |

| 4.4. Existing RISC-V Instructions .....                                       | 28 |

| 4.4.1. Integer Computational Instructions .....                               | 28 |

| 4.4.2. Control Transfer Instructions .....                                    | 29 |

| Unconditional Jumps .....                                                     | 29 |

| Conditional Branches .....                                                    | 29 |

| 4.4.3. Integer Load and Store Instructions .....                              | 29 |

| 4.5. Zicsr, Control and Status Register (CSR) Instructions .....              | 30 |

| 4.5.1. CSR Instructions .....                                                 | 30 |

| 4.6. Control and Status Registers (CSRs) .....                                | 31 |

| 4.7. Machine-Level CSRs .....                                                 | 32 |

| 4.7.1. Machine Status Registers (mstatus and mstatush) .....                  | 32 |

| 4.7.2. Machine Trap Vector Base Address Register (mtvec) .....                | 32 |

| 4.7.3. Machine Trap Vector Base Address Capability Register (mtvecc) .....    | 32 |

| 4.7.4. Machine Scratch Register (mscratch) .....                              | 33 |

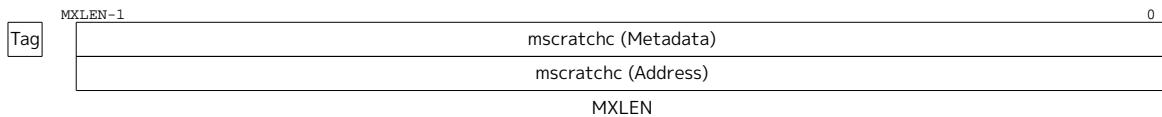

| 4.7.5. Machine Scratch Capability Register (mscratchc) .....                  | 33 |

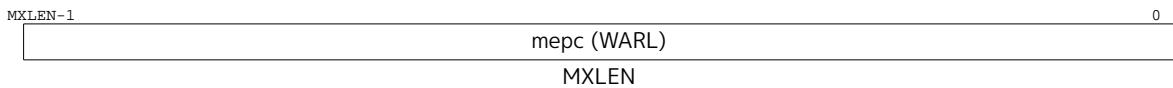

| 4.7.6. Machine Exception Program Counter (mepc) .....                         | 34 |

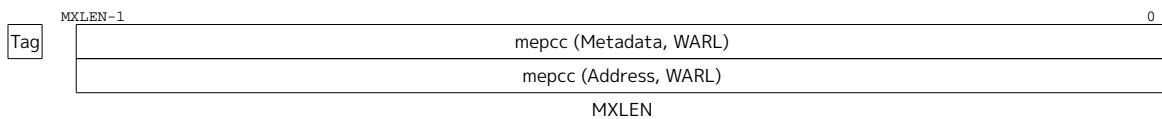

| 4.7.7. Machine Exception Program Counter Capability (mepcc) .....             | 34 |

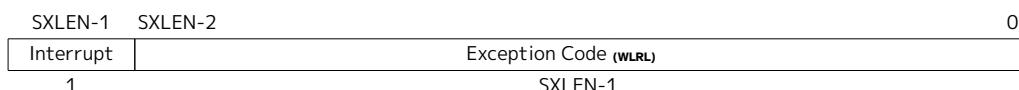

| 4.7.8. Machine Cause Register (mcause) .....                                  | 34 |

| 4.7.9. Machine Trap Delegation Register (medeleg) .....                       | 37 |

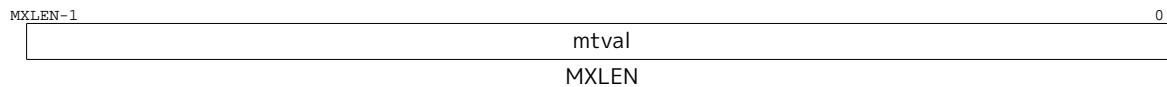

| 4.7.10. Machine Trap Value Register (mtval) .....                             | 37 |

| 4.7.11. Machine Trap Value Register 2 (mtval2) .....                          | 37 |

| mtval2 values for CHERI faults .....                                          | 37 |

| mtval2 values for Load/Store/AMO Page Faults .....                            | 38 |

| 4.8. Supervisor-Level CSRs .....                                              | 38 |

| 4.8.1. Supervisor Trap Vector Base Address Register (stvec) .....             | 38 |

| 4.8.2. Supervisor Trap Vector Base Address Capability Register (stvecc) ..... | 39 |

| 4.8.3. Supervisor Scratch Register (sscratch) .....                           | 39 |

| 4.8.4. Supervisor Scratch Capability Register (sscratchc) .....               | 39 |

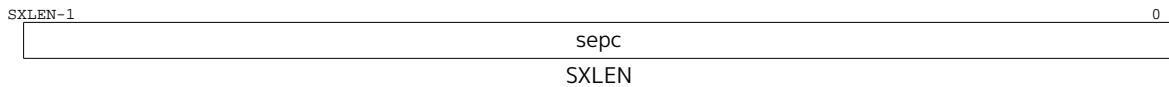

| 4.8.5. Supervisor Exception Program Counter (sepc) .....                      | 40 |

| 4.8.6. Supervisor Exception Program Counter Capability (sepcc) .....          | 40 |

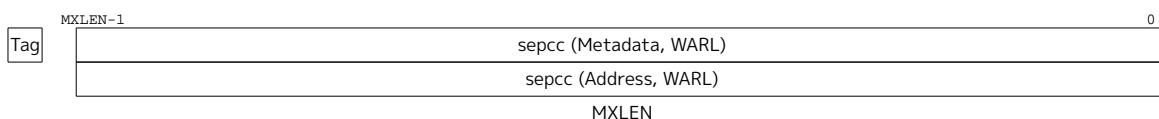

| 4.8.7. Supervisor Cause Register (scause) .....                               | 40 |

| 4.8.8. Supervisor Trap Value Register (stval) .....                           | 41 |

| 4.8.9. Supervisor Trap Value Register 2 (stval2) .....                        | 41 |

| 4.9. Unprivileged CSRs .....                                                  | 41 |

| 4.10. CHERI Exception handling .....                                          | 42 |

| 4.11. CHERI Exceptions and speculative execution .....                        | 43 |

| 4.12. Physical Memory Attributes (PMA) .....                                  | 44 |

| 4.13. Page-Based Virtual-Memory Systems .....                                 | 44 |

| 4.13.1. Invalid Address Handling .....                                        | 44 |

| Updating CSRs .....                                                           | 45 |

| Branches and Jumps .....                                                      | 45 |

|                                                                                                          |           |

|----------------------------------------------------------------------------------------------------------|-----------|

| Memory Accesses .....                                                                                    | 46        |

| 4.14. Integrating Zcheripurecap with Sdext.....                                                          | 46        |

| 4.14.1. Debug Mode .....                                                                                 | 47        |

| 4.14.2. Core Debug Registers .....                                                                       | 47        |

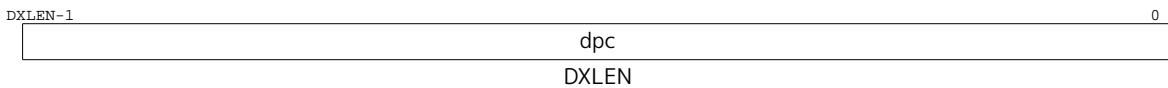

| 4.14.3. Debug Program Counter (dpc) .....                                                                | 47        |

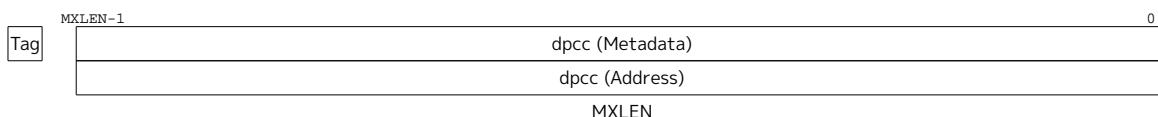

| 4.14.4. Debug Program Counter Capability (dpcc) .....                                                    | 48        |

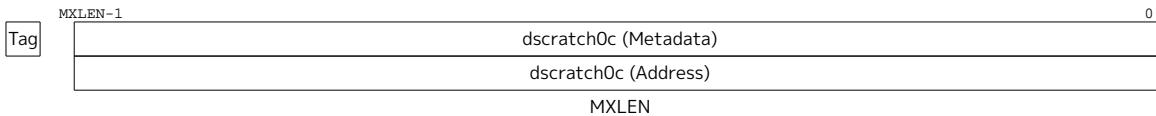

| 4.14.5. Debug Scratch Register 0 (dscratch0).....                                                        | 48        |

| 4.14.6. Debug Scratch Register 0 Capability (dscratch0c).....                                            | 48        |

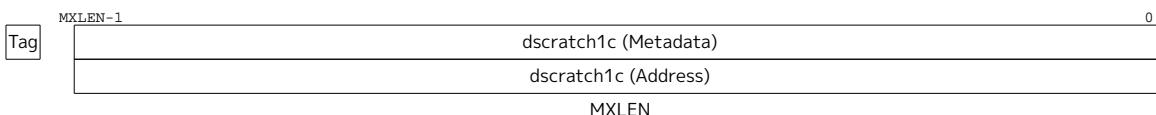

| 4.14.7. Debug Scratch Register 1 (dscratch1) .....                                                       | 49        |

| 4.14.8. Debug Scratch Register 1 Capability (dscratch1c) .....                                           | 49        |

| 4.14.9. Debug Infinite Capability Register (dinf0) .....                                                 | 49        |

| 4.15. Integrating Zcheripurecap with Sdtrig .....                                                        | 50        |

| <b>5. Extending Page-Based Virtual-Memory Systems for CHERI (RV64 only), including "Zcheripte" .....</b> | <b>52</b> |

| 5.1. Limiting Capability Propagation .....                                                               | 52        |

| 5.2. Capability Revocation.....                                                                          | 53        |

| 5.3. Extending the Page Table Entry Format .....                                                         | 53        |

| 5.4. Enabling Software or Hardware PTE updates .....                                                     | 55        |

| 5.5. Extending the Supervisor (sstatus) and Virtual Supervisor (vsstatus) Status Registers .....         | 55        |

| <b>6. "Zcherilevels" Extension for Capability Levels .....</b>                                           | <b>57</b> |

| 6.1. Capability format changes .....                                                                     | 57        |

| 6.1.1. Capability Level (CL) .....                                                                       | 57        |

| 6.1.2. New capability permissions .....                                                                  | 57        |

| 6.2. Changing capability levels and permissions .....                                                    | 59        |

| 6.3. Capability level summary table .....                                                                | 60        |

| 6.4. Extending Zcherilevels to more than two levels .....                                                | 60        |

| <b>7. "Zcherihybrid" Extension for CHERI Integer Pointer Mode .....</b>                                  | <b>61</b> |

| 7.1. CHERI Execution Mode .....                                                                          | 61        |

| 7.2. CHERI Execution Mode Encoding .....                                                                 | 61        |

| 7.2.1. Observing the CHERI Execution Mode .....                                                          | 62        |

| 7.3. Zcherihybrid Instructions .....                                                                     | 62        |

| 7.3.1. Capability Load and Store Instructions .....                                                      | 63        |

| 7.3.2. Capability Manipulation Instructions .....                                                        | 63        |

| 7.3.3. Mode Change Instructions .....                                                                    | 63        |

| 7.4. Existing RISC-V Instructions .....                                                                  | 63        |

| 7.4.1. Control Transfer Instructions .....                                                               | 63        |

| 7.4.2. Conditional Branches .....                                                                        | 64        |

| 7.4.3. Load and Store Instructions .....                                                                 | 64        |

| 7.4.4. CSR Instructions .....                                                                            | 64        |

| 7.5. Integrating Zcherihybrid with Sdext .....                                                           | 65        |

| 7.6. Debug Default Data Capability (dddc) .....                                                          | 65        |

| 7.7. Disabling CHERI Registers and Instructions .....                                                    | 66        |

| 7.8. Added CLEN-wide CSRs .....                                                                          | 67        |

|                                                                                          |           |

|------------------------------------------------------------------------------------------|-----------|

| 7.8.1. Machine Status Registers (mstatus and mstatush) .....                             | 67        |

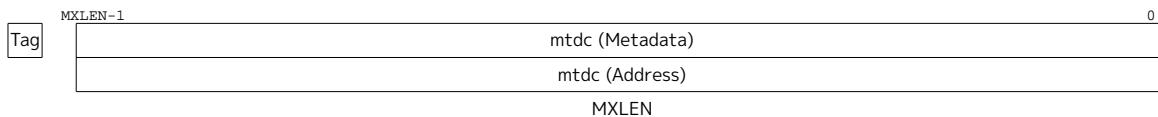

| 7.8.2. Machine Trap Default Capability Register (mtdc) .....                             | 68        |

| 7.8.3. Machine Security Configuration Register (mseccfg) .....                           | 68        |

| 7.8.4. Machine Environment Configuration Register (menvcfg) .....                        | 68        |

| 7.8.5. Supervisor Trap Default Capability Register (stdc) .....                          | 69        |

| 7.8.6. Supervisor Environment Configuration Register (senvcfg) .....                     | 69        |

| 7.8.7. Default Data Capability (ddc) .....                                               | 69        |

| <b>8. Integrating Zcheripurecap and Zcherihybrid with the Hypervisor Extension</b> ..... | <b>71</b> |

| 8.1. Hypervisor Status Register (hstatus) .....                                          | 71        |

| 8.2. Hypervisor Environment Configuration Register (henvcfg) .....                       | 71        |

| 8.3. Hypervisor Exception Delegation Register (hdeleg) .....                             | 71        |

| 8.4. Virtual Supervisor Status Register (vsstatus) .....                                 | 72        |

| 8.5. Virtual Supervisor Trap Vector Base Address Register (vstvec) .....                 | 72        |

| 8.6. Virtual Supervisor Trap Vector Base Address Capability Register (vstvecc) .....     | 72        |

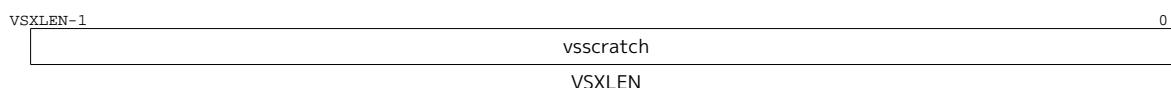

| 8.7. Virtual Supervisor Scratch Register (vsscratch) .....                               | 72        |

| 8.8. Virtual Supervisor Scratch Register (vsscratchc) .....                              | 72        |

| 8.9. Virtual Supervisor Exception Program Counter (vsepc) .....                          | 73        |

| 8.10. Virtual Supervisor Exception Program Counter Capability (vsepcc) .....             | 73        |

| 8.11. Virtual Supervisor Cause Register (vscause) .....                                  | 73        |

| 8.12. Virtual Supervisor Trap Default Capability Register (vstdc) .....                  | 73        |

| 8.13. Virtual Supervisor Trap Value Register (vstval) .....                              | 74        |

| 8.14. Virtual Supervisor Trap Value Register 2 (vstval2) .....                           | 74        |

| 8.15. Existing Hypervisor Load and Store Instructions .....                              | 74        |

| 8.16. Hypervisor Load and Store Capability Instructions .....                            | 74        |

| <b>9. Integrating Zcheripurecap and Zcherihybrid with the Vector Extension</b> .....     | <b>76</b> |

| <b>10. Integrating Zcheripurecap and Zcherihybrid with Pointer Masking</b> .....         | <b>77</b> |

| <b>11. "Ztid" Extension for Software Thread Identification</b> .....                     | <b>78</b> |

| 11.1. Control and Status Registers (CSRs) .....                                          | 78        |

| 11.2. Machine-Level, Supervisor-Level and Unprivileged CSRs .....                        | 78        |

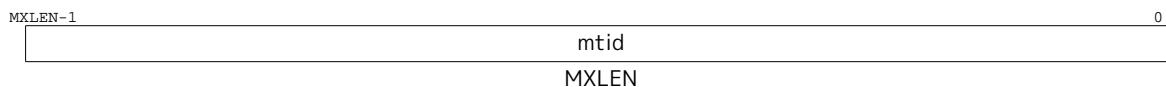

| 11.2.1. Machine Thread Identifier (mtid) .....                                           | 78        |

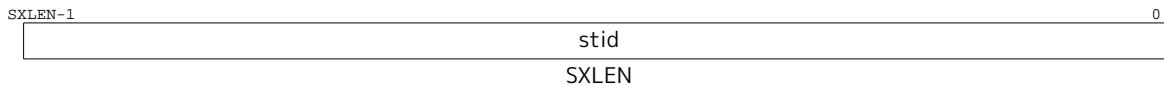

| 11.2.2. Supervisor Thread Identifier (stid) .....                                        | 78        |

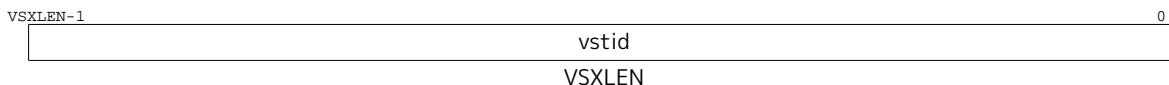

| 11.2.3. Virtual Supervisor Thread Identifier (vstid) .....                               | 79        |

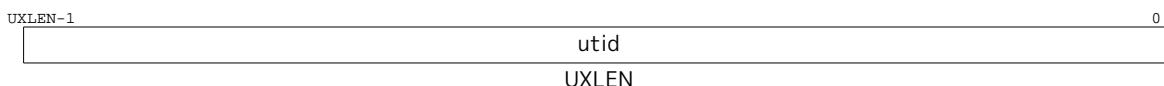

| 11.2.4. User Thread Identifier (utid) .....                                              | 79        |

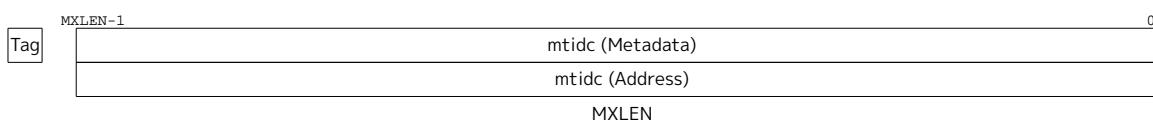

| 11.2.5. Machine Thread Identifier Capability (mtidc) .....                               | 79        |

| 11.2.6. Supervisor Thread Identifier Capability (stidc) .....                            | 79        |

| 11.2.7. Virtual Supervisor Thread Identifier Capability (vstidc) .....                   | 80        |

| 11.2.8. User Thread Identifier Capability (utidc) .....                                  | 80        |

| 11.3. "Smstateen/Ssstateen" Integration .....                                            | 80        |

| 11.4. CHERI Compartmentalization .....                                                   | 81        |

| <b>12. RISC-V Instructions and Extensions Reference</b> .....                            | <b>82</b> |

| 12.1. "Zcheripurecap" and "Zcherihybrid" Extensions for CHERI .....                      | 83        |

| 12.1.1. CMV .....                                                                        | 84        |

| 12.1.2. MODESW.INT .....                                                                 | 85        |

|                                                               |     |

|---------------------------------------------------------------|-----|

| 12.1.3. MODESW.CAP .....                                      | 85  |

| 12.1.4. CADDI .....                                           | 87  |

| 12.1.5. CADD .....                                            | 87  |

| 12.1.6. SCADDR .....                                          | 89  |

| 12.1.7. ACPERM .....                                          | 90  |

| 12.1.8. SCMODE .....                                          | 93  |

| 12.1.9. SCHI .....                                            | 94  |

| 12.1.10. SCEQ .....                                           | 95  |

| 12.1.11. SENTRY .....                                         | 96  |

| 12.1.12. SCSS .....                                           | 97  |

| 12.1.13. CBLD .....                                           | 98  |

| 12.1.14. GCTAG .....                                          | 100 |

| 12.1.15. GCPERM .....                                         | 101 |

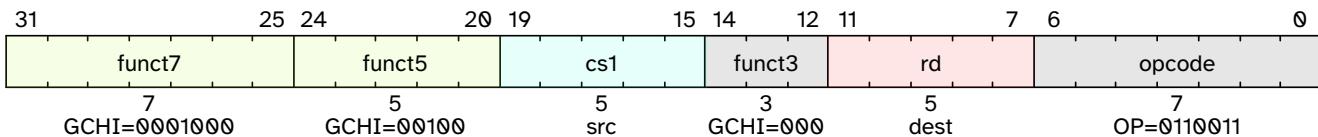

| 12.1.16. GCHI .....                                           | 102 |

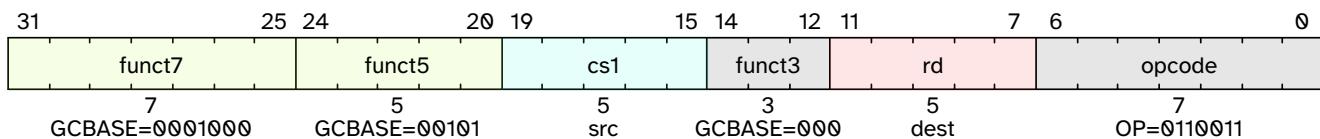

| 12.1.17. GCBASE .....                                         | 103 |

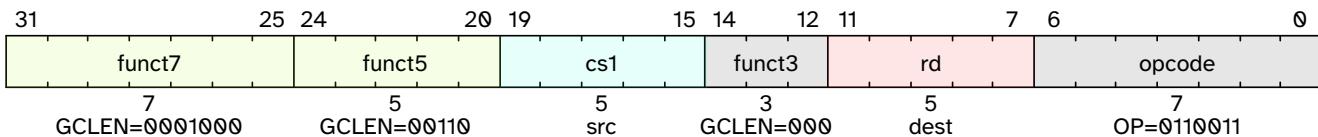

| 12.1.18. GCLEN .....                                          | 104 |

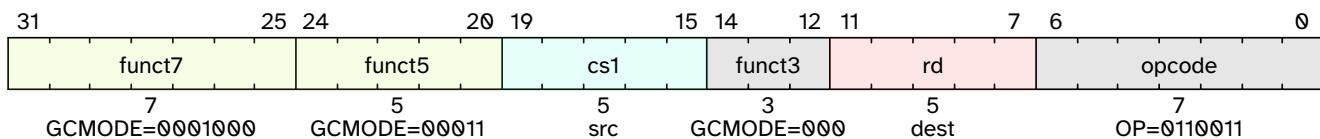

| 12.1.19. GCMODE .....                                         | 105 |

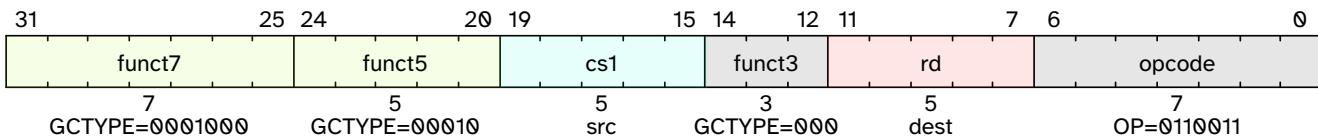

| 12.1.20. GCTYPE .....                                         | 106 |

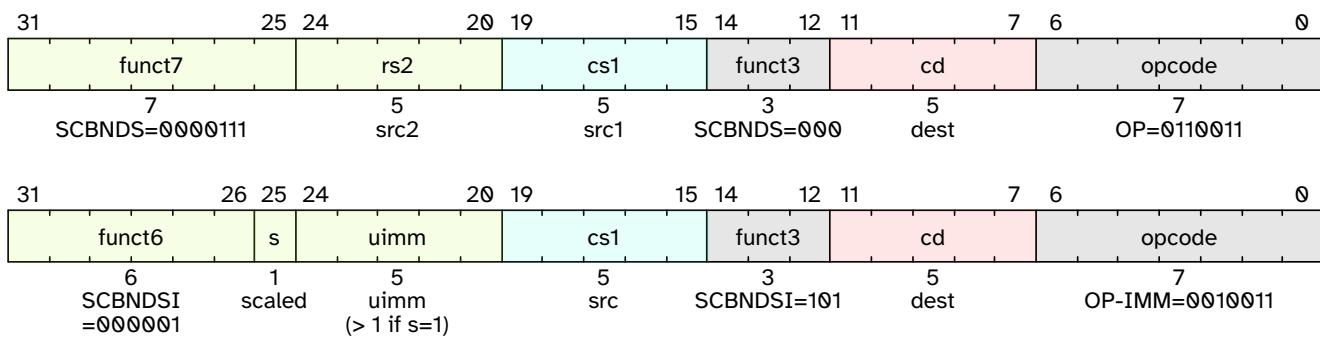

| 12.1.21. SCBNDSI .....                                        | 107 |

| 12.1.22. SCBNDS .....                                         | 107 |

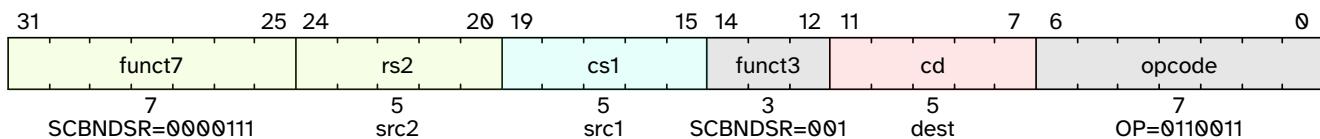

| 12.1.23. SCBNDSR .....                                        | 109 |

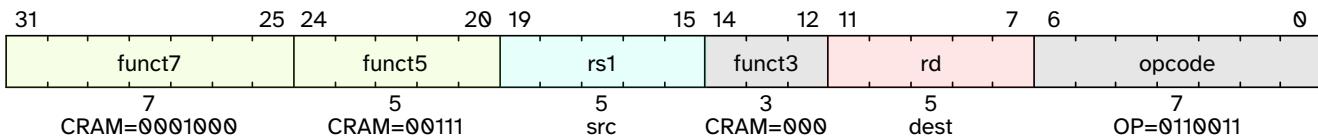

| 12.1.24. CRAM .....                                           | 110 |

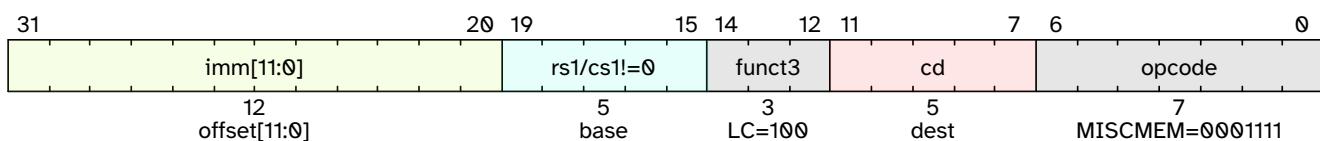

| 12.1.25. LC .....                                             | 111 |

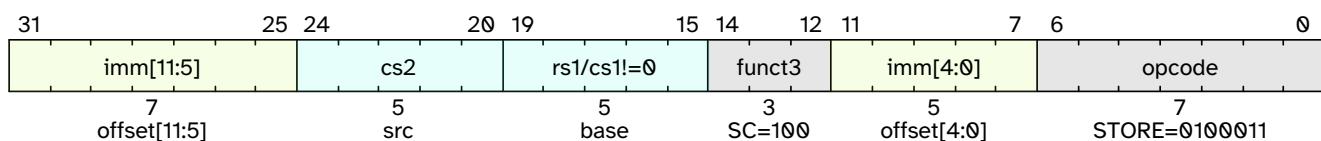

| 12.1.26. SC .....                                             | 113 |

| 12.2. RV32I/E and RV64I/E Base Integer Instruction Sets ..... | 115 |

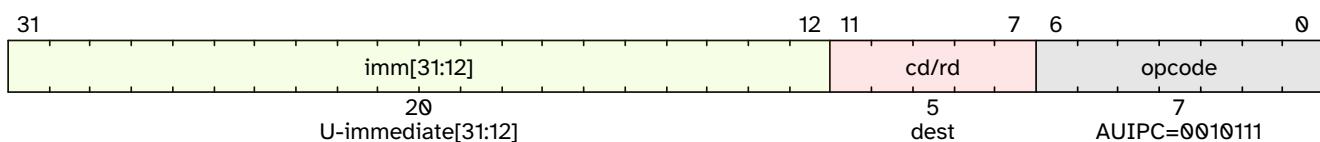

| 12.2.1. AUIPC .....                                           | 116 |

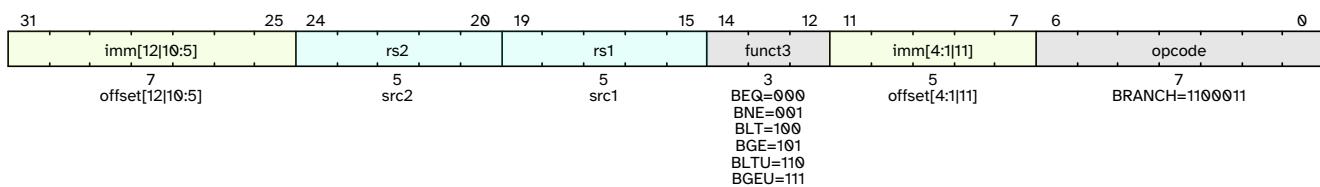

| 12.2.2. BEQ, BNE, BLT[U], BGE[U] .....                        | 117 |

| 12.2.3. JR .....                                              | 118 |

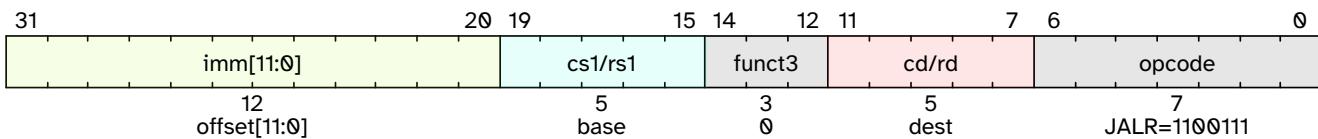

| 12.2.4. JALR .....                                            | 118 |

| 12.2.5. J .....                                               | 121 |

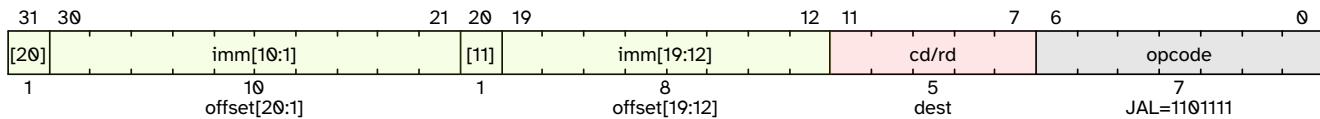

| 12.2.6. JAL .....                                             | 121 |

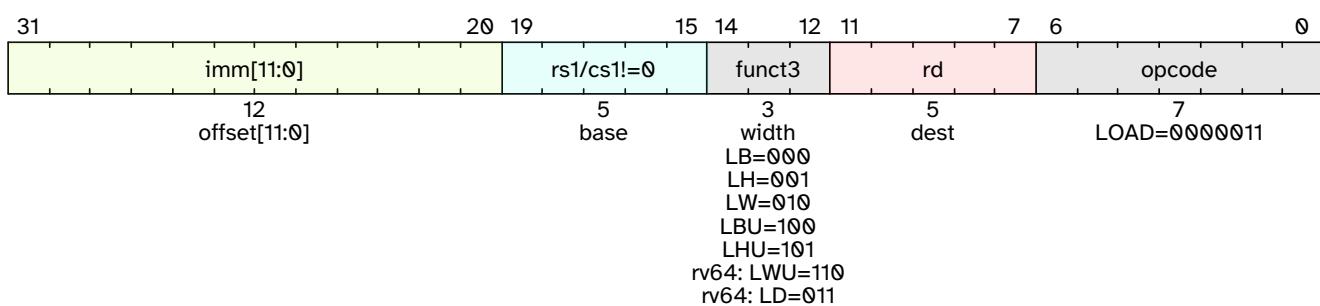

| 12.2.7. LD .....                                              | 123 |

| 12.2.8. LWU .....                                             | 123 |

| 12.2.9. LW .....                                              | 123 |

| 12.2.10. LHU .....                                            | 123 |

| 12.2.11. LH .....                                             | 123 |

| 12.2.12. LBU .....                                            | 123 |

| 12.2.13. LB .....                                             | 124 |

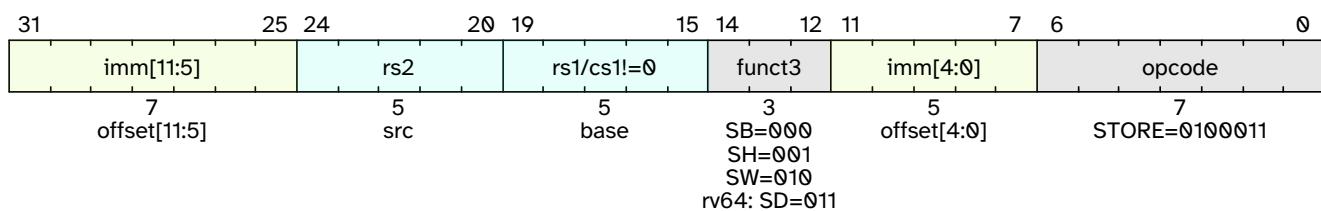

| 12.2.14. SD .....                                             | 126 |

| 12.2.15. SW .....                                             | 126 |

| 12.2.16. SH .....                                             | 126 |

| 12.2.17. SB .....                                             | 127 |

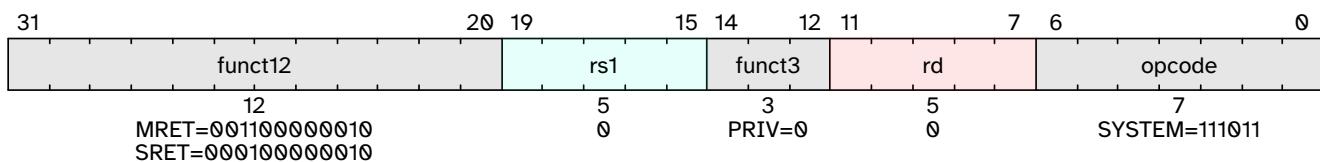

| 12.2.18. SRET .....                                           | 129 |

|                                                                                |     |

|--------------------------------------------------------------------------------|-----|

| 12.2.19. MRET .....                                                            | 129 |

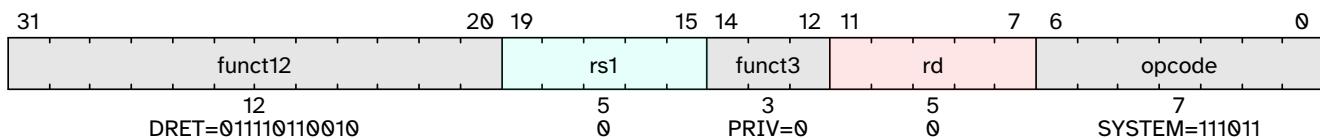

| 12.2.20. DRET .....                                                            | 130 |

| 12.3. "A" Standard Extension for Atomic Instructions .....                     | 131 |

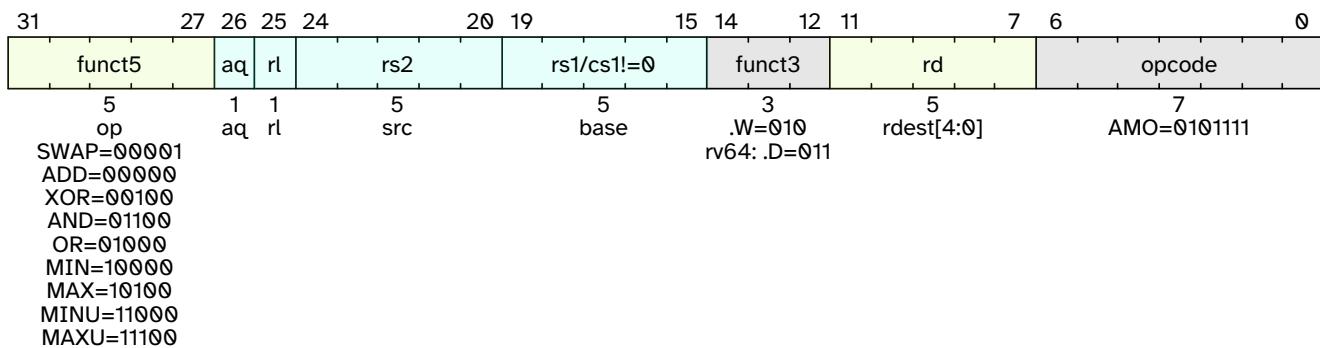

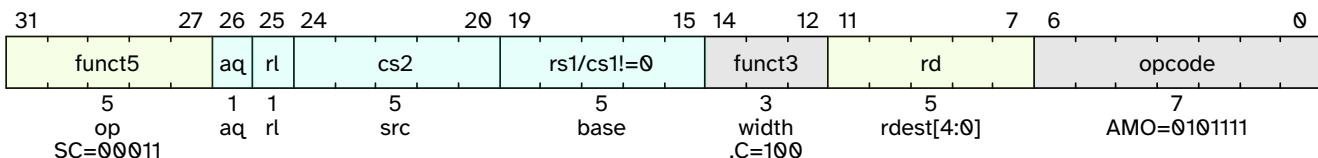

| 12.3.1. AMO<OP>.W .....                                                        | 132 |

| 12.3.2. AMO<OP>.D .....                                                        | 133 |

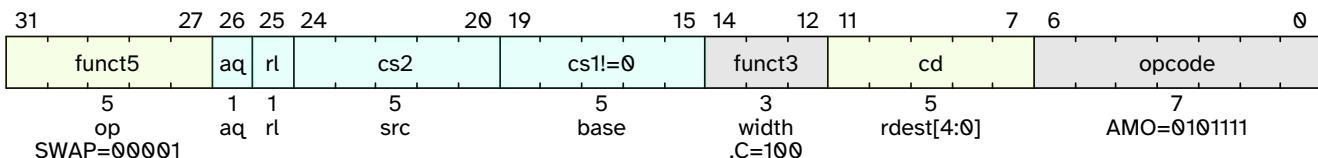

| 12.3.3. AMOSWAP.C .....                                                        | 135 |

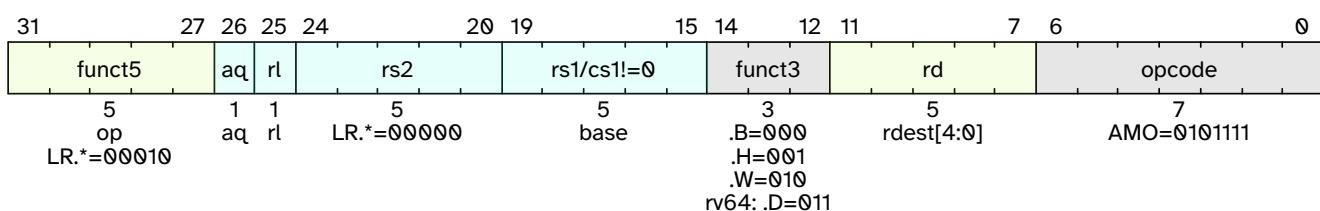

| 12.3.4. LR.D .....                                                             | 138 |

| 12.3.5. LR.W .....                                                             | 138 |

| 12.3.6. LR.H .....                                                             | 138 |

| 12.3.7. LR.B .....                                                             | 139 |

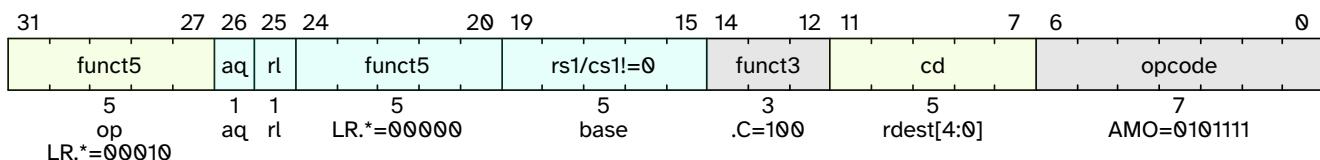

| 12.3.8. LR.C .....                                                             | 141 |

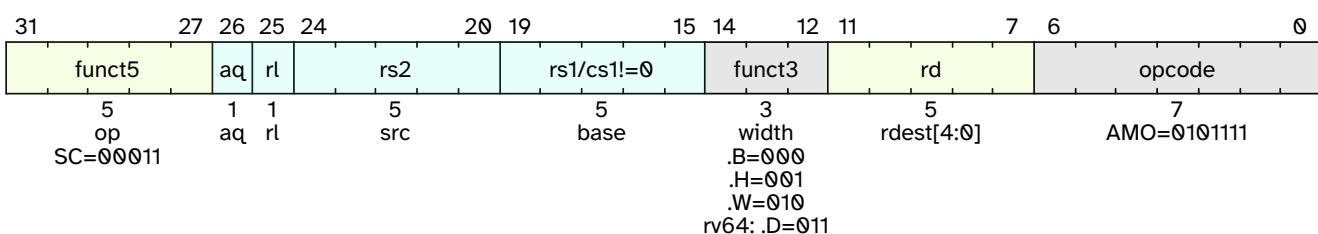

| 12.3.9. SC.D .....                                                             | 143 |

| 12.3.10. SC.W .....                                                            | 143 |

| 12.3.11. SC.H .....                                                            | 143 |

| 12.3.12. SC.B .....                                                            | 144 |

| 12.3.13. SC.C .....                                                            | 146 |

| 12.4. "Zicsr", Control and Status Register (CSR) Instructions .....            | 148 |

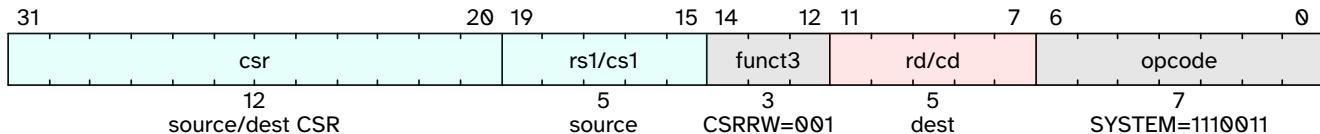

| 12.4.1. CSRRW .....                                                            | 149 |

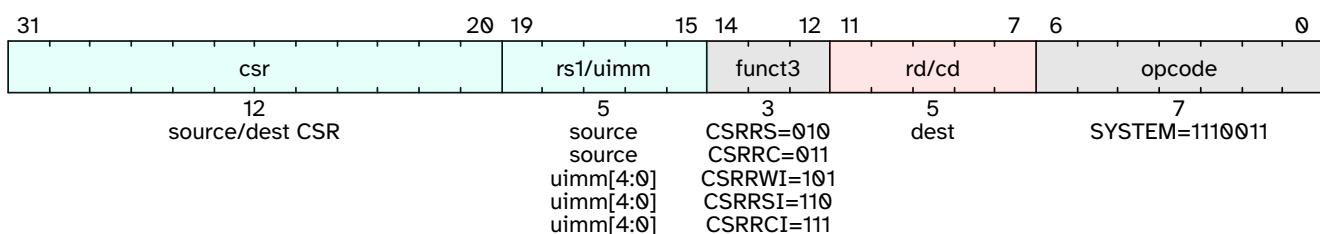

| 12.4.2. CSRRWI .....                                                           | 151 |

| 12.4.3. CSRRS .....                                                            | 151 |

| 12.4.4. CSRRSI .....                                                           | 151 |

| 12.4.5. CSRRC .....                                                            | 151 |

| 12.4.6. CSRRCI .....                                                           | 152 |

| 12.5. "Zfh", "Zfhmin", "F" and "D" Standard Extension for Floating-Point ..... | 154 |

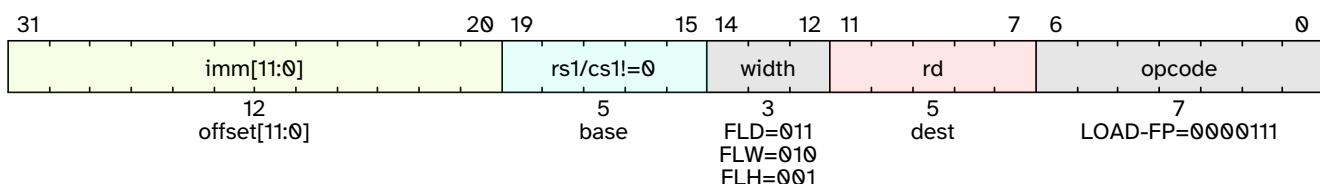

| 12.5.1. FLD .....                                                              | 155 |

| 12.5.2. FLW .....                                                              | 155 |

| 12.5.3. FLH .....                                                              | 156 |

| 12.5.4. FSD .....                                                              | 158 |

| 12.5.5. FSW .....                                                              | 158 |

| 12.5.6. FSH .....                                                              | 159 |

| 12.6. "C" Standard Extension for Compressed Instructions .....                 | 161 |

| 12.6.1. RV32 .....                                                             | 161 |

| 12.6.2. RV64 .....                                                             | 162 |

| 12.6.3. C.BEQZ, C.BNEZ .....                                                   | 163 |

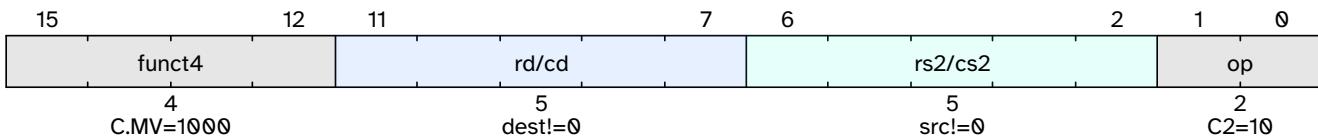

| 12.6.4. C.MV .....                                                             | 164 |

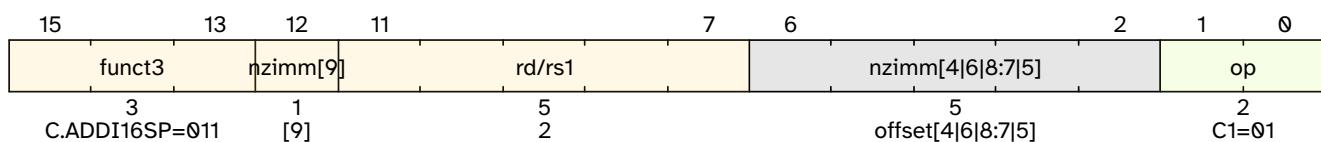

| 12.6.5. C.ADDI16SP .....                                                       | 165 |

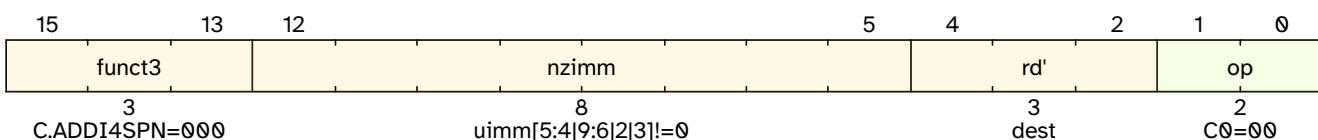

| 12.6.6. C.ADDI4SPN .....                                                       | 166 |

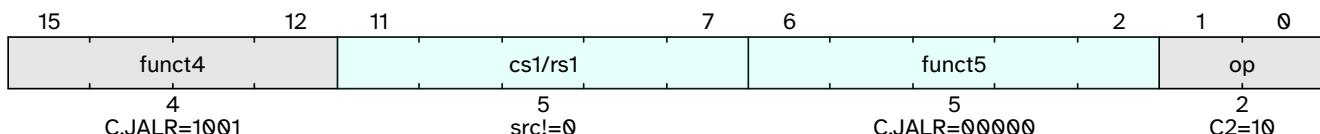

| 12.6.7. C.JALR .....                                                           | 167 |

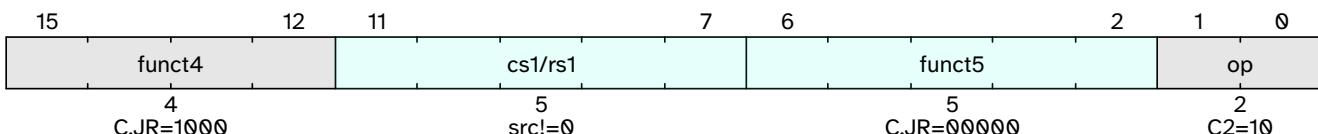

| 12.6.8. C.JR .....                                                             | 168 |

| 12.6.9. C.JAL .....                                                            | 169 |

| 12.6.10. C.J .....                                                             | 170 |

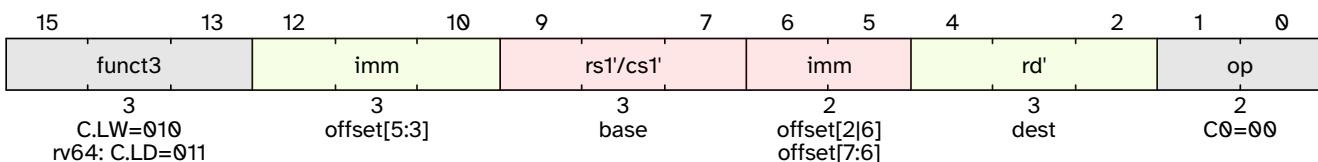

| 12.6.11. C.LD .....                                                            | 171 |

| 12.6.12. C.LW .....                                                            | 172 |

|                                                                                                |     |

|------------------------------------------------------------------------------------------------|-----|

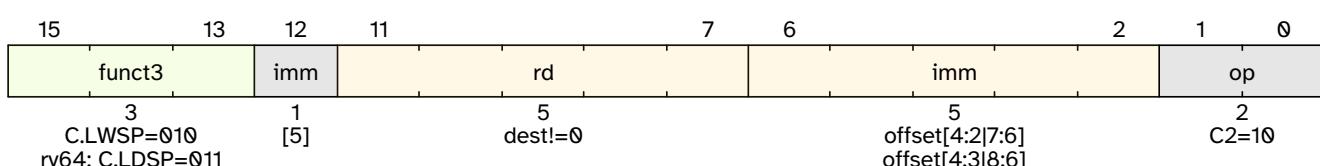

| 12.6.13. C.LWSP .....                                                                          | 174 |

| 12.6.14. C.LDSP .....                                                                          | 175 |

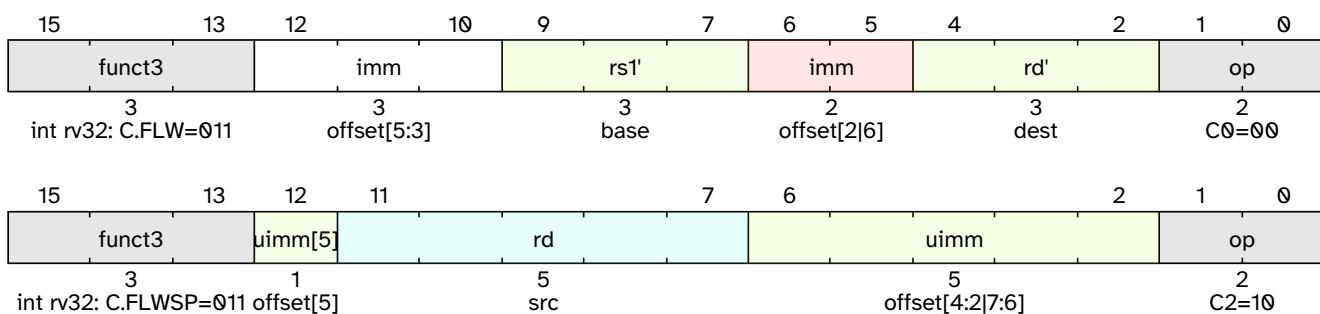

| 12.6.15. C.FLW .....                                                                           | 177 |

| 12.6.16. C.FLWSP .....                                                                         | 177 |

| 12.6.17. C.FLD .....                                                                           | 179 |

| 12.6.18. C.FLDSP .....                                                                         | 179 |

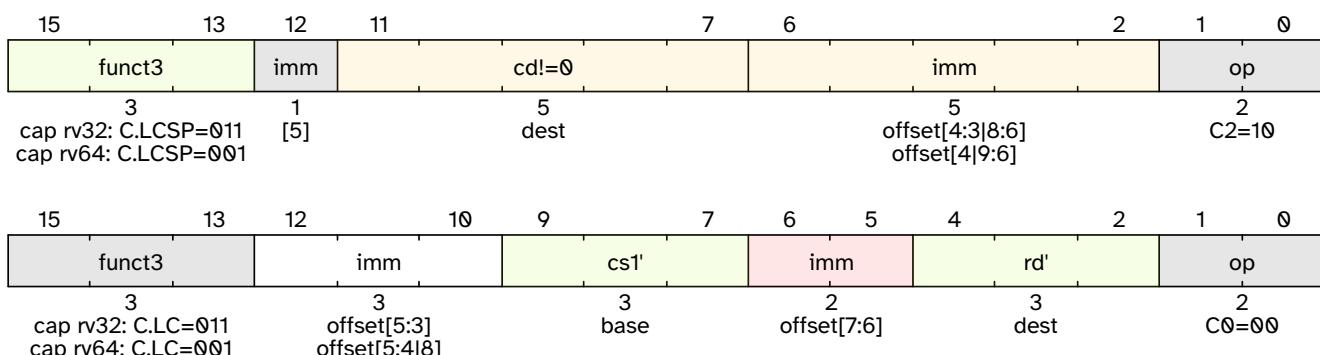

| 12.6.19. C.LC .....                                                                            | 181 |

| 12.6.20. C.LCSP .....                                                                          | 181 |

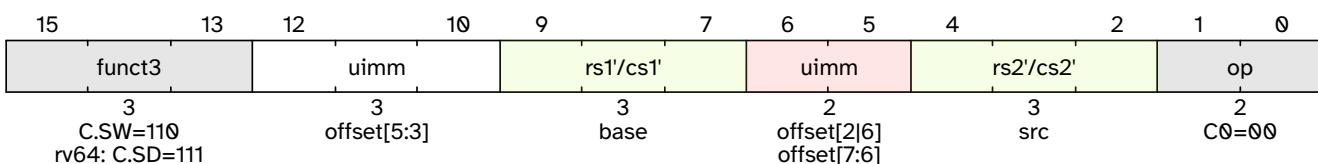

| 12.6.21. C.SD .....                                                                            | 183 |

| 12.6.22. C.SW .....                                                                            | 184 |

| 12.6.23. C.SWSP .....                                                                          | 186 |

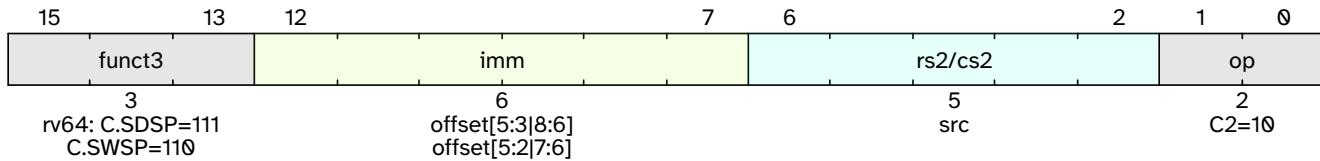

| 12.6.24. C.SDSP .....                                                                          | 187 |

| 12.6.25. C.FSW .....                                                                           | 189 |

| 12.6.26. C.FSWSP .....                                                                         | 189 |

| 12.6.27. C.FSD .....                                                                           | 191 |

| 12.6.28. C.FSDSP .....                                                                         | 191 |

| 12.6.29. C.SC .....                                                                            | 193 |

| 12.6.30. C.SCSP .....                                                                          | 193 |

| 12.7. "Zicbom", "Zicbop", "Zicboz" Standard Extensions for Base Cache Management Operations .. | 195 |

| 12.7.1. CBO.CLEAN .....                                                                        | 196 |

| 12.7.2. CBO.FLUSH .....                                                                        | 198 |

| 12.7.3. CBO.INVAL .....                                                                        | 200 |

| 12.7.4. CBO.ZERO .....                                                                         | 202 |

| 12.7.5. PREFETCH.I .....                                                                       | 204 |

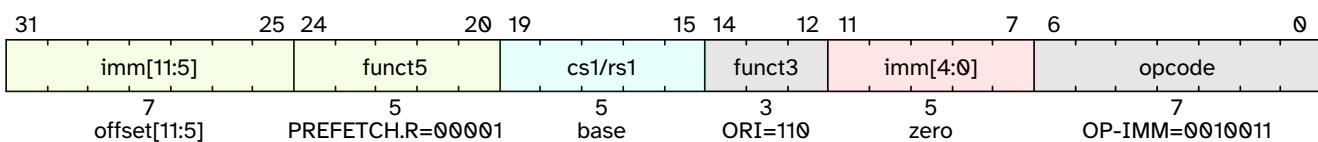

| 12.7.6. PREFETCH.R .....                                                                       | 206 |

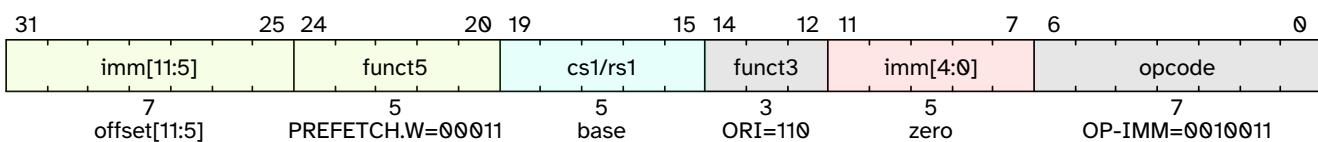

| 12.7.7. PREFETCH.W .....                                                                       | 208 |

| 12.8. "Zba" Extension for Bit Manipulation Instructions .....                                  | 210 |

| 12.8.1. ADD.UW .....                                                                           | 211 |

| 12.8.2. SH1ADD .....                                                                           | 213 |

| 12.8.3. SH2ADD .....                                                                           | 213 |

| 12.8.4. SH3ADD .....                                                                           | 214 |

| 12.8.5. SH1ADD.UW .....                                                                        | 216 |

| 12.8.6. SH2ADD.UW .....                                                                        | 216 |

| 12.8.7. SH3ADD.UW .....                                                                        | 217 |

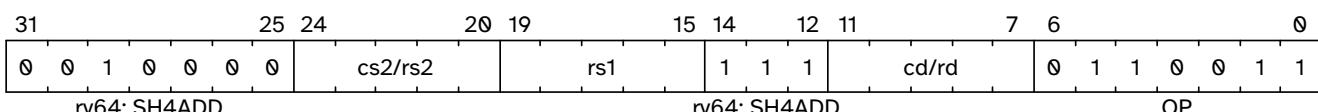

| 12.8.8. SH4ADD .....                                                                           | 219 |

| 12.8.9. SH4ADD.UW .....                                                                        | 221 |

| 12.9. "Zcb" Standard Extension For Code-Size Reduction .....                                   | 223 |

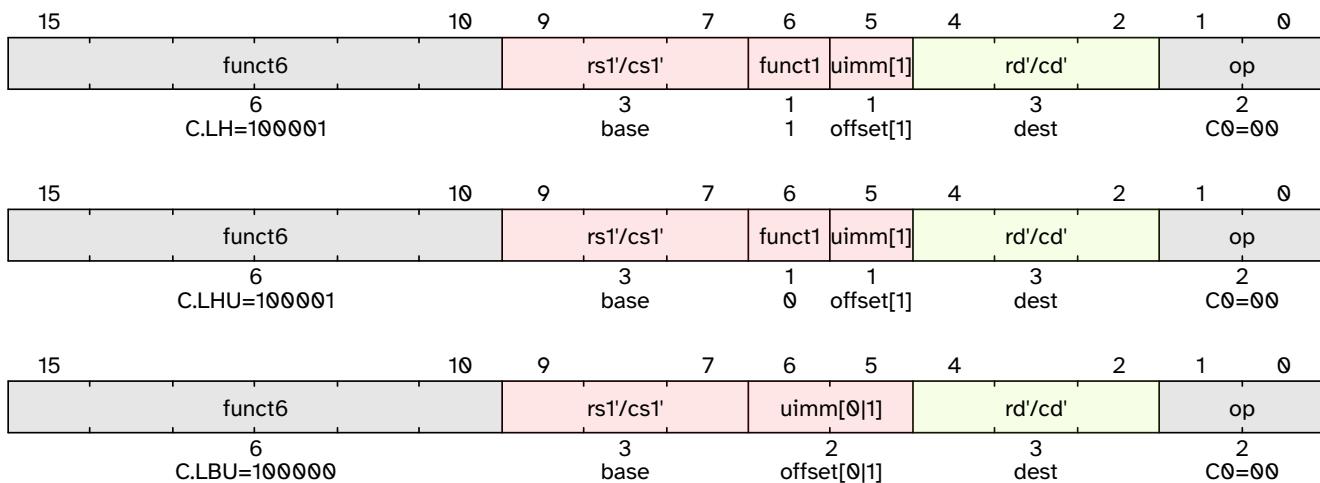

| 12.9.1. C.LH .....                                                                             | 224 |

| 12.9.2. C.LHU .....                                                                            | 224 |

| 12.9.3. C.LBU .....                                                                            | 225 |

| 12.9.4. C.SH .....                                                                             | 227 |

| 12.9.5. C.SB .....                                                                             | 228 |

| 12.10. "Zcmp" Standard Extension For Code-Size Reduction .....                                 | 230 |

|                                                                |            |

|----------------------------------------------------------------|------------|

| 12.10.1. CM.PUSH .....                                         | 231        |

| 12.10.2. CM.POP .....                                          | 233        |

| 12.10.3. CM.POPRET .....                                       | 235        |

| 12.10.4. CM.POPRETZ .....                                      | 237        |

| 12.10.5. CM.MVSA01 .....                                       | 239        |

| 12.10.6. CM.MVA01S .....                                       | 240        |

| 12.11. "Zcmt" Standard Extension For Code-Size Reduction ..... | 241        |

| 12.11.1. Jump Vector Table CSR (jvt) .....                     | 241        |

| 12.11.2. Jump Vector Table CSR (jvtc) .....                    | 241        |

| 12.11.3. CM.JALT .....                                         | 242        |

| 12.11.4. CM.JT .....                                           | 244        |

| 12.12. "H" Extension for Hypervisor Support .....              | 246        |

| 12.12.1. HLV.B .....                                           | 247        |

| 12.12.2. HLV.BU .....                                          | 247        |

| 12.12.3. HLV.H .....                                           | 247        |

| 12.12.4. HLV.HU .....                                          | 247        |

| 12.12.5. HLV.WU .....                                          | 247        |

| 12.12.6. HLV.D .....                                           | 247        |

| 12.12.7. HLV.W .....                                           | 248        |

| 12.12.8. HLV.C .....                                           | 250        |

| 12.12.9. HSV.B .....                                           | 253        |

| 12.12.10. HSV.H .....                                          | 253        |

| 12.12.11. HSV.D .....                                          | 253        |

| 12.12.12. HSV.W .....                                          | 254        |

| 12.12.13. HSV.C .....                                          | 256        |

| 12.12.14. HLVX.HU .....                                        | 258        |

| 12.12.15. HLVX.WU .....                                        | 258        |

| <b>Appendix A: CHERI System Implications .....</b>             | <b>260</b> |

| A.1. Small CHERI system example .....                          | 260        |

| A.2. Large CHERI system example .....                          | 261        |

| A.3. Large CHERI pure-capability system example .....          | 263        |

| <b>Appendix B: Extension summary .....</b>                     | <b>264</b> |

| B.1. Zabhlrsc .....                                            | 264        |

| B.2. Zish4add .....                                            | 264        |

| B.3. Zcheripurecap .....                                       | 264        |

| B.4. Zcherihybrid .....                                        | 273        |

| <b>Appendix C: Capability Width CSR Summary .....</b>          | <b>275</b> |

| <b>Appendix D: Instructions and CHERI Execution Mode .....</b> | <b>280</b> |

| <b>Bibliography .....</b>                                      | <b>289</b> |

## Preamble

*This document is in the [Development state](#)*

*Expect potential changes. This draft specification is likely to evolve before it is accepted as a standard. Implementations based on this draft may not conform to the future standard.*

## Copyright and license information

This specification is licensed under the Creative Commons Attribution 4.0 International License (CC-BY 4.0). The full license text is available at [creativecommons.org/licenses/by/4.0/](https://creativecommons.org/licenses/by/4.0/).

Copyright 2024 by RISC-V International.

## Contributors

This RISC-V specification has been contributed to directly or indirectly by:

- Thomas Aird <[thomas.aird@codasip.com](mailto:thomas.aird@codasip.com)>

- Hesham Almatary <[hesham.almatary@cl.cam.ac.uk](mailto:hesham.almatary@cl.cam.ac.uk)>

- Andres Amaya Garcia <[andres.amaya@codasip.com](mailto:andres.amaya@codasip.com)>

- John Baldwin <[jhb61@cl.cam.ac.uk](mailto:jhb61@cl.cam.ac.uk)>

- Paul Buxton <[paul.buxton@codasip.com](mailto:paul.buxton@codasip.com)>

- David Chisnall <[david.chisnall@cl.cam.ac.uk](mailto:david.chisnall@cl.cam.ac.uk)>

- Jessica Clarke <[jessica.clarke@cl.cam.ac.uk](mailto:jessica.clarke@cl.cam.ac.uk)>

- Brooks Davis <[brooks.davis@sri.com](mailto:brooks.davis@sri.com)>

- Lawrence Esswood <[lesswood@google.com](mailto:lesswood@google.com)>

- Nathaniel Wesley Filardo <[nwf20@cam.ac.uk](mailto:nwf20@cam.ac.uk)>

- Franz A. Fuchs <[franz.fuchs@cl.cam.ac.uk](mailto:franz.fuchs@cl.cam.ac.uk)>

- Timothy Hutt <[timothy.hutt@codasip.com](mailto:timothy.hutt@codasip.com)>

- Alexandre Joannou <[alexandre.joannou@cl.cam.ac.uk](mailto:alexandre.joannou@cl.cam.ac.uk)>

- Martin Kaiser <[martin.kaiser@codasip.com](mailto:martin.kaiser@codasip.com)>

- Tariq Kurd <[tariq.kurd@codasip.com](mailto:tariq.kurd@codasip.com)>

- Ben Laurie <[benl@google.com](mailto:benl@google.com)>

- Marno van der Maas <[mvdmaas@lowrisc.org](mailto:mvdmaas@lowrisc.org)>

- Maja Malenko <[maja.malenko@codasip.com](mailto:maja.malenko@codasip.com)>

- A. Theodore Markettos <[theo.markettos@cl.cam.ac.uk](mailto:theo.markettos@cl.cam.ac.uk)>

- David McKay <[david.mckay@codasip.com](mailto:david.mckay@codasip.com)>

- Jamie Melling <[jamie.melling@codasip.com](mailto:jamie.melling@codasip.com)>

- Stuart Menefy <[stuart.menefy@codasip.com](mailto:stuart.menefy@codasip.com)>

- Simon W. Moore <[simon.moore@cl.cam.ac.uk](mailto:simon.moore@cl.cam.ac.uk)>

- Peter G. Neumann <[neumann@csl.sri.com](mailto:neumann@csl.sri.com)>

- Robert Norton <[robert.norton@cl.cam.ac.uk](mailto:robert.norton@cl.cam.ac.uk)>

- Alexander Richardson <[alexrichardson@google.com](mailto:alexrichardson@google.com)>

- Michael Roe <[mr101@cam.ac.uk](mailto:mr101@cam.ac.uk)>

- Peter Rugg <[peter.rugg@cl.cam.ac.uk](mailto:peter.rugg@cl.cam.ac.uk)>

- Peter Sewell <[peter.sewell@cl.cam.ac.uk](mailto:peter.sewell@cl.cam.ac.uk)>

- Carl Shaw <[carl.shaw@codasip.com](mailto:carl.shaw@codasip.com)>

- Ricki Tura <[ricki.tura@codasip.com](mailto:ricki.tura@codasip.com)>

- Robert N. M. Watson <[robert.watson@cl.cam.ac.uk](mailto:robert.watson@cl.cam.ac.uk)>

- Toby Wenman <[toby.wenman@codasip.com](mailto:toby.wenman@codasip.com)>

- Jonathan Woodruff <[jonathan.woodruff@cl.cam.ac.uk](mailto:jonathan.woodruff@cl.cam.ac.uk)>

- Jason Zhijingcheng Yu <[yu.zhi@comp.nus.edu.sg](mailto:yu.zhi@comp.nus.edu.sg)>

# Chapter 1. Quick Start

This document describes the RISC-V extensions for supporting CHERI capabilities in hardware. Capabilities can be used to provide memory safety, mitigating up to 70% of memory safety issues (Joly et al., 2020), as well as to provide efficient compartmentalization. The extensions are split into the core features required for a working capability system (Zcheripurecap), and features required to support a mix-and-match of binaries compiled for CHERI and unchanged binaries (Zcherihybrid). Some other smaller extensions are described that provide additional functionality relevant to CHERI.

## 1.1. Capability Properties

Capabilities are  $2^*XLEN$  (which we call CLEN) bit structures, containing all the information required to identify and authorize access to a region of memory. This includes:

- An XLEN bit address, describing where the capability currently points.

- Bounds: a *base* and a *top* address, describing the range of addresses the capability can be used to access.

- Permissions (read, write, execute, read capability, ...) describing the kinds of accesses the capability can be used for.

- Sealing information: a capability can be *sealed*, restricting it to only be used or modified in particular ways.

A one-bit integrity tag is stored alongside a capability: this is maintained by hardware and cannot be directly modified by software. It indicates whether the capability is valid. An initial [Infinite](#) capability with access to all of memory with all permissions is provided in system registers on reset: all valid capabilities are derived from it. This is the only way to obtain a valid capability: no software, even machine mode, can *forge* a capability.

## 1.2. Added State

A CHERI core adds state to allow capabilities to be used from within registers, and to ensure they are not corrupted as they flow through the system. This means the following state is added:

- Metadata within architectural registers: XLEN-wide integer registers (e.g. sp, a0) are all extended with another XLEN bits of capability metadata, including bounds and permissions. The resulting CLEN bits in full form a capability, and we refer to the same register prefixed with a c, i.e. csp, ca0. The integer part of the register is interpreted as the address field of the capability. The zero register is extended with zero metadata and a cleared tag: this is called the [NULL](#) capability. As well as general purpose registers, system registers that store addresses are extended to contain capabilities. For example, [mtvec](#) is extended to a capability version [mtvecc](#) (the machine trap vector capability) to allow the code bounds to be changed on an exception.

- Tags in registers, caches, and memory:

- Every register has a one-bit tag, indicating whether the capability in the register is valid to be dereferenced. Among other reasons, this tag is cleared if the register is written as an integer.

- The tags are also tracked through the memory subsystem: every aligned CLEN-bits wide region has a non-addressable one-bit tag, which the hardware manages atomically with the data. The tag is cleared if the memory region is ever written other than using a capability store from a tagged capability register. Any caches must preserve this abstraction.

## 1.3. Checking Memory

Every memory access performed by a CHERI core must be authorized by a capability. It is explicitly defined for every instruction where to find the capability to check against. In *purecap* code, where all pointers are individual capabilities, the capability and address are used together, so e.g. `lw t0, 16(csp)` loads a word from memory, getting the address and bounds from the `csp` register. For code that has not yet been fully adapted to CHERI (*hybrid* code), the processor can run in a pointer mode (not to be confused with a privilege mode) where the authorizing capability is instead taken from a special CSR: the default data capability (`ddc`).

Instruction fetch is also authorized by a capability: the program counter capability (`pcc`) which extends PC. This allows code fetch to be bounded, preventing a wide range of attacks that subvert control flow with integer data. Where Zcherihybrid is supported, the `pcc` also contains the `mode bit` indicating whether the processor is running in integer or capability pointer mode. Changing the bounds used for instruction fetch or the pointer mode can be as easy as performing a capability-based jump (`JALR` in capability pointer mode). `MODESW.CAP` and `MODESW.INT` instructions are also added to allow cheap mode switching.

Exception codes are added for CHERI-specific exceptions on fetch, jumps, and memory access. No other exception paths are added: in particular, capability manipulations do not trap, but may clear the tag on the result capability if the operation is not permitted.

## 1.4. Added Instructions

The added instructions can be split into the following categories:

- Capability manipulations (e.g. `CADD`, `SCBNDS`): for security, capabilities can only be modified in restricted ways. Special instructions are provided to perform these allowed operations, for example *shrinking* the bounds or *reducing* the permissions. Any attempt to manipulate capabilities without using the instructions clears the tag, rendering them unusable for accessing memory.

- Capability inspection (e.g. `GCBASE`, `GCPERM`): capability fields (for example the *bounds* describing what addresses the capability gives access to) are stored compressed in registers and memory. These instructions give convenient access to allow software to query them.

- Memory access instructions (e.g. `LC`, `SC`): capabilities must be read from and written to memory atomically along with their tag. Instructions are added to perform these wider accesses, allowing capability flow between the memory and the register file.

## 1.5. Existing Instructions

Existing RISC-V instructions are largely unmodified: in *Integer Pointer Mode*, there is binary compatibility. Instructions that access memory, as well as branches and jumps, are automatically checked against `ddc` and `pcc`, raising an exception if the checks fail. However, `ddc` and `pcc` are reset to `Infinite` capabilities, meaning the checks will always pass on systems that have not written to CHERI system registers.

In *Capability Pointer Mode*, these instructions are instead modified to check against the full capability from the address register (e.g. `lw t0, 16(csp)`). In some cases, they are also changed to return a full capability value, e.g. `AUIPC` will return the full `pcc` including the metadata.

## Chapter 2. Introduction

### 2.1. CHERI Concepts and Terminology

Current CPU architectures (including RISC-V) allow memory access solely by specifying and dereferencing a memory address stored as an integer value in a register or in memory. Any accidental or malicious action that modifies such an integer value can result in unrestricted access to the memory that it addresses. Unfortunately, this weak memory protection model has resulted in the majority of software security vulnerabilities present in software today.

CHERI enables software to efficiently implement fine-grained memory protection and scalable software compartmentalization by providing strong, efficient hardware mechanisms to support software execution and enable it to prevent and mitigate vulnerabilities.

Design goals include incremental adoptability from current ISAs and software stacks, low performance overhead for memory protection, significant performance improvements for software compartmentalization, formal grounding, and programmer-friendly underpinnings. It has been designed to provide strong, non-probabilistic protection rather than depending on short random numbers or truncated cryptographic hashes that can be leaked and reinjected, or that could be brute forced.

CHERI enhances the CPU to add hardware memory access control. It has an additional memory access mechanism that protects *references to code and data* (pointers), rather than the *location of code and data* (integer addresses). This mechanism is implemented by providing a new primitive, called a **capability**, that software components can use to implement strongly protected pointers within an address space.

Capabilities are unforgeable and delegatable tokens of authority that grant software the ability to perform a specific set of operations. In CHERI, integer-based pointers can be replaced by capabilities to provide memory access control. In this case, a memory access capability contains an integer memory address that is extended with metadata to protect its integrity, limit how it is manipulated, and control its use. This metadata includes:

- an out-of-band *tag* implementing strong integrity protection (differentiating valid and invalid capabilities) that prevents confusion between data and capabilities

- *bounds* limiting the range of addresses that may be dereferenced

- *permissions* controlling the specific operations that may be performed

- *type* which is used to support higher-level software encapsulation

The CHERI model is motivated by the *principle of least privilege*, which argues that greater security can be obtained by minimizing the privileges accessible to running software. A second guiding principle is the *principle of intentional use*, which argues that, where many privileges are available to a piece of software, the privilege to use should be explicitly named rather than implicitly selected. While CHERI does not prevent the expression of vulnerable software designs, it provides strong vulnerability mitigation: attackers have a more limited vocabulary for attacks, and should a vulnerability be successfully exploited, they gain fewer rights, and have reduced access to further attack surfaces.

Protection properties for capabilities include the ISA ensuring that capabilities are always derived via valid manipulations of other capabilities (*provenance*), that corrupted in-memory capabilities cannot be dereferenced (*integrity*), and that rights associated with capabilities shall only ever be equal or less

permissive (*monotonicity*). Tampering or modifying capabilities in an attempt to elevate their rights will yield an invalid capability as the tag will be cleared. Attempting to dereference via an invalid capability will result in a hardware exception.

CHERI capabilities may be held in registers or in memories, and are loaded, stored, and dereferenced using CHERI-aware instructions that expect capability operands rather than integer addresses. On hardware reset, initial capabilities are made available to software via capability registers. All other capabilities will be derived from these initial valid capabilities through valid capability transformations.

Developers can use CHERI to build fine-grained spatial and temporal memory protection into their system software and applications and significantly improve their security.

## 2.2. CHERI Extensions to RISC-V

This specification is based on publicly available documentation including ([Watson et al., 2023](#)) and ([Woodruff et al., 2019](#)). It defines the following extensions to support CHERI alongside RISC-V:

### Zcheripurecap

Introduces key, minimal CHERI concepts and features to the RISC-V ISA. The resulting extended ISA is not backwards-compatible with RISC-V.

### Zcherihybrid

Extends Zcheripurecap with features to ensure that the ISA extended with CHERI allows backwards binary compatibility with RISC-V.

### Zish4add

Addition of [SH4ADD](#) and [SH4ADD.UW](#) for RV64 only, as CHERI capabilities are 16 bytes when XLEN=64

### Zabhlrsc

Addition of [LR.B](#), [LR.H](#), [SC.B](#), [SC.H](#) for more accurate atomic locking as the memory ranges are restricted by using bounds, therefore precise locking is needed.

### Zcheripte

CHERI extension for RISC-V harts supporting page-based virtual-memory.

### Zstid

Extension for supporting thread identifiers. This extension improves software compartmentalization on CHERI systems.

### Zcherilevels

Extension for supporting capability flow control. This extension allows limiting storing of capabilities to specific regions and can be used e.g. for safer data sharing between compartments.

*The extension names are provisional and subject to change.*

*Table 1. Extension status and summary*

| Extension                     | Status | Comment                                    |

|-------------------------------|--------|--------------------------------------------|

| <a href="#">Zcheripurecap</a> | Stable | This extension is a candidate for freezing |

| <a href="#">Zcherihybrid</a>  | Stable | This extension is a candidate for freezing |

| Extension                   | Status      | Comment                                                                                              |

|-----------------------------|-------------|------------------------------------------------------------------------------------------------------|

| Zish4add                    | Stable      | This extension is a candidate for freezing                                                           |

| Zabhlrsc                    | Stable      | This extension is a candidate for freezing                                                           |

| Zcheripte                   | Stabilizing | This extension is a candidate for freeze, software evaluation currently ongoing                      |

| Zstid                       | Stabilizing | This extension is a candidate for freeze, software evaluation currently ongoing                      |

| Zcherilevels with LVLBITS=1 | Prototype   | This extension is a prototype, software is being developed to use it to increase the maturity level. |

Zcheripurecap is defined as the base extension which all CHERI RISC-V implementations must support. Zcherihybrid and Zcheripte are optional extensions in addition to Zcheripurecap.

We refer to software as *purecap* if it utilizes CHERI capabilities for all memory accesses — including loads, stores and instruction fetches — rather than integer addresses. Purecap software requires the CHERI RISC-V hart to support Zcheripurecap. We refer to software as *hybrid* if it uses integer addresses **or** CHERI capabilities for memory accesses. Hybrid software requires the CHERI RISC-V hart to support Zcheripurecap and Zcherihybrid.

See [Chapter 12](#) for compatibility with other RISC-V extensions.

## 2.3. Risks and Known Uncertainty

- All extensions could be divided up differently in the future, including after ratification

- The RISC-V Architecture Review Committee (ARC) are likely to update all encodings

- The ARC are likely to update all CSR addresses

- Instruction mnemonics may be renamed

- Any changes will affect assembly code, but assembler aliases can provide backwards compatibility

### 2.3.1. Partially Incompatible Extensions

There are RISC-V extensions in development that may duplicate some aspects of CHERI functionality or directly conflict with CHERI and should only be available in *Integer Pointer Mode* on a CHERI-enabled hart. These include:

- RISC-V CFI specification

- "J" Pointer Masking (see [Chapter 10](#)).

## Chapter 3. Anatomy of Capabilities in Zcheripurecap

RISC-V defines variants of the base integer instruction set characterized by the width of the integer registers and the corresponding size of the address space. There are two primary ISA variants, RV32I and RV64I, which provide 32-bit and 64-bit address spaces respectively. The term XLEN refers to the width of an integer register in bits (either 32 or 64). The value of XLEN may change dynamically at run-time depending on the values written to CSRs, so we define capability behavior in terms of MXLEN, which is the value of XLEN used in machine mode and the widest XLEN the implementation supports.

*Zcheripurecap assumes a version of the privileged architecture which defines MXLEN as constant and requires higher privilege modes to have at least the same XLEN as lower privilege modes; these changes are present in the current draft and expected to be part of privileged architecture 1.13.*

Zcheripurecap defines capabilities of size CLEN corresponding to  $2 * MXLEN$  without including the tag bit. The value of CLEN is always calculated based on MXLEN regardless of the effective XLEN value.

*We briefly note that the capability encoding described in this section could be replaced with an entirely different design without changing how CHERI integrates with the RISC-V ISA. In particular, this capability encoding specification was designed to run software initially ported to CHERIv9 while providing spatial safety, temporal safety and compartmentalization support alongside a good measure of compatibility with RISC-V software that is not aware of CHERI. Alternative capability encoding specifications must provide key primitives, such as permissions and bounds, from this specification while using a different encoding that, for example, changes the granularity of bounds or adds new features. For simplicity of expression, the text is written as if this was the only possible capability encoding for CHERI RISC-V.*

### 3.1. Capability Encoding

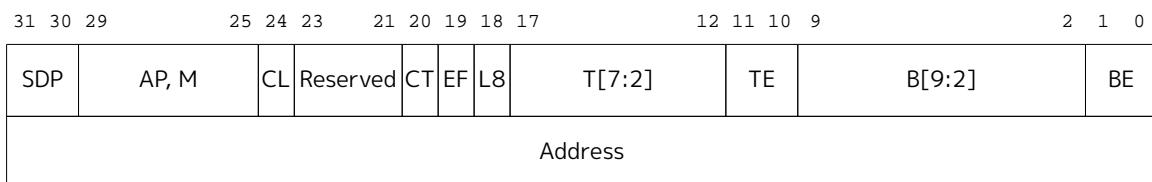

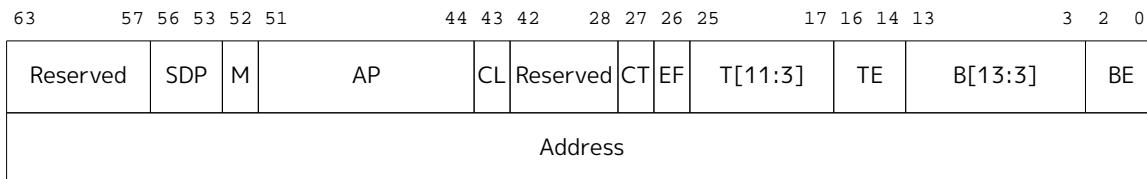

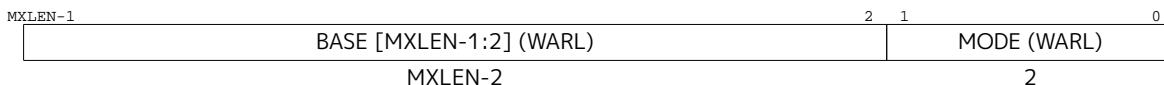

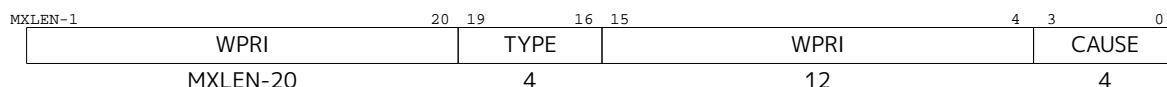

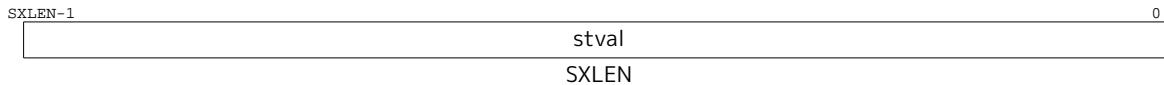

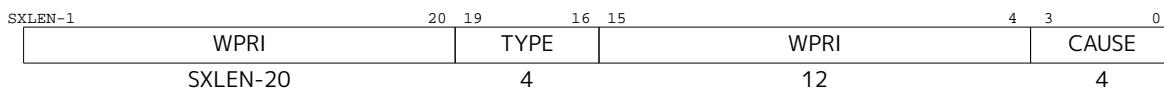

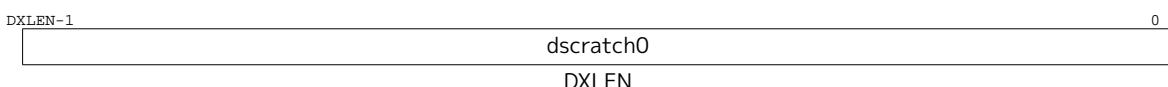

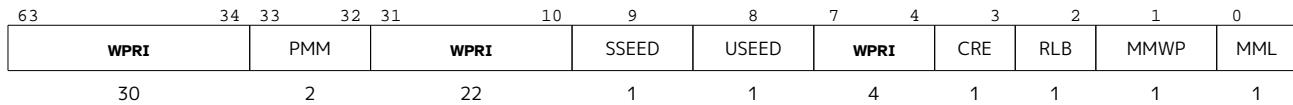

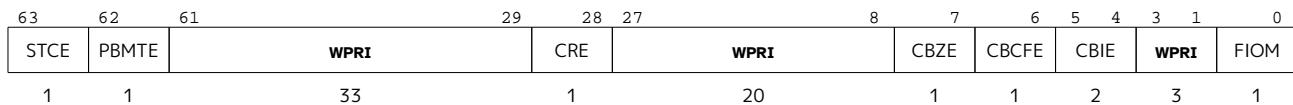

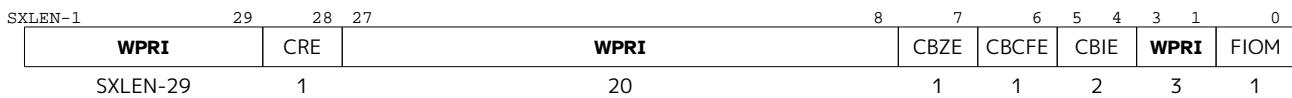

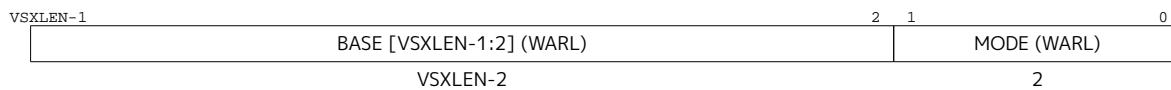

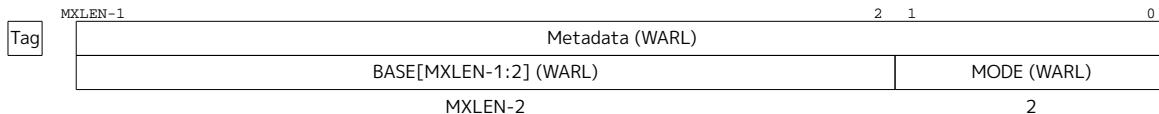

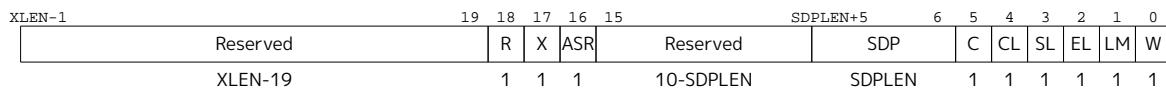

The components of a capability, except the tag, are encoded as shown in [Figure 1](#) for MXLEN=32 and [Figure 2](#) for MXLEN=64. Each memory location or register able to hold a capability must also store the tag as out of band information that software cannot directly set or clear. The capability metadata is held in the most significant bits and the address is held in the least significant bits.

32

*Figure 1. Capability encoding for MXLEN=32*

64

Figure 2. Capability encoding for MXLEN=64

Reserved bits are available for future extensions to Zcheripurecap.

- i Reserved bits must be 0 in tagged capabilities.

- i The CL field is only present if Zcherilevels is implemented, otherwise it is reserved.

## 3.2. Components of a Capability

Capabilities contain the software accessible fields described in this section.

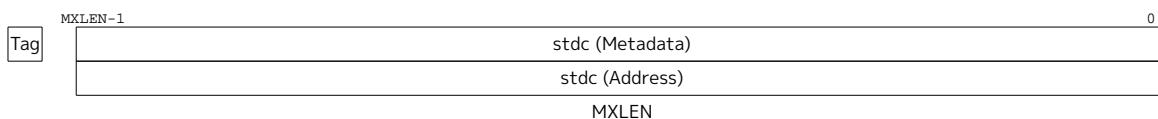

### 3.2.1. Tag

The tag is an additional hardware managed bit added to addressable memory and registers. It is stored separately and may be referred to as "out of band". It indicates whether a register or CLEN-aligned memory location contains a valid capability. If the tag is set, the capability is valid and can be dereferenced (contingent on checks such as permissions or bounds).

The capability is invalid if the tag is clear. Using an invalid capability to dereference memory or authorize any operation gives rise to exceptions. All capabilities derived from invalid capabilities are themselves invalid i.e. their tags are 0.

All locations in registers or memory able to hold a capability are CLEN+1 bits wide including the tag bit. Those locations are referred as being *CLEN-bit* or *capability wide* in this specification.

### 3.2.2. Address

The byte-address of a memory location is encoded as MXLEN integer value.

Table 2. Address widths depending on MXLEN

| MXLEN | Address width |

|-------|---------------|

| 32    | 32            |

| 64    | 64            |

### 3.2.3. Architectural Permissions (AP)

#### Description

This field encodes architecturally defined permissions of the capability. Permissions grant access subject to the tag being set, the capability being unsealed (see [Section 3.2.5](#)), and bounds checks (see [Section 3.2.6](#)). An operation is also contingent on requirements imposed by other RISC-V architectural

features, such as virtual memory, PMP and PMAs, even if the capability grants sufficient permissions. The permissions currently defined in Zcheripurecap are listed below.

### Read Permission (R)

Allow reading integer data from memory. Tags are always read as zero when reading integer data.

### Write Permission (W)

Allow writing integer data to memory. Tags are always written as zero when writing integer data. Every CLEN aligned word in memory has a tag, if any byte is overwritten with integer data then the tag for all CLEN-bits is cleared.

### Capability Permission (C)

Allow reading capability data from memory if the authorizing capability also grants [R-permission](#). Allow writing capability data to memory if the authorizing capability also grants [W-permission](#).

### Execute Permission (X)

Allow instruction execution.

### Load Mutable Permission (LM)

Allow preserving the [W-permission](#) of capabilities loaded from memory. If a capability grants [R-permission](#) and [C-permission](#), but no [LM-permission](#), then a capability loaded via this authorizing capability will have [W-permission](#) and [LM-permission](#) removed provided that the loaded capability has its tag set and is not sealed; loaded capabilities that are sealed or untagged do not have their permissions changed. The rules specified by [ACPERM](#) are followed when [W-permission](#) and [LM-permission](#) are removed, so additional permissions may also be removed. Clearing a capability's [LM-permission](#) and [W-permission](#) allows sharing a read-only version of a data structure (e.g. a tree or linked list) without making a copy.

*Implementations are allowed to retain invalid capability permissions loaded from memory instead of following the [ACPERM](#) behavior of reducing them to no permissions.*

### Access System Registers Permission (ASR)

Allow read and write access to all privileged (M-mode and S-mode) CSRs. If Zstid is supported the `utid`, `utidc`, `vstid`, `vstidc`, `stid`, `stidc`, `mtid`, `mtidc` registers are all considered privileged for the purposes of writing and unprivileged for reading, and thus require ASR-permission for writes but not reads. In all cases a suitable privilege mode is required for access.

### Permission Encoding

The bit width of the permissions field depends on the value of MXLEN as shown in [Table 3](#). A 5-bit vector encodes the permissions when MXLEN=32. For this case, the legal encodings of permissions are listed in [Table 4](#). Certain combinations of permissions are impractical. For example, [C-permission](#) is superfluous when the capability does not grant either [R-permission](#) or [W-permission](#). Therefore, it is only possible to encode a subset of all combinations.

*Table 3. Permissions widths depending on MXLEN*

| MXLEN | AP field width | Comment                                                                                                           |

|-------|----------------|-------------------------------------------------------------------------------------------------------------------|

| 32    | 5              | Encodes some combinations of 6 permission bits, including the <a href="#">M-bit</a> if Zcherihybrid is supported. |

| MXLEN | AP field width | Comment                                          |

|-------|----------------|--------------------------------------------------|

| 64    | 6              | Separate bits for each architectural permission. |

*if  $Z_{cherilevels}$  is supported then there are 8 architectural permission bits.*

For MXLEN=32, the permissions encoding is split into four quadrants. The quadrant is taken from bits [4:3] of the permissions encoding. The meaning for bits [2:0] are shown in [Table 4](#) for each quadrant.

Quadrants 2 and 3 are arranged to implicitly grant future permissions which may be added with the existing allocated encodings. Quadrant 0 does the opposite - the encodings are allocated *not* to implicitly add future permissions, and so granting future permissions will require new encodings. Quadrant 1 encodes permissions for executable capabilities and the [M-bit](#).

Table 4. Encoding of architectural permissions for MXLEN=32

| Encoding[2:0]                                                                                  | R | W | C | LM | X | ASR | Mode <sup>1</sup> | Notes                                         |  |  |

|------------------------------------------------------------------------------------------------|---|---|---|----|---|-----|-------------------|-----------------------------------------------|--|--|

| <b>Quadrant 0: Non-capability data read/write</b>                                              |   |   |   |    |   |     |                   |                                               |  |  |

| bit[2] - write, bit[1] - reserved (0), bit[0] - read                                           |   |   |   |    |   |     |                   |                                               |  |  |

| <i>Reserved bits for future extensions are 0 so new permissions are not implicitly granted</i> |   |   |   |    |   |     |                   |                                               |  |  |

| 0                                                                                              |   |   |   |    |   |     | N/A               | No permissions                                |  |  |

| 1                                                                                              | ✓ |   |   |    |   |     | N/A               | Data RO                                       |  |  |

| 2-3                                                                                            |   |   |   |    |   |     | reserved          |                                               |  |  |

| 4                                                                                              |   | ✓ |   |    |   |     | N/A               | Data WO                                       |  |  |

| 5                                                                                              | ✓ | ✓ |   |    |   |     | N/A               | Data RW                                       |  |  |

| 6-7                                                                                            |   |   |   |    |   |     | reserved          |                                               |  |  |

| <b>Quadrant 1: Executable capabilities</b>                                                     |   |   |   |    |   |     |                   |                                               |  |  |

| bit[0] - <b>M-bit</b> (0-Capability Pointer Mode, 1-Integer Pointer Mode)                      |   |   |   |    |   |     |                   |                                               |  |  |

| 0-1                                                                                            | ✓ | ✓ | ✓ | ✓  | ✓ | ✓   | Mode <sup>1</sup> | Execute + ASR (see <a href="#">Infinite</a> ) |  |  |

| 2-3                                                                                            | ✓ |   | ✓ | ✓  | ✓ |     | Mode <sup>1</sup> | Execute + Data & Cap RO                       |  |  |

| 4-5                                                                                            | ✓ | ✓ | ✓ | ✓  | ✓ |     | Mode <sup>1</sup> | Execute + Data & Cap RW                       |  |  |

| 6-7                                                                                            | ✓ | ✓ |   |    | ✓ |     | Mode <sup>1</sup> | Execute + Data RW                             |  |  |

| <b>Quadrant 2: Restricted capability data read/write</b>                                       |   |   |   |    |   |     |                   |                                               |  |  |

| R and C implicitly granted, LM dependent on W permission.                                      |   |   |   |    |   |     |                   |                                               |  |  |

| <i>Reserved bits for future extensions must be 1 so they are implicitly granted</i>            |   |   |   |    |   |     |                   |                                               |  |  |

| bit[2] is reserved to mean write for future encodings                                          |   |   |   |    |   |     |                   |                                               |  |  |

| 0-2                                                                                            |   |   |   |    |   |     | reserved          |                                               |  |  |

| 3                                                                                              | ✓ |   | ✓ |    |   |     | N/A               | Data & Cap RO (no LM)                         |  |  |

| 4-7                                                                                            |   |   |   |    |   |     | reserved          |                                               |  |  |

| <b>Quadrant 3: Capability data read/write</b>                                                  |   |   |   |    |   |     |                   |                                               |  |  |

| bit[2] - write, R and C implicitly granted.                                                    |   |   |   |    |   |     |                   |                                               |  |  |

| <i>Reserved bits for future extensions must be 1 so they are implicitly granted</i>            |   |   |   |    |   |     |                   |                                               |  |  |

| 0-2                                                                                            |   |   |   |    |   |     | reserved          |                                               |  |  |

| 3                                                                                              | ✓ |   | ✓ | ✓  |   |     | N/A               | Data & Cap RO                                 |  |  |

| 4-6                                                                                            |   |   |   |    |   |     | reserved          |                                               |  |  |

| 7                                                                                              | ✓ | ✓ | ✓ | ✓  |   |     | N/A               | Data & Cap RW                                 |  |  |

<sup>1</sup> Mode ([M-bit](#)) can only be set on a tagged capability when [Zcherihybrid](#) is supported. Despite being encoded here it is **not** an architectural permission.

When MXLEN=32 there are many reserved permission encodings (see [Table 4](#)). It is not possible for a tagged capability to have one of these values since [ACPERM](#) will never create it. It is possible for untagged capabilities to have reserved values. [GCPERM](#) will interpret reserved values as if it were 0b00000 (no permissions).

*Future extensions may assign meanings to the reserved bit patterns, in which case **GCPERM** is allowed to report a non-zero value.*

A 6-bit vector encodes the permissions when MXLEN=64 (8-bit if Zcherilevels is supported). In this case, there is a bit per permission as shown in [Table 5](#). A permission is granted if its corresponding bit is set, otherwise the capability does not grant that permission.

Table 5. Encoding of architectural permissions for MXLEN=64

| Bit | Name                       |

|-----|----------------------------|

| 0   | C-permission               |

| 1   | W-permission               |

| 2   | R-permission               |

| 3   | X-permission               |

| 4   | ASR-permission             |

| 5   | LM-permission              |

| 6   | EL-permission <sup>1</sup> |

| 7   | SL-permission <sup>1</sup> |

<sup>1</sup> This permission is only supported if the implementation supports [Zcherilevels](#).

The [M-bit](#) is only assigned meaning when the implementation supports Zcherihybrid and [X-permission](#) is set.

1. For MXLEN=64, the bit assigned to the [M-bit](#) must be zero if [X-permission](#) isn't set.

2. For MXLEN=32, the [M-bit](#) is only encoded in quadrant 1 and does *not* exist in the other quadrants.

#### Permission Transitions

Executing [ACPERM](#) can result in sets of permissions which cannot be represented when MXLEN=32 (see [Table 4](#)) or permission combinations which are not useful for MXLEN=64, such as [ASR-permission](#) set without [X-permission](#).

These cases are defined to return useful minimal sets of permissions, which may be no permissions. See [ACPERM](#) for these rules.

*Future extensions may allow more combinations of permissions, especially for MXLEN=64.*

#### 3.2.4. Software-Defined Permissions (SDP)

A bit vector used by the kernel or application programs for software-defined permissions (SDP).

*Software is completely free to define the usage of these bits. For example, a program may decide to use an SDP bit to indicate the "ownership" of objects. Therefore, a capability grants permission to free the memory it references if that SDP bit is set because it "owns" that object.*

Table 6. SDP widths depending on MXLEN

| MXLEN | SDPLEN |

|-------|--------|

| 32    | 2      |

| 64    | 4      |

### 3.2.5. Capability Type (CT) Bit

This bit indicates the type of the capability: it is a sealed capability if the bit is 1 or unsealed if it is 0.

Sealed capabilities ( $CT \neq 0$ ) cannot be dereferenced to access memory and are immutable such that modifying any of its fields clears the tag of the output capability.

*Sealed capabilities might be useful to software as tokens that can be passed around. The only way of clearing the type bit of a capability is by rebuilding it via a superset capability with [CBLD](#). Zcheripurecap does not offer an unseal instruction.*

*The [Capability Level \(CL\)](#) field can be reduced even if the capability is sealed, see [Table 31](#).*

For code capabilities, the sealing bit is used to implement immutable capabilities that describe function entry points, known as sealed entry (sentry) capabilities. Such capabilities can be leveraged to establish a form of control-flow integrity between mutually distrusting code. A program may jump to a sentry capability to begin executing the instructions it references. A [JALR](#) instruction with zero offset automatically unseals a sentry target capability and installs it in the program counter capability (see [Section 4.2](#)). The jump-and-link instructions also seal the return address capability which serves as an entry point the callee can return to but cannot use to authorize memory loads or stores.

### 3.2.6. Bounds (EF, T, TE, B, BE)

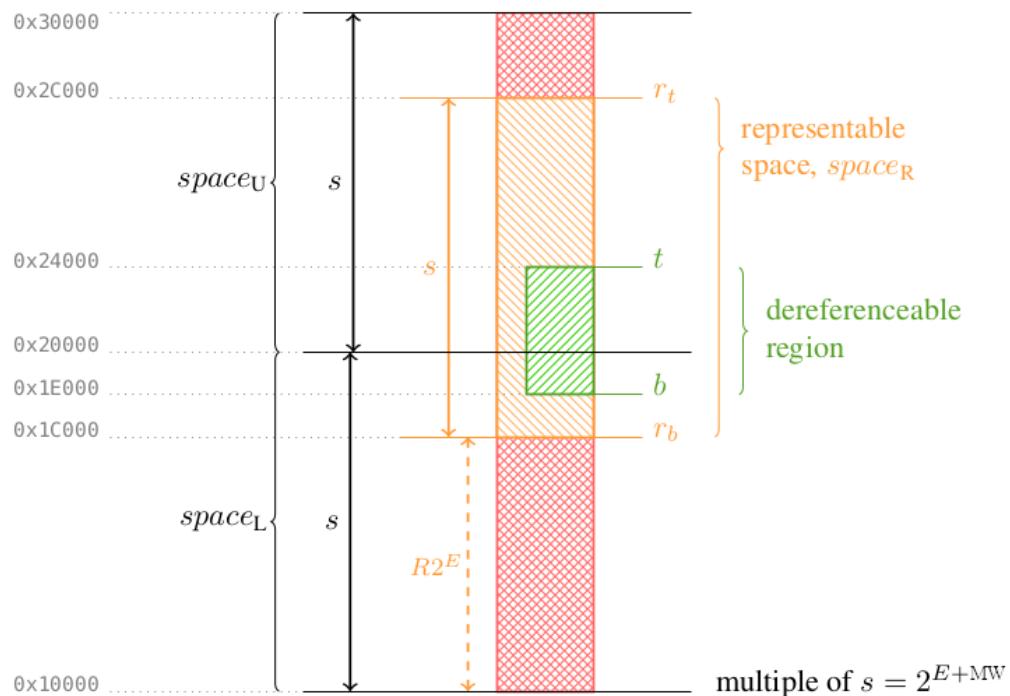

#### Concept

The bounds encode the base and top addresses that constrain memory accesses. The capability can be used to access any memory location  $A$  in the range  $\text{base} \leq A < \text{top}$ . The bounds are encoded in compressed format, so it is not possible to encode any arbitrary combination of base and top addresses. An invalid capability with tag cleared is produced when attempting to construct a capability that is not *representable* because its bounds cannot be correctly encoded. The bounds are decoded as described in [Section 3.1](#).

The bounds field has the following components:

- **T:** Value substituted into the capability's address to decode the top address

- **B:** Value substituted into the capability's address to decode the base address

- **E:** Exponent that determines the position at which B and T are substituted into the capability's address

- **EF:** Exponent format flag indicating the encoding for T, B and E

- The exponent is stored in T and B if  $EF=0$ , so it is 'internal'

- The exponent is zero if  $EF=1$

The bit width of T and B are defined in terms of the mantissa width (MW) which is set depending on the value of MXLEN as shown in [Table 7](#).

*Table 7. Mantissa width (MW) values depending on MXLEN*

| MXLEN | MW |

|-------|----|

| 32    | 10 |

| MXLEN | MW |

|-------|----|

| 64    | 14 |

The exponent E indicates the position of T and B within the capability's address as described in [Section 3.1](#). The bit width of the exponent (EW) is set depending on the value of MXLEN. The maximum value of the exponent is calculated as follows:

$$\text{CAP\_MAX\_E} = \text{MXLEN} - \text{MW} + 2$$

The possible values for EW and CAP\_MAX\_E are shown in [Table 8](#).

*Table 8. Exponent widths and CAP\_MAX\_E depending on MXLEN*

| MXLEN | EW | CAP_MAX_E |

|-------|----|-----------|

| 32    | 5  | 24        |

| 64    | 6  | 52        |

*The address and bounds must be representable in valid capabilities i.e. when the tag is set (see [Section 3.2.6.3](#)).*

## Decoding

The metadata is encoded in a compressed format ([Woodruff et al., 2019](#)). It uses a floating point representation to encode the bounds relative to the capability address. The base and top addresses from the bounds are decoded as shown below.

*TODO: The pseudocode below does not have a formal notation. It is simply a placeholder while the Sail implementation is unavailable. In this notation, / means "integer division", [] are the bit-select operators, and arithmetic is signed.*

```

EW      = (MXLEN == 32) ? 5 : 6

CAP_MAX_E = MXLEN - MW + 2

If EF = 1:

E          = 0

T[EW / 2 - 1:0] = TE

B[EW / 2 - 1:0] = BE

LCout      = (T[MW - 3:0] < B[MW - 3:0]) ? 1 : 0

LMSB       = (MXLEN == 32) ? L8 : 0

else:

E          = CAP_MAX_E - ( (MXLEN == 32) ? { L8, TE, BE } : { TE, BE } )

)

T[EW / 2 - 1:0] = 0

B[EW / 2 - 1:0] = 0

LCout      = (T[MW - 3:EW / 2] < B[MW - 3:EW / 2]) ? 1 : 0

LMSB       = 1

```

Reconstituting the top two bits of T:

$$T[MW - 1:MW - 2] = B[MW - 1:MW - 2] + LCout + LMSB$$

Decoding the bounds:

$$\begin{aligned} \text{top: } t &= \{ a[MXLEN - 1:E + MW] + ct, T[MW - 1:0] \}, \{E\{1'b0\}\} \} \\ \text{base: } b &= \{ a[MXLEN - 1:E + MW] + cb, B[MW - 1:0] \}, \{E\{1'b0\}\} \} \end{aligned}$$

The corrections  $c_t$  and  $c_b$  are calculated as shown below using the definitions in [Table 9](#) and [Table 10](#).

$$\begin{aligned} A &= a[E + MW - 1:E] \\ R &= B - 2^{MW-2} \end{aligned}$$

*Table 9. Calculation of top address correction*

| A < R | T < R | c <sub>t</sub> |

|-------|-------|----------------|

| false | false | 0              |

| false | true  | +1             |

| true  | false | -1             |

| true  | true  | 0              |

*Table 10. Calculation of base address correction*

| A < R | B < R | c <sub>b</sub> |

|-------|-------|----------------|

| false | false | 0              |

| false | true  | +1             |

| true  | false | -1             |

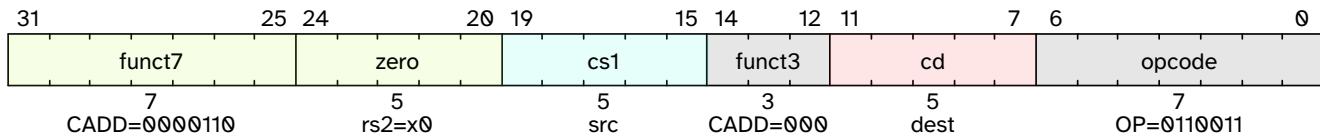

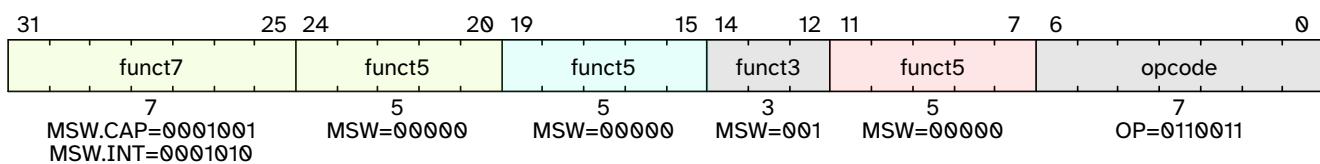

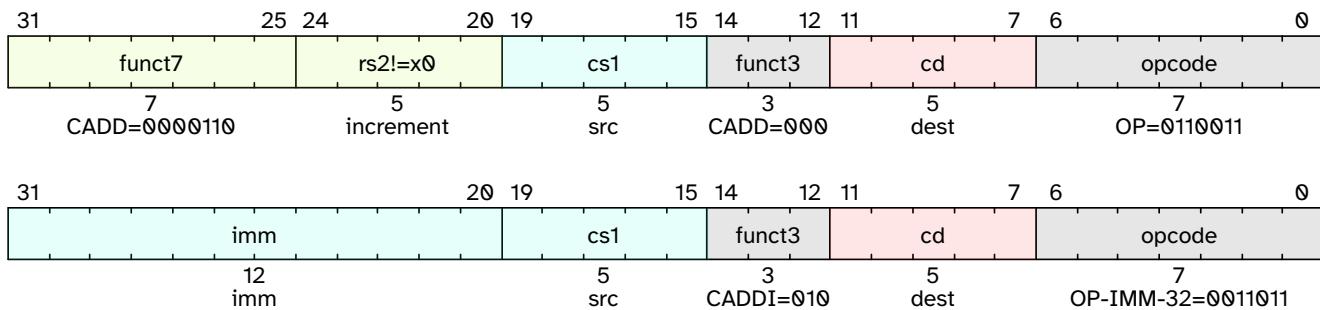

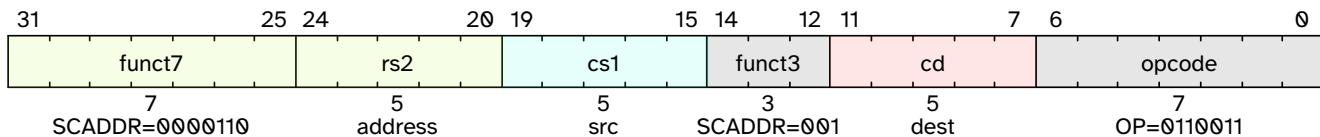

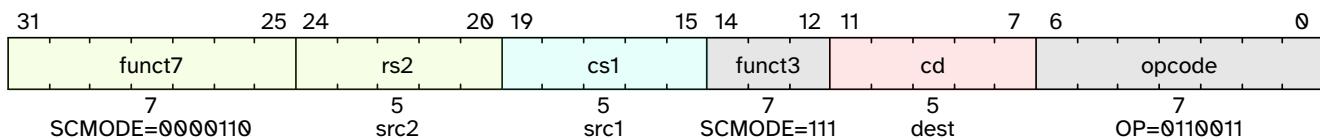

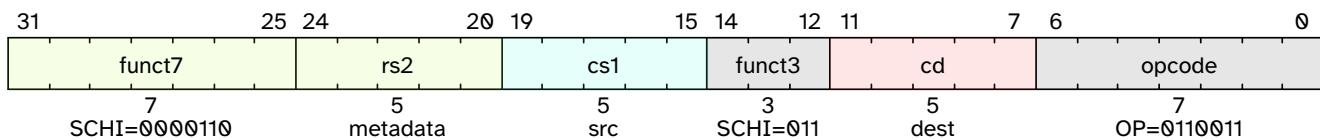

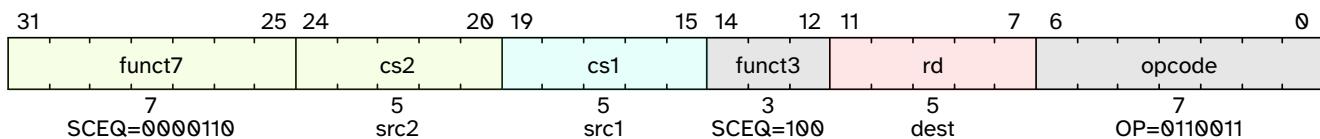

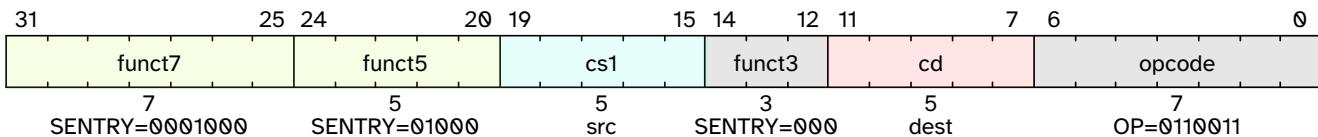

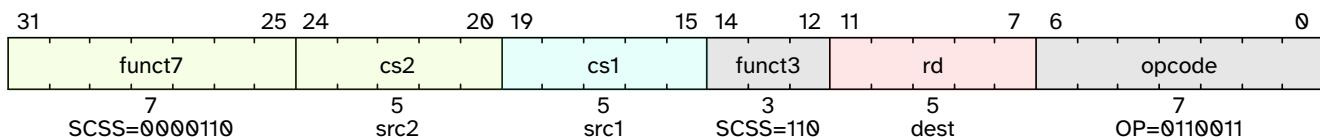

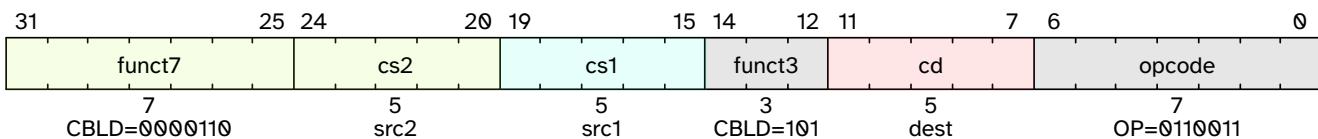

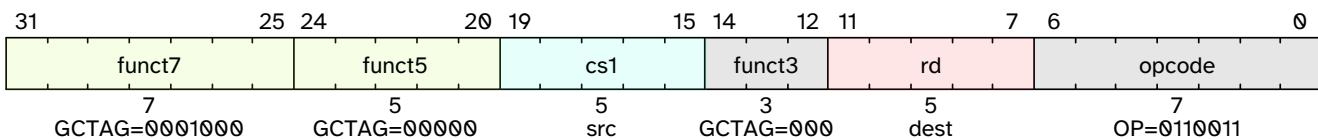

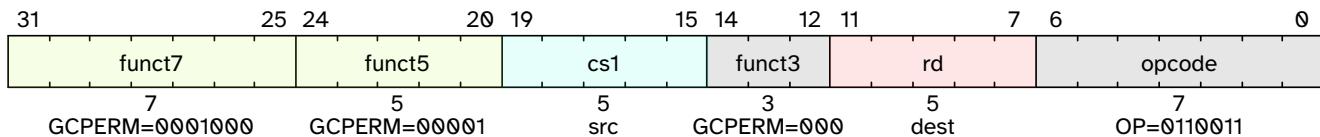

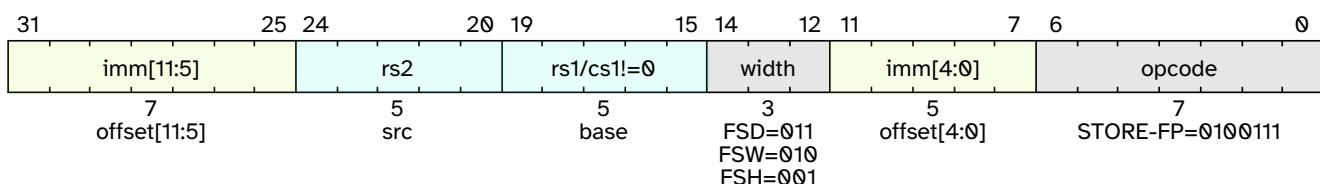

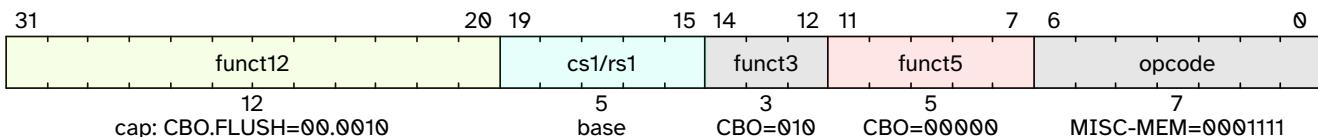

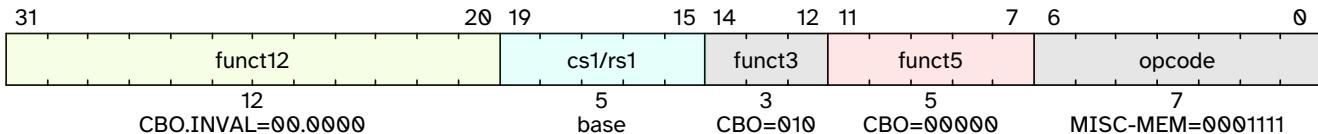

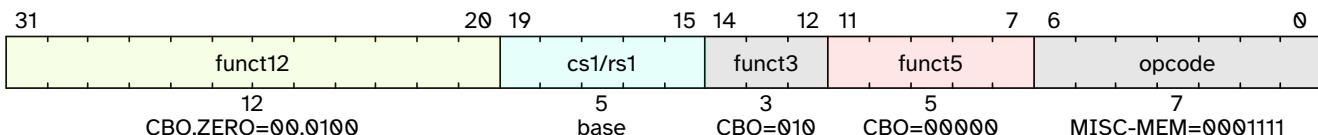

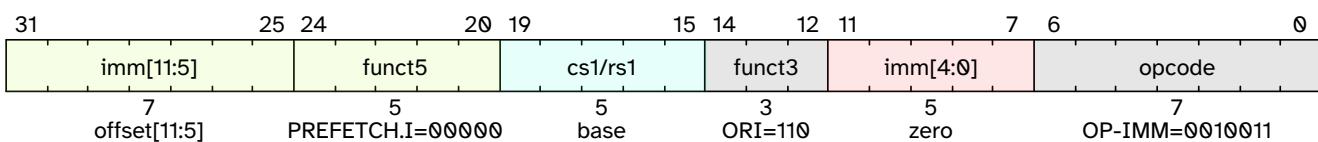

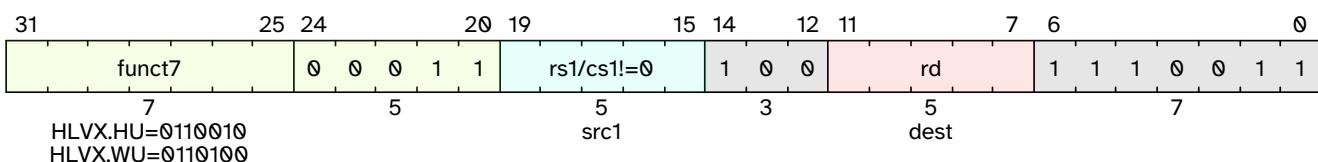

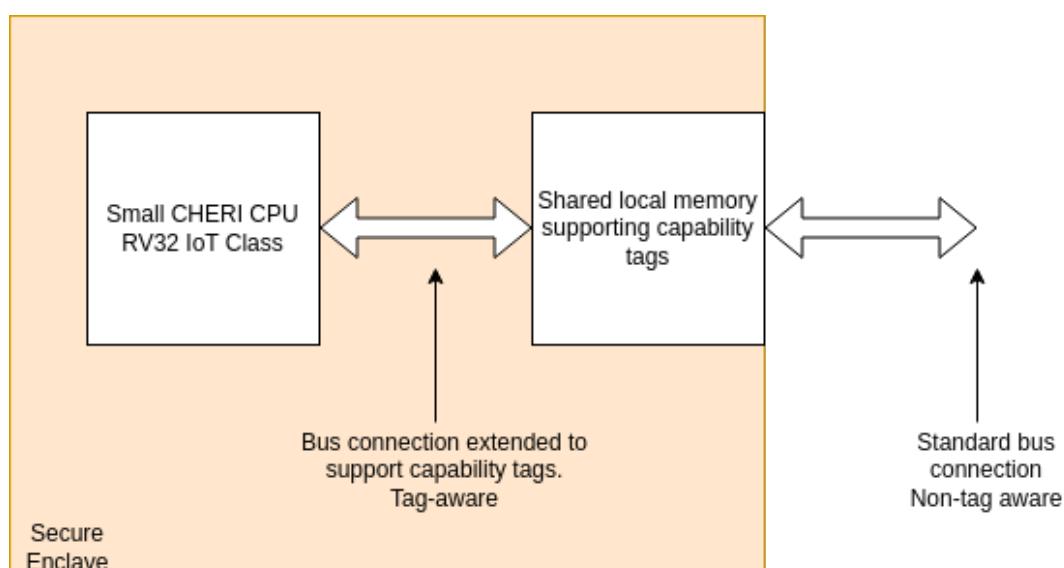

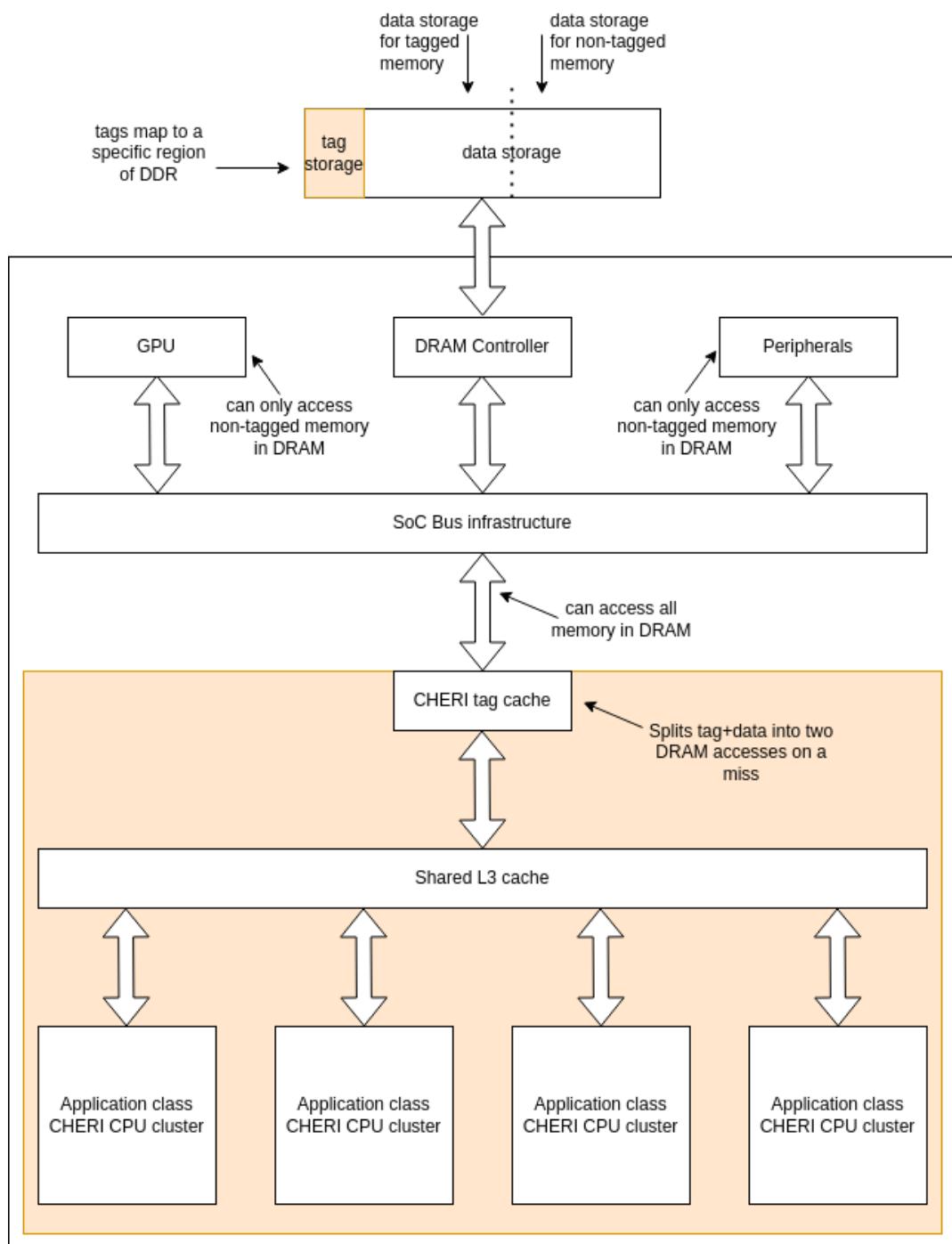

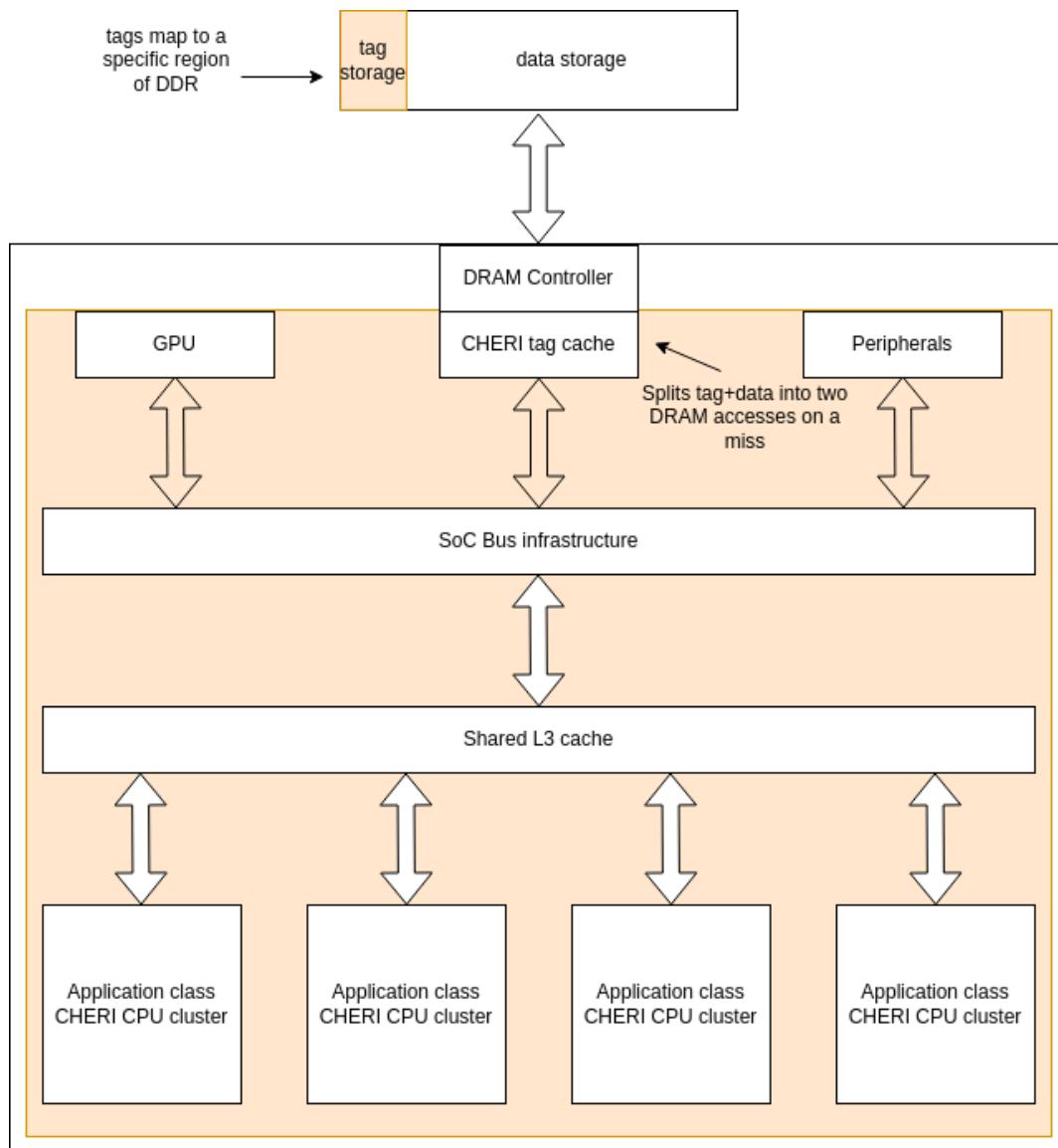

| true  | true  | 0              |