# ST231 core and instruction set architecture

Reference manual

7645929 Rev N

September 2009

# Reference manual

# ST231 core and instruction set architecture

# Introduction

The 32-bit ST231 is a member of the ST200 family of cores.

This family of embedded processors uses a scalable technology that allows variation in instruction issue width, the number and capabilities of functional units and register files, and the instruction set.

The ST200 family includes the following features:

- parallel execution units, including multiple integer ALUs and multipliers

- architectural support for data prefetch

- predicated execution through select operations

- efficient branch architecture with multiple condition registers

- encoding of immediate operands up to 32 bits

- support for user and supervisor modes and memory protection

Contents ST231

# **Contents**

| Introd | duction |          |                                  | 1  |

|--------|---------|----------|----------------------------------|----|

| Prefa  | ce      |          |                                  | )  |

|        | ST20    | 0 docum  | ent identification and control10 | C  |

|        | ST20    | 0 docum  | entation suite                   | O  |

|        |         |          | ised in this guide1              |    |

|        |         |          | ments12                          |    |

| 1      | Ovei    | rview .  |                                  | 3  |

| -      | 1.1     |          | overview                         |    |

|        | 1.2     |          | overview                         |    |

|        | 1.3     |          | nent overview                    |    |

| 2      | Exec    | cution u | nits                             | 5  |

|        | 2.1     |          | runits (IU)                      |    |

|        | 2.2     | Multiply | y units                          | 5  |

|        | 2.3     | Load/s   | tore unit (LSU)                  | 5  |

|        |         | 2.3.1    | Memory access                    |    |

|        |         | 2.3.2    | Addressing modes                 | 6  |

|        |         | 2.3.3    | Alignment                        | 6  |

|        |         | 2.3.4    | Control registers16              | 6  |

|        |         | 2.3.5    | Cache purging                    | ဝိ |

|        |         | 2.3.6    | Dismissible loads                | ô  |

|        | 2.4     | Branch   | ı unit                           | 7  |

|        |         | 2.4.1    | Idle mode macro17                | 7  |

|        |         | 2.4.2    | syncins macro18                  | 3  |

| 3      | Arch    | itectura | ıl state                         | 9  |

|        | 3.1     | Progra   | m counter (PC)19                 | 9  |

|        | 3.2     | Registe  | er file19                        | 9  |

|        |         | 3.2.1    | Link register                    | Э  |

|        | 3.3     | Branch   | register file                    | 9  |

|        |         |          |                                  |    |

|   | 3.4  | Program status word (PSW)            |

|---|------|--------------------------------------|

|   |      | 3.4.1 Bit fields                     |

|   |      | 3.4.2 USER_MODE21                    |

|   |      | 3.4.3 DEBUG_MODE                     |

|   |      | 3.4.4 PSW access                     |

|   | 3.5  | Control registers                    |

| 4 | Exec | cution pipeline and latencies        |

|   | 4.1  | Execution pipeline                   |

|   | 4.2  | Operation latencies                  |

|   | 4.3  | Branch stalls                        |

|   | 4.4  | Interlocks                           |

|   | 4.5  | Additional notes                     |

|   |      | 4.5.1 Flushing the pipeline          |

|   |      | 4.5.2 Restrictions on link register  |

| 5 | Trap | s (exceptions and interrupts)25      |

|   | 5.1  | Trap mechanism                       |

|   | 5.2  | Exception handling                   |

|   | 5.3  | Saved execution state                |

|   | 5.4  | Interrupts                           |

|   | 5.5  | Debug interrupt handling             |

|   | 5.6  | Exception types and priorities       |

|   |      | 5.6.1 Illegal instruction definition |

|   | 5.7  | Speculative load considerations      |

|   |      | 5.7.1 Misaligned implementation      |

| 6 | Mem  | ory translation and protection       |

|   | 6.1  | TLB overview                         |

|   | 6.2  | Address space 32                     |

|   |      | 6.2.1 Physical addresses32           |

|   |      | 6.2.2 Virtual addresses              |

|   | 6.3  | Caches                               |

|   |      | 6.3.1 Instruction cache organization |

|   |      |                                      |

|   |     | 6.3.2    | Data cache organization3  | 34         |

|---|-----|----------|---------------------------|------------|

|   | 6.4 | Contro   | l registers               | 35         |

|   |     | 6.4.1    | PSW                       | 35         |

|   |     | 6.4.2    | TLB_INDEX3                | 35         |

|   |     | 6.4.3    | TLB_ENTRY03               | 35         |

|   |     | 6.4.4    | TLB_ENTRY13               | 38         |

|   |     | 6.4.5    | TLB_ENTRY23               | 38         |

|   |     | 6.4.6    | TLB_ENTRY33               | 38         |

|   |     | 6.4.7    | TLB_REPLACE3              | 38         |

|   |     | 6.4.8    | TLB_CONTROL               | łO         |

|   |     | 6.4.9    | TLB_ASID                  | ŀO         |

|   |     | 6.4.10   | TLB_EXCAUSE4              | 11         |

|   | 6.5 | TLB de   | escription4               | 2          |

|   |     | 6.5.1    | Reset4                    | ŀ2         |

|   |     | 6.5.2    | UTLB arbitration          | ŀ2         |

|   |     | 6.5.3    | Exceptions                | ŀ3         |

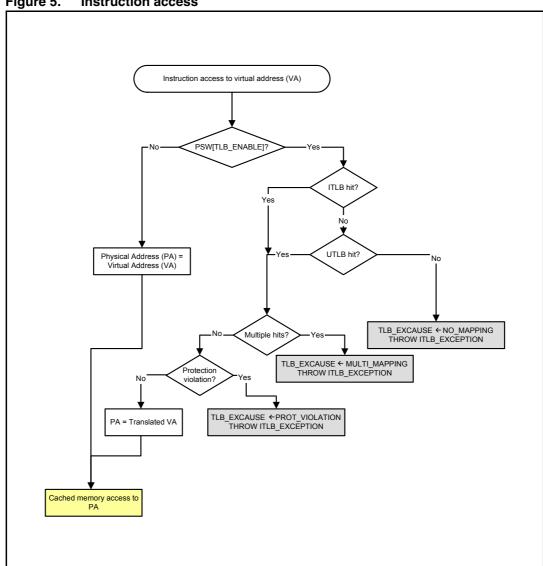

|   |     | 6.5.4    | Instruction accesses      | 14         |

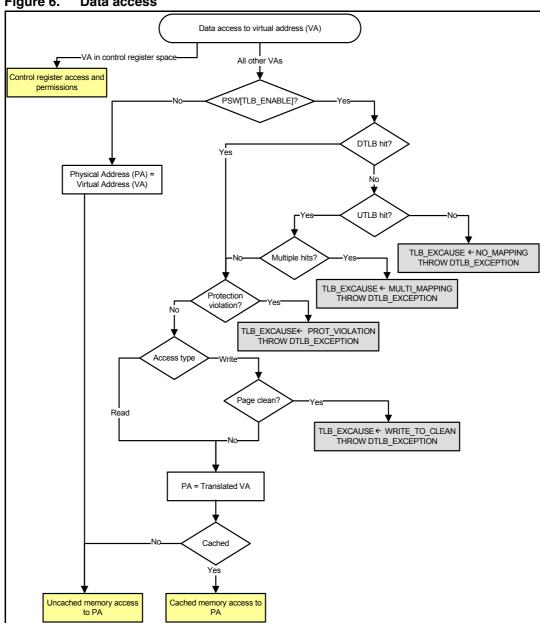

|   |     | 6.5.5    | Data accesses             | 15         |

|   | 6.6 | Specul   | ative control unit (SCU)  | 6          |

|   |     | 6.6.1    | SCU_BASEx4                | ŀ7         |

|   |     | 6.6.2    | SCU_LIMITx4               | ŀ7         |

|   |     | 6.6.3    | Updates to SCU registers4 | 17         |

| 7 | Mem | ory sub  | system                    | 8          |

|   | 7.1 | Memor    | y subsystem 4             | 9          |

|   | 7.2 | I-side n | nemory subsystem4         | 9          |

|   |     | 7.2.1    | Instruction buffer4       | <b>ļ</b> 9 |

|   |     | 7.2.2    | Instruction cache5        | 50         |

|   |     | 7.2.3    | I-side bus error          | 51         |

|   | 7.3 | D-side   | memory subsystem          | <b>i</b> 1 |

|   |     | 7.3.1    | Load/store unit           | 51         |

|   |     | 7.3.2    | Data cache partitioning5  | 52         |

|   |     | 7.3.3    | Speculative loads         | 52         |

|   |     | 7.3.4    | Cached loads and stores   | 52         |

|   |     | 7.3.5    | Uncached load and stores  | 53         |

|   |     | 7.3.6    | Prefetching data          | 53         |

|   |     |          |                           |            |

|   |       | 7.3.7    | Purging data caches                 | 54 |

|---|-------|----------|-------------------------------------|----|

|   |       | 7.3.8    | D-side synchronization              | 54 |

|   |       | 7.3.9    | D-side bus errors                   | 54 |

|   |       | 7.3.10   | Operations                          | 55 |

|   |       | 7.3.11   | Cache policy                        | 55 |

|   |       | 7.3.12   | Write buffer                        | 58 |

|   | 7.4   | Core m   | nemory controller (CMC)             | 58 |

|   | 7.5   | Additio  | nal notes                           | 59 |

|   |       | 7.5.1    | Memory ordering and synchronization | 59 |

|   |       | 7.5.2    | Coherency between I-side and D-side | 59 |

|   |       | 7.5.3    | Reset state                         | 59 |

|   |       | 7.5.4    | Cached data in uncached region      | 59 |

|   |       | 7.5.5    | Prefetch performance                | 60 |

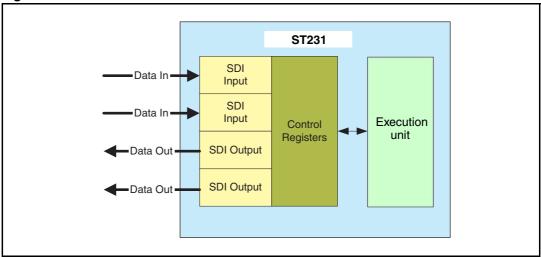

| 8 | Strea | aming d  | ata interface                       | 61 |

|   | 8.1   | Functio  | onal description                    | 61 |

|   |       | 8.1.1    | Data width                          | 62 |

|   | 8.2   | Comm     | unication channel                   | 62 |

|   |       | 8.2.1    | Timeouts                            | 62 |

|   | 8.3   | Registe  | ers                                 | 62 |

|   |       | 8.3.1    | Input channel memory mapping        | 63 |

|   |       | 8.3.2    | Output channel memory mapping       | 64 |

|   |       | 8.3.3    | Protection                          | 64 |

|   | 8.4   | Interru  | pts, exceptions and restarts        | 65 |

|   |       | 8.4.1    | Interrupts                          | 65 |

|   |       | 8.4.2    | SDI exceptions                      | 65 |

|   |       | 8.4.3    | Restart (soft reset)                | 65 |

| 9 | Cont  | rol regi | sters                               | 67 |

|   | 9.1   | Access   | s operations                        | 67 |

|   | 9.2   | Except   | ions                                | 67 |

|   | 9.3   | · ·      | I register addresses                |    |

|   | 9.4   |          | ache replacement state register     |    |

|   | 9.5   |          | n register                          |    |

|   | -     |          | •                                   |    |

| 10 | Time  | rs       |                                                                 | 73      |

|----|-------|----------|-----------------------------------------------------------------|---------|

|    | 10.1  | Operat   | ion                                                             | 73      |

|    |       | 10.1.1   | TIMEDIVIDEi                                                     | 73      |

|    |       | 10.1.2   | TIMECOUNTi                                                      | 74      |

|    |       | 10.1.3   | TIMECONST <i>i</i>                                              | 74      |

|    |       | 10.1.4   | TIMECONTROLi                                                    | 74      |

|    | 10.2  | Timer i  | nterrupts                                                       | 74      |

|    | 10.3  | Progra   | mming the timers                                                | 75      |

| 11 | Perip | heral a  | ddresses                                                        | 76      |

|    | 11.1  | Access   | s to peripheral registers                                       | 76      |

|    | 11.2  | Periphe  | eral addresses                                                  | 76      |

|    |       | 11.2.1   | Interrupt controller and timer registers                        | 77      |

|    |       | 11.2.2   | DSU registers                                                   | 78      |

|    |       | 11.2.3   | DSU ROM                                                         | 79      |

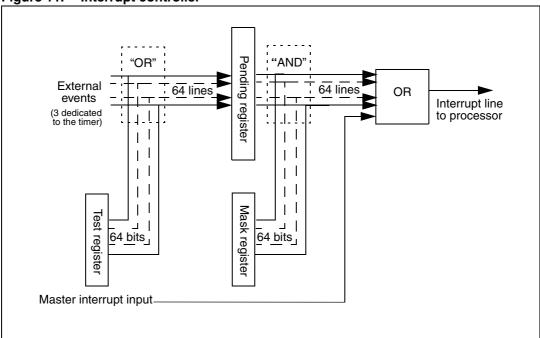

| 12 | Inter | rupt coi | ntroller                                                        | 80      |

|    | 12.1  | Archite  | cture                                                           | 80      |

|    | 12.2  | Operat   | ion                                                             | 80      |

|    |       | 12.2.1   | Test register                                                   | 81      |

|    |       | 12.2.2   | Master interrupt input                                          | 81      |

|    | 12.3  | Interru  | pt registers                                                    | 81      |

|    |       | 12.3.1   | Interrupt pending register (INTPENDING)                         | 81      |

|    |       | 12.3.2   | Interrupt mask register (INTMASK)                               | 82      |

|    |       | 12.3.3   | Interrupt mask set and clear registers (INTMASKSET and INTMASE) | ASKCLR) |

|    |       | 12.3.4   | Interrupt test register (INTTEST)                               | 84      |

|    |       | 12.3.5   | Interrupt set and clear registers (INTSET and INTCLR)           | 84      |

| 13 | Debu  | ıgging s | support (TAPLink)                                               | 87      |

|    | 13.1  | Core .   |                                                                 | 87      |

|    |       | 13.1.1   | Debug interrupts                                                | 87      |

|    |       | 13.1.2   | Hardware breakpoint support | 89    |

|----|-------|----------|-----------------------------|-------|

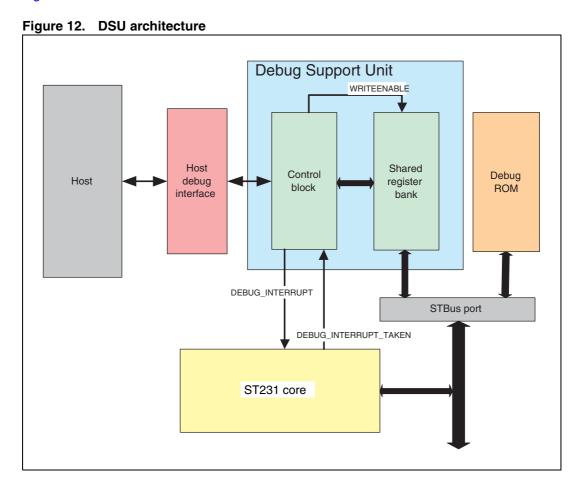

|    | 13.2  | Debug    | support unit                | 90    |

|    |       | 13.2.1   | Architecture                | 90    |

|    |       | 13.2.2   | Shared register bank        |       |

|    |       | 13.2.3   | DSU control registers       | 91    |

|    | 13.3  | Debug    | ROM                         | 93    |

|    |       | 13.3.1   | Debug initialization loop   | 93    |

|    |       | 13.3.2   | Default debug handler       | 93    |

|    | 13.4  | Host de  | bug interface               | 96    |

|    |       | 13.4.1   | Message format              | 96    |

|    |       | 13.4.2   | Operation                   | 97    |

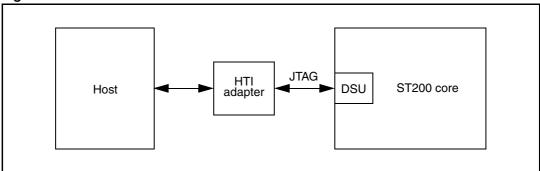

| 14 | Debu  | igging s | upport (JTAG)               | 98    |

|    | 14.1  | Core .   |                             | 98    |

|    |       | 14.1.1   | Debug interrupts            | 98    |

|    |       | 14.1.2   | Hardware breakpoint support | 99    |

|    | 14.2  | Debug    | support unit                | . 101 |

|    |       | 14.2.1   | Architecture                | 101   |

|    |       | 14.2.2   | Shared register bank        | 102   |

|    |       | 14.2.3   | DSU control registers       | 102   |

|    | 14.3  | Debug    | ROM                         | . 103 |

|    |       | 14.3.1   | Debug initialization loop   | 103   |

|    |       | 14.3.2   | Default debug handler       | 104   |

|    |       | 14.3.3   | User-defined debug handler  | 107   |

|    | 14.4  | Host de  | bug interface               | . 107 |

|    |       | 14.4.1   | Protocol and flow control   | 108   |

|    |       | 14.4.2   | Command Format              | 109   |

|    |       | 14.4.3   | Handling events             | 110   |

| 15 | Perfo | rmance   | monitoring                  | . 112 |

|    | 15.1  | Events   |                             | . 112 |

|    | 15.2  | Access   | to registers                | . 113 |

|    | 15.3  | Control  | register (PM_CR)            | . 114 |

|    | 15.4  | Event c  | ounters (PM_CNTi)           | . 114 |

|    | 15.5  | Clock c  | ounter (PM_PCLK)            | . 115 |

|    | 15.6  |          | ing events                  |       |

|    | . 3.0 | 2.2.0    |                             | 3     |

|    |       |          |                             |       |

| 16 | Exec | ution m  | odel                         | 116 |

|----|------|----------|------------------------------|-----|

|    | 16.1 | Bundle   | fetch, decode, and execute   | 116 |

|    | 16.2 | Functio  | ons                          | 118 |

|    |      | 16.2.1   | Bundle decode                | 118 |

|    |      | 16.2.2   | Operation execution          | 118 |

|    |      | 16.2.3   | Exceptional cases            | 118 |

| 17 | Spec | ificatio | n notation                   | 119 |

|    | 17.1 | Variabl  | es and types                 | 119 |

|    |      | 17.1.1   | Integer                      | 119 |

|    |      | 17.1.2   | Boolean                      |     |

|    |      | 17.1.3   | Bit-fields                   | 120 |

|    |      | 17.1.4   | Arrays                       | 120 |

|    | 17.2 | Expres   | sions                        | 120 |

|    |      | 17.2.1   | Integer arithmetic operators | 121 |

|    |      | 17.2.2   | Integer shift operators      | 122 |

|    |      | 17.2.3   | Integer bitwise operators    | 122 |

|    |      | 17.2.4   | Relational operators         | 123 |

|    |      | 17.2.5   | Boolean operators            | 123 |

|    |      | 17.2.6   | Single-value functions       | 124 |

|    | 17.3 | Statem   | ients                        | 125 |

|    |      | 17.3.1   | Undefined behavior           | 125 |

|    |      | 17.3.2   | Assignment                   | 125 |

|    |      | 17.3.3   | Conditional                  | 126 |

|    |      | 17.3.4   | Repetition                   | 127 |

|    |      | 17.3.5   | Exceptions                   | 127 |

|    |      | 17.3.6   | Procedures                   | 128 |

|    | 17.4 | Archite  | ctural state                 | 128 |

|    | 17.5 | Memor    | y and control registers      | 129 |

|    |      | 17.5.1   | Support functions            | 129 |

|    |      | 17.5.2   | Memory model                 |     |

|    |      | 17.5.3   | Control register model       |     |

|    |      | 17.5.4   | Cache model                  | 136 |

|    |      | 17.5.5   | Architectural state model    | 136 |

| 18         | Instru  | uction set                                                    | 137   |

|------------|---------|---------------------------------------------------------------|-------|

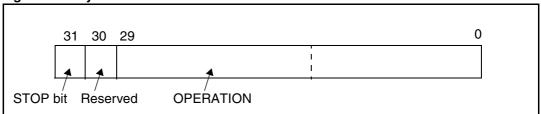

|            | 18.1    | Bundle encoding                                               | . 137 |

|            |         | 18.1.1 Extended immediates                                    | . 137 |

|            |         | 18.1.2 Encoding restrictions                                  | . 138 |

|            | 18.2    | Operation specifications                                      | 138   |

|            | 18.3    | Example operations                                            | 139   |

|            |         | 18.3.1 add Immediate                                          | . 139 |

|            | 18.4    | Macros                                                        | 141   |

|            | 18.5    | Operations                                                    | 142   |

| Appendix   | x A In  | struction encoding                                            | 312   |

|            | A.1     | Reserved bits                                                 | 312   |

|            | A.2     | Fields                                                        | 312   |

|            | A.3     | Formats                                                       |       |

|            | A.4     | Opcodes                                                       |       |

| Appendix   | x B S   | TBus endian behavior                                          | 320   |

|            | B.1     | Endianness of bytes and half-words within a word based memory | 320   |

|            | B.2     | Endianness of 64-bit accesses                                 | 321   |

|            | B.3     | System requirements                                           | 321   |

| Glossary   | ·       |                                                               | 322   |

| List of in | structi | ons                                                           | 324   |

| Revision   | histor  | у                                                             | 326   |

| Index      |         |                                                               | 327   |

Preface ST231

## **Preface**

#### ST200 document identification and control

Each book in the ST200 documentation suite carries a unique ADCS identifier of the form:

ADCS nnnnnnnx

where *nnnnnnn* is the document number, and *x* is the revision.

Whenever making comments on an ST200 document, the complete identification ADCS *nnnnnnnx* should be quoted.

#### ST200 documentation suite

The ST200 documentation suite comprises the following volumes:

#### ST231 Core and Instruction Set Architecture

(ADCS 7645929) This manual describes the architecture and the instruction set of the ST231 core as used by STMicroelectronics.

#### ST200 User Manual

(ADCS 8063762) This manual describes the ST200 Micro Toolset and provides an introduction to OS21. It covers the various cross tools and libraries that are provided in the toolset, the target platform libraries, how to boot OS21 applications from ROM and how to port applications which use STMicroelectronics' OS20 operating systems. Information is also given on how to build the open source packages that provide the compiler tools, base run-time libraries and debug tools and how to set up an ST Micro Connect.

#### **ST200 Micro Toolset Compiler Manual**

(ADCS 7508723) This manual provides a detailed guide to using the ANSI C and C++ compiler drivers for compiling and linking source code to produce an executable binary. The compiler drivers are introduced in terms of how they fit into the complete ST200 toolchain. The manual then concentrates on the facilities provided by the compiler drivers to produce efficient code. It covers: command line options, predefined macros, supported pragmas, compiler optimization techniques, GNU C and C++ language extensions and asm construct, the assembly language and intrinsic functions.

#### **ST200 Run-time Architecture Manual**

(ADCS 7521848) This manual describes the common software conventions for the ST200 processor run-time architecture.

#### ST200 ELF Specification

(ADCS 7932400) This document describes the use of the ELF file format for the ST200 processor. It provides information needed to create and interpret ELF files and is specific to the ST200 processor.

ST231 Preface

#### **OS21 User Manual**

(ADCS 7358306) This manual describes the royalty free, light weight, OS21 multitasking operating system.

#### **OS21 for ST200 User Manual**

(ADCS 7410372) This manual describes the use of OS21 on ST200 platforms. It describes how specific ST200 facilities are exploited by the OS21 API. It also describes the OS21 board support packages for ST200 platforms.

## Conventions used in this guide

#### **General notation**

The notation in this document uses the following conventions:

- sample code, keyboard input and file names

- variables and code variables

- code comments,

- screens, windows and dialog boxes

- instructions

#### **Hardware notation**

The following conventions are used for hardware notation:

- REGISTER NAMES and FIELD NAMES

- PIN NAMES and SIGNAL NAMES

#### Software notation

Syntax definitions are presented in a modified Backus-Naur Form (BNF). Briefly:

- Terminal strings of the language, that is, strings not built up by rules of the language, are printed in teletype font. For example, void.

- Nonterminal strings of the language, that is, strings built up by rules of the language, are printed in italic teletype font. For example, *name*.

- If a nonterminal string of the language starts with a nonitalicized part, it is equivalent to the same nonterminal string without that nonitalicized part. For example, vspace-name.

- Each phrase definition is built up using a double colon and an equals sign to separate the two sides ('::=').

- Alternatives are separated by vertical bars ('|').

- Optional sequences are enclosed in square brackets ('[' and ']').

- Items which may be repeated appear in braces ('{' and '}').

Preface ST231

# **Acknowledgements**

The ST231 core is based on technology jointly developed by Hewlett-Packard Laboratories and STMicroelectronics.

$\mathsf{Microsoft}^{\circledR}, \mathsf{Visual Studio}^{\circledR} \ \mathsf{and Windows}^{\circledR} \ \mathsf{are registered trademarks of Microsoft Corporation in the United States and/or other countries.}$

ST231 Overview

## 1 Overview

This chapter provides an introduction to the ST231 processor and to this reference manual.

#### 1.1 VLIW overview

VLIW (very long instruction word) processors use a technique where instruction level parallelism is explicitly exposed to the compiler, which must schedule operations to account for the operation latency. The hardware implementation of a VLIW processor is significantly simpler than a corresponding multiple issue superscalar CPU because of the simplicity of the grouping and scheduling hardware; the complexity is passed to the instruction scheduling software (compiler and assembler) which is responsible for scheduling the parallel operations for maximum efficiency.

RISC-like operations (syllables) are grouped into bundles (wide words). The operations in a bundle are issued simultaneously. In the ST200 family operations also complete simultaneously. While the delay between issue and completion is the same for all operations, some results are available for bypassing to subsequent operations prior to completion. This is discussed further in *Chapter 4: Execution pipeline and latencies on page 22*.

#### 1.2 ST231 overview

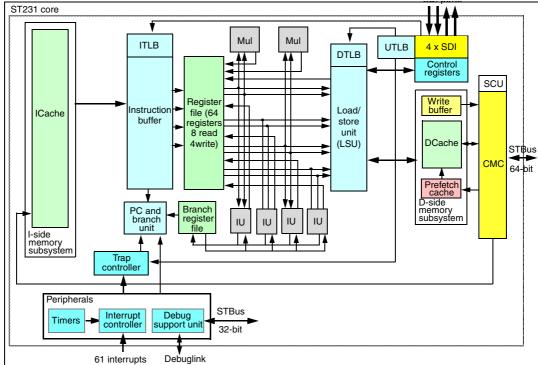

The ST231 includes the ST231 core and associated peripherals. *Figure 1* shows the arrangement of these components in a block diagram.

Figure 1. Block diagram of the ST231

ST231 Overview

#### 1.3 **Document overview**

This manual describes the architecture and instruction set of the ST231 implementation. This section gives an outline of the following document.

The processor is made up of a number of functional units described in Chapter 2: Execution units which operate on data stored in the register files (Chapter 3: Architectural state). These functional units are pipelined and subject to explicit observable latencies (Chapter 4: Execution pipeline and latencies).

The handling of exceptions and interrupts are detailed in Chapter 5: Traps (exceptions and interrupts).

The ST231 accesses memory through the memory subsystem (Chapter 7: Memory subsystem) which provides protection and address translation by means of a translation lookaside buffer (Chapter 5: Traps (exceptions and interrupts)).

The ST231 has four SDI ports (Chapter 8: Streaming data interface) which allow it to communicate rapidly with other devices and avoid cache pollution when processing large amounts of data.

Control of the devices is performed using the memory mapped control registers defined within the relevant chapters. The address of the control registers and PSW are detailed in Chapter 9: Control registers.

The ST231 also provides a performance monitoring system to help with software optimization and debugging (Chapter 15: Performance monitoring).

The following peripheral devices are also provided: timers (Chapter 10: Timers), interrupt control (Chapter 12: Interrupt controller) and debug support(a) (Chapter 13: Debugging support (TAPLink) or Chapter 14: Debugging support (JTAG)). The peripheral register addresses are detailed in Chapter 11: Peripheral addresses.

The execution model is described in Chapter 16: Execution model. The execution of bundles is described in Section 16.1: Bundle fetch, decode, and execute on page 116, including the behavior of the machine when exceptions or interrupts are encountered.

Chapter 18: Instruction set describes the details of each operation, including the semantics. The instruction set includes details of the instruction set encoding, syntax and semantics. The encoding of bundles is defined in Section 18.1: Bundle encoding on page 137.

The behavior of operations is specified using the notational language defined in *Chapter 17*: Specification notation on page 119 through Section 17.3: Statements on page 125. The descriptions clearly identify where architectural state is updated and the latency of the operands.

A simple model of memory and control registers defined in Section 17.5.2: Memory model on page 130 and Section 17.5.3: Control register model on page 134 is used when specifying load and store operations.

14/331 7645929

a. Only one of the debugging support chapters is applicable depending upon the version of the core implemented. Please refer to the product datasheet for specific variant details.

ST231 Execution units

#### 2 Execution units

The functional core of ST231 comprises of a number of execution units working on two register files. The execution units include 4 integer units, 2 multiply units, a load/store unit and a branch unit which are all described in this chapter. The two register files, the branch registers and the general purpose registers are described in *Chapter 3: Architectural state on page 19*.

## 2.1 Integer units (IU)

The ST231 has four identical integer units. Each integer unit is capable of executing one operation per cycle. The results of the integer units can be used as operands of the next bundle. This is equivalent to a pipeline depth of one cycle.

Each operation can take up to three operands in the form of two 32-bit values and a single conditional bit. The IU then executes the appropriate operation and produces up to two results in the form of a 32-bit value and a 1-bit conditional value. The integer operations supported are detailed in the *Chapter 18: Instruction set on page 137*.

## 2.2 Multiply units

The ST231 has two identical multiply units. Each multiply unit is pipelined with a depth of three cycles, executing an operation every cycle.

Each multiply units takes two 32-bit operands and produces a single 32-bit result. The multiply operations supported are detailed in the *Chapter 18: Instruction set on page 137*.

# 2.3 Load/store unit (LSU)

The ST231 has a single load/store unit. The load/store unit is pipelined with a depth of three cycles, executing an operation every cycle.

The load store can take up to three 32-bit operands and may produce a single 32-bit result depending on the operation. The load store operations supported are detailed in the *Chapter 18: Instruction set on page 137*.

Memory access protection and translation is implemented by the TLB, this is part of the memory sub-system. The TLB also controls the cache behavior of data accesses, *Chapter 6: Memory translation and protection on page 31.*

Uncached accesses or accesses which miss the data cache cause the load/store unit to stall the pipeline to ensure correct operation.

15/331

Execution units ST231

#### 2.3.1 Memory access

The ST231 uses a single 32-bit address space to address the external memory system. Peripheral devices and control registers are also mapped into the address space.

All cacheable memory transactions are made using the data cache. The data cache determines if an external memory access (using the STBus) is required to complete the request.

Note:

Cacheable **STORE** memory transactions that miss are written to the write buffer not the data cache.

Uncached accesses are performed directly on the memory system, see to *Section 7.3.5: Uncached load and stores on page 53*.

#### 2.3.2 Addressing modes

The ST231 supports one addressing mode – the effective address is an immediate (constant) plus a register.

## 2.3.3 Alignment

All **LOAD** and **STORE** instructions work on data stored on the natural alignment of the data type; that is, words on word boundaries, half-word on half word boundaries.

**LOAD** and **STORE** operations with misaligned addresses raise an exception which makes possible the implementation of misaligned **LOAD**s by trap handlers.

For a byte or half-word **LOAD**, the data from memory is loaded into the least significant part of a register and is either sign-extended or zero extended according to the instruction definition.

For a byte or half-word **STORE**, the data stored from the least significant part of a register.

#### 2.3.4 Control registers

The LSU maps a part of the address space that is devoted to control registers (see *Chapter 9: Control registers on page 67* for details). The LSU control register block intercepts **LOAD**s and **STORE**s to this area of memory so that it can process the operation. No access to the data cache is made for control register operations. Transactions are made across the 32-bit control register bus to those control registers that live outside the LSU.

#### 2.3.5 Cache purging

Cache purging (flush and invalidate) operations are provided on the ST231.

They allow for purging lines and sets from the data cache, and invalidating the entire instruction cache.

#### 2.3.6 Dismissible loads

Dismissible **LOAD**s are used to support software load speculation. This allows the compiler to schedule a **LOAD** in advance of a condition that predicates its use.

Dismissible **LOAD**s are required to return the same value as a normal **LOAD** if such an operation can be executed without causing an exception. Otherwise dismissible **LOAD**s return zero.

ST231 Execution units

In the event that misaligned accesses are supported through a software trap handler, the ST231 may be configured to trap non-aligned dismissible LOADs, see the *Chapter 5: Traps* (exceptions and interrupts) on page 25. The TLB can be configured to return zero for dismissible LOADs in cases where they can be executed without exception; this is to support peripherals which have destructive read behavior.

#### 2.4 Branch unit

The ST231 has one branch unit. This unit supports both relative immediate branches (with and without condition code) and absolute and relative jumps and calls.

A conditional branch is performed using the **BR** and **BRF** instructions. These instructions have two operands, a condition code register and the immediate offset of the branch.

An unconditional branch is performed using the **GOTO** (immediate) instruction. This instruction has one operand containing the immediate offset of the branch.

An unconditional jump is performed using the **GOTO** (link register) instruction. This instruction causes a control transfer to the address stored in the link register, see *Section 3.2.1: Link register on page 19*.

An unconditional call is performed using the **CALL** (link register) and **CALL** (immediate) instructions. These instruction cause a control transfer to the address stored in the link register (see *Section 3.2.1: Link register on page 19*) or to the specified immediate offset. After the call, the link register contains the return address.

Due to pipeline restrictions all branches and jumps incur a penalty of one cycle of stall.

#### 2.4.1 Idle mode macro

The **IDLE mode** macro is encoded as a bundle containing a **GOTO** (immediate) to the same bundle. The **IDLE mode** macro must be alone in a bundle (otherwise it is treated as a normal **GOTO**).

The **IDLE mode** macro is architecturally identical to the branch it is derived from. When an interrupt or debug interrupt occurs the core exits idle mode and jumps to the correct handler.

#### Implementation notes

When an IDLE mode macro is executed the ST231:

- empties the pipeline, completing any instructions issued before the idle,

- waits for all outstanding bus transactions to complete:

- all prefetches issued to the bus have completed (responses have come back)

- all writes issued to the bus have completed (responses have come back)

- waits for the SDI output buffer to be become empty

- enters idle mode

The core will not enter idle mode while the performance monitoring hardware is enabled. When the core enters idle mode a bit is set in the PM\_CR register, see *Section 15.3: Control register (PM CR) on page 114.*

Execution units ST231

The core discontinues entry to idle mode and jumps to the correct handler on the following conditions:

- STBus error exception

- external interrupt

- debug interrupt

The core exits idle mode and jumps to the correct handler on the following conditions:

- external interrupt

- debug interrupt

While in idle mode:

- timers continue to operate normally

- the SDI input ports do not accept data

- the SDI output ports do not send out data as they must be empty before the core enters idle mode

- the peripheral blocks accepts and responds to STBus transactions as normal

- the DSU continues to operate as normal (both using the TAPLink and using the STBus)

## 2.4.2 syncins macro

The **syncins** macro can be used to ensure that all previous instructions have completed and all new instructions have not yet started. The **syncins** macro ensures that the pipeline is empty and the instruction buffer is purged.

The **syncins** macro may only be executed in supervisor mode.

ST231 Architectural state

## 3 Architectural state

This chapter describes the architectural state of the ST231 core, which consists of the following elements:

- program counter

- register file

- branch register file

- program status word

- control registers

# 3.1 Program counter (PC)

The PC contains a 32-bit byte address pointing to the beginning of the current bundle in memory. The two LSBs of the PC are always zero.

## 3.2 Register file

The general purpose register file contains 64 words of 32 bits each. These are named R0 to R63.

Reading register zero (R0) always returns the value zero. Writing values to R0 has no effect on the processor state.

### 3.2.1 Link register

Register R63, the architectural link register, is used by the **call** and **return** mechanism. R63 is updated by explicit register writes and the **call** operation. Some restrictions apply to accessing the link register, see *Section 4.5.2: Restrictions on link register on page 24*.

# 3.3 Branch register file

The branch register file contains eight single bit branch registers, B0 to B7.

# 3.4 Program status word (PSW)

The program status word (PSW) contains control information that affects the operation of the ST231 processor.

Architectural state ST231

## 3.4.1 Bit fields

The PSW contains the bit fields listed in *Table 1*.

Table 1. PSW bit fields

| Name                   | Bit(s)  | Writable | Reset | Comment                                                                                                                                       |

|------------------------|---------|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| USER_MODE              | 0       | RW       | 0x0   | 0: the core is in supervisor mode 1: the core is in user mode                                                                                 |

| INT_ENABLE             | 1       | RW       | 0x0   | 0: external interrupts are disabled     1: external interrupts are enabled                                                                    |

| TLB_ENABLE             | 2       | RW       | 0x0   | address translation is disabled     address translation is enabled                                                                            |

| TLB_DYNAMIC            | 3       | RW       | 0x0   | 0: speculative loads and purge address ignore "no mapping" violations.  1: speculative loads and purge address cause "no mapping" violations. |

| SPECLOAD_MALIGNTRAP_EN | 4       | RW       | 0x0   | 0: disables exceptions on speculative load misalignment errors.     1: enables exceptions on speculative load misalignment errors.            |

| Reserved               | 5       | RO       | 0x0   | Reserved                                                                                                                                      |

| Reserved               | 6       | RO       | 0x0   | Reserved                                                                                                                                      |

| Reserved               | 7       | RO       | 0x0   | Reserved                                                                                                                                      |

| DBREAK_ENABLE          | 8       | RW       | 0x0   | 0: data breakpoints are disabled 1: data breakpoints are enabled                                                                              |

| IBREAK_ENABLE          | 9       | RW       | 0x0   | O: instruction breakpoints are disabled     1: instruction breakpoints are enabled                                                            |

| Reserved               | 10      | RO       | 0x0   | Reserved                                                                                                                                      |

| Reserved               | 11      | RO       | 0x0   | Reserved                                                                                                                                      |

| DEBUG_MODE             | 12      | RW       | 0x0   | 0: the core is not in debug mode 1: the core is in debug mode                                                                                 |

| Reserved               | [31:13] | RO       | 0x0   | Reserved                                                                                                                                      |

ST231 Architectural state

#### 3.4.2 USER MODE

The USER\_MODE bit indicates whether the machine is in user mode or supervisor mode. When in user mode, the processor has restricted access:

- the TLB (see *Chapter 6: Memory translation and protection on page 31*) defines the level of access to memory in both user and supervisor modes

- in user mode there is limited access to control registers, see Chapter 9: Control registers on page 67

- certain instructions can not be executed in user mode, see Chapter 18: Instruction set on page 137

## 3.4.3 DEBUG\_MODE

The DEBUG\_MODE bit indicates whether the machine is in debug mode. For the effect of writing to DEBUG\_MODE, see *Exiting debug mode on page 88*.

#### 3.4.4 PSW access

The PSW can be read as a control register, Section 3.5: Control registers on page 21.

The **pswset** instruction is used to set any number of bits in the PSW atomically. The **pswclr** instruction is used to clear any number of bits in the PSW atomically.

The PSW can also be updated by means of an **rfi** operation. The required status word should be stored into the SAVED\_PSW and the address of the code to be executed directly after the change should be stored in the SAVED\_PC. Then executing an **rfi** atomically copies the SAVED\_PSW into the PSW and the SAVED\_PC into the PC.

**Example:** Procedure to write the PSW, (in ST231 assembler code),

```

_sys_set_psw

stw SAVED_PC[$r0] = $r63;; // Return address

stw SAVED_PSW[$r0] = $r4;; // New value

nop ;;

nop ;;

nop ;;

rfi ;;

```

Note:

Interrupts must be disabled during this sequence to prevent SAVED\_PC and SAVED\_PSW from being changed.

# 3.5 Control registers

Additional architectural state is held in a number of memory mapped control registers, Chapter 9: Control registers on page 67. These registers include support for interrupts and exceptions, and memory protection.

## 4 Execution pipeline and latencies

This chapter describes the architecturally visible pipeline and operation latencies for the ST231.

## 4.1 Execution pipeline

The ST231 uses a pipelined execution scheme. This pipeline is architecturally visible in a number of areas:

- operation latencies

- branch stalls

- bypassing

- usage restrictions

The execution pipeline is three cycles long and comprises three stages E1, E2 and E3. All operations begin in E1. Operands are read or bypassed to an operation at the start of E1. All results are written at the end of E3.

This execution pipeline allows arithmetic and **load/store** operations to execute for up to three cycles. The results of operations which complete earlier than E3 are made available for bypassing as operands to subsequent operations, though strictly operations do not complete until the end of the E3 stage. This is when the architectural state is updated.

The pipeline is designed to efficiently implement the serial execution of the code, see *Chapter 16: Execution model on page 116*.

## 4.2 Operation latencies

ST231 operations begin in E1 cycle and complete in either E1, E2 or E3. The time taken for an operation to produce a result is called the operation latency. For simple operations like **add** and **subtract** the latency is a single cycle. For operations like **multiply** and **load** the latency is three cycles.

Note: Operational latencies may vary between different members of the ST200 processor family.

#### 4.3 Branch stalls

The ST231 has no penalty for not taken branches.

The ST231 stalls for one cycle when a branch is taken. There may be a further stall caused by the destination bundle of a branch crossing an I-cache line boundary. See *Section 7.2.1: Instruction buffer on page 49*.

#### 4.4 Interlocks

The ST231 provides operation latency interlock checking. This enforces the latency between all operations by stalling the pipeline, with the following exceptions:

- store to SAVED PSW to rfi

- store to SAVED PC to rfi

- store to SAVED\_SAVED\_PSW to rfi

- store to SAVED SAVED PC to rfi

In the cases listed above, the software must ensure that the control register has been updated before executing the **rfi**. See *Section 3.4.4: PSW access on page 21* for further details of how to do this.

For all other cases, the ST231 automatically stalls the pipeline to uphold the internal latency constraints. As such there are no possible latency violations for the above cases.

For optimal machine usage, bundles containing useful operations should be inserted in order to respect the underlying latency between operations.

#### 4.5 Additional notes

Additional information about flushing the pipeline and restrictions on the link register are provided in this section.

#### 4.5.1 Flushing the pipeline

As state is stored within the pipeline, some changes require that state to be flushed out to ensure coherency. For example, the ST231 pipeline needs to be flushed to ensure that UTLB updates take effect. (For the recommended sequence for UTLB updates, see *Coherency on page 40*).

The following instructions cause the pipeline to be emptied:

- rfi

- pswset

- pswclr

- prgins

- prginspg

#### 4.5.2 Restrictions on link register

To optimize performance, the ST231 contains a speculative link register (SLR). This is a copy of possible future updates to R63. In the current implementation, this register is updated earlier in the pipeline than R63. The core uses SLR as the source for register indirect branch operations.

There are circumstances when SLR is not a true copy of R63. This occurs when an interrupt or exception is taken immediately before an update to R63 but after the SLR has been speculatively changed. The solution to this is to ensure that all interrupt and exception handlers write explicitly to R63 prior to the execution of an **rfi**, **call \$r63** or **goto \$r63**. This requirement can easily be met with a **mov** operation from R63 to R63 in one of the first bundles of the trap handler.

Register indirect **call** and **goto** operations also require R63 to be stable. If R63 is modified in the three bundles preceding one of these operations, an interlock stall occurs.

A number of operations cannot target R63 for efficiency reasons. These include **multiply** operations, byte and half-word **load** operations, see *Chapter 18: Instruction set on page 137*.

# 5 Traps (exceptions and interrupts)

In the ST231 architecture, exceptions and interrupts are jointly termed traps. This chapter describes the trap mechanism.

## 5.1 Trap mechanism

The ST231 defines two types of traps:

- external asynchronous traps (interrupts and bus errors),

- internal synchronous traps (exceptions resulting from operation execution).

A trap point is the point in the program execution where a trap occurs. All bundles executed before the trap point have finished updating the architectural state; no architectural state has been updated by subsequent bundles. For an exception, the trap point is the (start of the) bundle which caused the exception. For an interrupt, the trap point is (the start of) the bundle whose execution has been interrupted. Typically this is a bundle that had been executed shortly after the interrupt was raised or enabled.

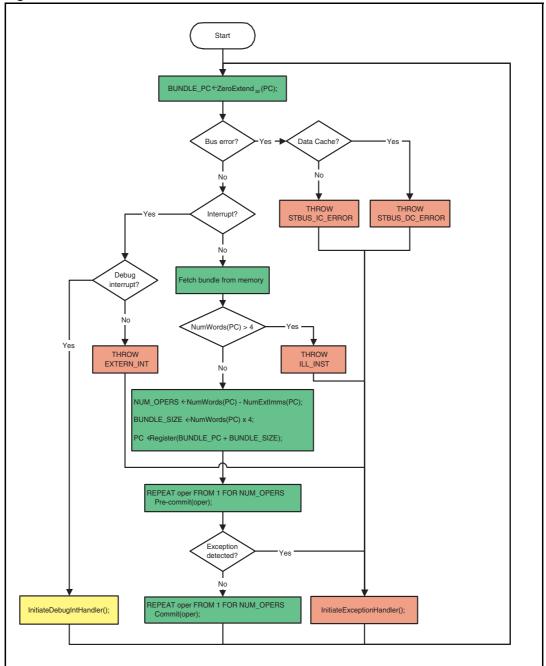

The flow diagram, *Figure 16 on page 101* defines when a trap is taken. The aim of this chapter is to define the steps that are carried out when a trap is to be taken.

In effect, taking a trap can be viewed as executing an operation that branches to the required handler, with a number of side effects. The side effects are defined by the statements below. An external interrupt is treated as an EXTERN\_INT exception, with only debug interrupts being handled differently.

At the trap point, the ST231 transfers execution to the trap handler, starting at the address held in the HANDLER\_PC control register, and saves the execution state as detailed in *Section 5.3: Saved execution state*. All operations issued before the trapping bundle are allowed to complete. All operations issued after and including the trapping bundle are discarded. The architectural state, with the exception of saved execution state, is exactly that at the trap point. Hence ST231 interrupts and exceptions can be considered precise.

Traps are handled strictly (in order), and indivisibly with respect to the bundle stream.

# 5.2 Exception handling

Due to the fact that more than one operation can execute at the same time, it is possible to have more than one exception thrown in a bundle. In this case, only the highest priority exception is passed to the handler.

#### 5.3 Saved execution state

Directly following a trap the saved execution state defines the reason for the trap and the precise trap point in the execution flow of the processor. Control registers store these values for use by the handler routine.

Taking an exception can be summarized as:

```

NEXT_PC \leftarrow HANDLER_PC; // Branch to the exception handler EXCAUSE \leftarrow HighestPriority(); // Store information EXADDRESS \leftarrow ExceptAddress(EXCAUSE);// for the handler SAVED_PSW \leftarrow PSW; // Save the PSW and PC SAVED_PC \leftarrow BUNDLE_PC; PSW[USER_MODE] \leftarrow 0; // Enter supervisor mode PSW[INT_ENABLE] \leftarrow 0; // Disable interrupts PSW[IBREAK_ENABLE] \leftarrow 0; // Disable instruction breakpoints PSW[DBREAK_ENABLE] \leftarrow 0; // Disable data breakpoints

```

Where the function <code>HighestPriority</code> returns the highest priority exception from those that have been thrown, refer to <code>Section 5.6</code>. The <code>ExceptAddress</code> function defines the value that is stored into the <code>EXADDRESS</code> control register. Its return value is either 0 or the address of the data or instruction which has triggered the exception.

#### Therefore:

```

variable ← ExceptAddress(exception);

is equivalent to:

IF ((exception = DBREAK) OR

(exception = MISALIGNED_TRAP) OR

(exception = CREG_NO_MAPPING) OR

(exception = CREG_ACCESS_VIOLATION) OR

(exception = DTLB) OR

(exception = ITLB)) THEN

variable ← value;

ELSE

variable ← 0;

```

Where value is the optional argument that is passed to THROW (see *Section 17.3.5: Exceptions on page 127*) when the exception was generated.

26/331 7645929

The core uses a **rfi** (return from interrupt) operation to recommence execution at the trap point. An **rfi** operation causes the following state updates:

## 5.4 Interrupts

All interrupts are effectively treated by the ST231 as an exception of type EXTERN\_INT. Individual interrupt lines are indicated by registers in the interrupt controller. See *Chapter 12: Interrupt controller on page 80*.

# 5.5 Debug interrupt handling

Refer to Chapter 13: Debugging support (TAPLink) on page 87.

## 5.6 Exception types and priorities

The EXCAUSENO control register gives the cause of the last exception. Since only one exception is thrown at a time, simultaneous exceptions are prioritized. The bit fields for this register are listed in *Table 2*.

Table 2. EXCAUSENO bit fields

| Name      | Bit(s) | Writable | Reset | Comment                         |

|-----------|--------|----------|-------|---------------------------------|

| EXCAUSENO | [4:0]  | RW       | 0x0   | Specifies the exception number. |

| Reserved  | [31:5] | RO       | 0x0   | Reserved.                       |

For backward compatibility, the exception cause is also available as a bit-field by reading the EXCAUSE register. The EXCAUSE register is read only and always returns 1 << EXCAUSENO\_EXCAUSENO.

*Table 3* shows the possible exceptions and the value in the EXCAUSENO bitfield of the EXCAUSENO control register that each corresponds to. The table is listed in exception priority order starting with the highest priority.

Table 3. EXCAUSENO\_EXCAUSENO values

| Name                  | Value | Comment                                                                                                                   |

|-----------------------|-------|---------------------------------------------------------------------------------------------------------------------------|

| STBUS_IC_ERROR        | 0     | The instruction cache caused a bus error.                                                                                 |

| STBUS_DC_ERROR        | 1     | The data cache caused a bus error.                                                                                        |

| EXTERN_INT            | 2     | There was an external interrupt.                                                                                          |

| IBREAK                | 3     | An instruction address breakpoint has occurred.                                                                           |

| ITLB                  | 4     | An instruction related TLB exception has occurred.                                                                        |

| SBREAK                | 5     | A software breakpoint was found.                                                                                          |

| ILL_INST              | 6     | The bundle could not be decoded into legal sequence of operations or a privileged operation is being issued in user mode. |

| SYSCALL               | 7     | System call.                                                                                                              |

| DBREAK                | 8     | A breakpoint on a data address has been triggered.                                                                        |

| MISALIGNED_TRAP       | 9     | The address is misaligned and misaligned accesses are not supported.                                                      |

| CREG_NO_MAPPING       | 10    | The load or store address was in control register space, but no control register exists at that exact address.            |

| CREG_ACCESS_VIOLATION | 11    | A store to a control register was attempted whilst in user mode.                                                          |

| DTLB                  | 12    | A data related TLB exception has occurred.                                                                                |

| RESERVED              | 13    | Reserved                                                                                                                  |

| SDI_TIMEOUT           | 14    | One of the SDI interfaces timed out while being accessed.                                                                 |

#### 5.6.1 Illegal instruction definition

An illegal instruction exception is caused when an illegal bundle is executed. A legal bundle and all syllables contained in it must conform to the restrictions as detailed in *Chapter 18: Instruction set on page 137.*

In particular, a legal bundle and all the syllables it contains must conform to the following.

- All syllables must be valid operations or an immediate extension.

- A bundle must have a stop bit that is, four zero stop bits are illegal.

- Unused opcode fields must be set to zero, including bit 30.

- Any branch, call, rfi, pswset and pswclr operation must appear as the first syllable of a bundle.

- Multiply operations must appear at odd word addresses.

- Immediate extensions must appear at even word addresses.

- Immediate extensions must associate with an operation that is in the same bundle and has an immediate format that can be extended.

- There may be no more than one immediate extension associated with a single operation.

- A privileged operation can only be executed in supervisor mode. This includes rfi, pswset, pswclr, prginspg and prgins.

- There can only be one operation requiring the load/store unit in each bundle. This includes sync, prgset, prgadd, prginspg, pswset, pswclr, rfi, ldb, ldh, ldw, stb, sth and stw.

- The **sbrk** operation must have the stop bit set.

- Destination registers in a bundle have to be unique, with the exception of R0.

- Idb, Idh and mul operations must not have R63 as a destination register.

- prgins and syscall must be alone in a bundle.

## 5.7 Speculative load considerations

Speculative (or dismissible) loads execute as normal loads except in the following cases.

- The address is in a region where a speculative load may be destructive. In this case, the SCU (see Section 6.6: Speculative control unit (SCU) on page 46) should be set up to prevent speculation to this region. In this case, a zero is always returned and no access is made to the memory.

- A normal load would cause an exception. Generally, in this case, the load is

considered to have been incorrectly speculated and the data is not utilized in the

correct execution of the program. Zero is returned by default.

- If a dismissible **load** causes a bus error then a bus error exception is always thrown. The TLB and/or SCU should always be set up to prevent dismissible loads from causing bus errors. See *Chapter 6: Memory translation and protection on page 31*.

## 5.7.1 Misaligned implementation

Application or system software may require misalignment support, with misaligned accesses being correctly interpreted by the exception handler. To improve speculative load support for misaligned addresses, a control value PSW[SPECLOAD\_MALIGNTRAP\_EN] can be set which causes speculative loads to trap on misaligned addresses rather than returning zero, see *Section 3.4: Program status word (PSW) on page 19*.

# 6 Memory translation and protection

The ST231 provides full memory translation and protection by means of a translation lookaside buffer (TLB).

The TLB enables the ST231 to run memory-managing operating systems (such as Linux). It also provides a level of backward compatibility for the instruction protection unit (IPU) and data protection unit (DPU) functions when running a non-memory managed OS (for example, OS21).

The ST231 memory management system allows multiple virtual address spaces. Each virtual address space has associated with it an address space identifier (ASID).

The ST231 memory management system allows memory pages to be marked with three different policies: cached, uncached and write combining uncached, as defined in *Table 9*.

#### 6.1 TLB overview

The ST231 has a small instruction TLB (ITLB), a small data TLB (DTLB) and a larger unified TLB (UTLB).

The ITLB performs instruction address translations and acts as a cache for address translations stored in the UTLB. When the ITLB misses it automatically updates from the UTLB.

The DTLB performs data address translations and acts as a cache for address translations stored in the UTLB. When the DTLB misses it automatically updates from the UTLB.

When the UTLB is changed, the ITLB and DTLB are not updated. The ITLB and DTLB can be flushed under software control by means of the TLB\_CONTROL register, see Section 6.4.8: TLB\_CONTROL on page 40.

The ITLB and DTLB act as small caches that keep copies of the currently active translations. Only translations that are shared or match the current ASID are loaded into the ITLB and DTLB.

Table 4 provides details of the TLB configuration of the ST231.

Table 4. TLB information

| Item | Size       | Comment                                                    |

|------|------------|------------------------------------------------------------|

| DTLB | 8 entries  | Fully associative buffer with LRU replacement.             |

| ITLB | 4 entries  | Fully associative buffer with LRU replacement.             |

| UTLB | 64 entries | Fully associative buffer which is managed by the software. |

The UTLB size can be determined either by reading the core version register (using a lookup table) or reading the TLB\_REPLACE register after reset.

## 6.2 Address space

This section deals with physical and virtual addresses.

### 6.2.1 Physical addresses

The ST231 TLB supports 32-bit addresses providing up to 4 Gbyte of physical address space. The layout of the TLB registers allows future variants to support up to 45 bits of physical address space.

#### 6.2.2 Virtual addresses

Virtual addresses are 32-bits. The TLB performs the mapping from virtual to physical addresses using one of the following page sizes: 8 Kbyte, 4 Mbyte and 256 Mbyte.

Control registers are accessed by virtual addresses only; virtual addresses corresponding to control registers are not translated. The (virtual) addresses of the control registers are valid physical addresses; any access to these physical addresses will be made to the memory subsystem in the usual way. If the TLB is disabled then the untranslated address will access control registers.

#### 6.3 **Caches**

The caches are virtually indexed and physically tagged. The cache tag RAM lookup occurs in parallel with the TLB lookup.

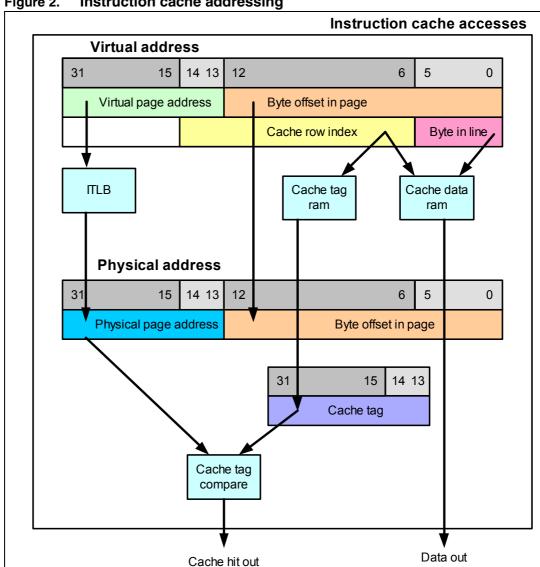

#### 6.3.1 Instruction cache organization

Instruction cache addressing is illustrated in *Figure 2*.

The instruction cache is 32 Kbytes direct mapped and built from 512 x 64 byte lines.

The virtual address bits [14:06] are used to index the instruction cache RAMs.

Virtual address bits [31:13] are sent to the ITLB for translation. The translated physical address bits [31:13] from the ITLB is then compared against the instruction cache tag.

Virtual address bits [05:00] are used to select the correct bytes from the cache line.

Instruction cache addressing Figure 2.

#### 6.3.2 Data cache organization

Instruction cache addressing is illustrated in Figure 3.

The data cache is 32 Kbytes four way set associate and built from 4 x 256 x 32 byte lines.

The virtual address bits [12:05] are used to index the data cache RAMs.

Virtual address bits [31:13] are sent to the DTLB for translation. The translated physical address bits [31:13] from the DTLB are then compared against the data cache tag.

Virtual address bits [04:00] are used to select the correct bytes from the cache line.

Figure 3. Data cache addressing Data cache accesses Virtual address 15 14 13 31 12 4 0 5 Virtual page address Byte offset in page Cache row index Byte in line **DTLB** Cache data Cache tag rams rams **Physical address** 12 31 15 14 13 5 4 0 Physical page address Byte offset in page 31 15 14 13 Cache tag 4 x Cache tag Data Mux compare Way select Cache hit out Data out

# 6.4 Control registers

A full list of control registers is provided in Chapter 9: Control registers on page 67.

#### 6.4.1 PSW

The TLB can be enabled and disabled by a bit in the PSW, see *Chapter 3: Architectural state on page 19*.

While address translation is disabled (TLB\_ENABLE = 0):

- virtual addresses are not translated and are used directly as the physical address

- all data accesses are made uncached

- no TLB exceptions are thrown

#### 6.4.2 TLB\_INDEX

Table 5 shows the mapping for the TLB\_INDEX register.

Table 5. TLB\_INDEX bit fields

| Name     | Bit(s) | Writable | Reset | Comment                                                                                                                                                                                                        |

|----------|--------|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ENTRY    | [7:0]  | RW       | 0x0   | Determines which of the 64 TLB entries is mapped to the TLB_ENTRYx registers. Writing a value to this register that is greater than the maximum UTLB entry available has no effect (the entry is not updated). |

| RESERVED | [31:8] | RO       | 0x0   | Reserved.                                                                                                                                                                                                      |

When the TLB\_INDEX register is written, subsequent read/writes to the TLB\_ENTRYX registers are to the indicated UTLB entry.

### 6.4.3 TLB\_ENTRY0

This register maps bits [31:00] of the TLB entry. The entry is chosen by writing to the TLB\_INDEX register. *Table 6* lists the fields of the TLB\_ENTRY0 register; the fields are described in subsequent tables.

Table 6. TLB\_ENTRY0 bit fields

| Name       | Bit(s)  | Writable | Reset | Comment                                                                          |

|------------|---------|----------|-------|----------------------------------------------------------------------------------|

| ASID       | [7:0]   | RW       | 0x0   | Indicates which address space this page belongs to.                              |

| SHARED     | 8       | RW       | 0x0   | Page shared by multiple address spaces (ASIDs).                                  |

| PROT_SUPER | [11:9]  | RW       | 0x0   | A three bit field that defines the protection of this region in supervisor mode. |

| PROT_USER  | [14:12] | RW       | 0x0   | A three bit field that defines the protection of this region in user mode.       |

Table 6. TLB\_ENTRY0 bit fields (continued)

| Name      | Bit(s)  | Writable | Reset | Comment                                                                                                                                                                                                                         |

|-----------|---------|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIRTY     | 15      | RW       | 0x0   | Page is dirty. When this bit is 0 write accesses to this page (when write permission is allowed) cause a TLB_WRITE_TO_CLEAN exception. When this bit is 1 writes to this page (when write permission is allowed) are permitted. |

| POLICY    | [19:16] | RW       | 0x0   | Cache policy for this page.                                                                                                                                                                                                     |

| SIZE      | [22:20] | RW       | 0x0   | Size of this page (also used to disable the page).                                                                                                                                                                              |

| PARTITION | [24:23] | RW       | 0x0   | Data cache partition indicator.                                                                                                                                                                                                 |

| RESERVED  | [31:25] | RO       | 0x0   | Reserved.                                                                                                                                                                                                                       |

Writing zero to this register disables the page.

*Table 7* lists the possible values of the POLICY field.

Table 7. TLB\_ENTRY0\_POLICY values

| Name       | Value | Comment                                                                                                                                                                             |

|------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UNCACHED   | 0     | Uncached mode. Reads and write that miss the cache are uncached.                                                                                                                    |

| CACHED     | 1     | Cached mode. Reads that miss the cache cause the cache to be filled. Writes that hit the cache are written into the cache. Writes that miss the cache are sent to the write buffer. |

| WCUNCACHED | 2     | Write combining uncached. Writes that miss the cache are sent to the write buffer. Reads that miss the cache are uncached.                                                          |

| Reserved   | 3     | Reserved (on the ST230 reserved cache policies default to uncached).                                                                                                                |

| Reserved   | 4     | Reserved (on the ST230 reserved cache policies default to uncached).                                                                                                                |

| Reserved   | 5     | Reserved (on the ST230 reserved cache policies default to uncached).                                                                                                                |

| Reserved   | 6     | Reserved (on the ST230 reserved cache policies default to uncached).                                                                                                                |

| Reserved   | 7     | Reserved (on the ST230 reserved cache policies default to uncached).                                                                                                                |

Table 8 lists of the possible values of the SIZE field.

Table 8. TLB\_ENTRY0\_SIZE values

| Name     | Value | Comment                                                       |  |

|----------|-------|---------------------------------------------------------------|--|

| DISABLED | 0     | Page is disabled.                                             |  |

| 8K       | 1     | 8 KByte page.                                                 |  |

| 4MB      | 2     | 4 MByte page.                                                 |  |

| 256MB    | 3     | 256 MByte page.                                               |  |

| Reserved | 4     | Reserved (on the ST230 reserved page sizes disable the page). |  |

| Reserved | 5     | Reserved (on the ST230 reserved page sizes disable the page). |  |

| Reserved | 6     | Reserved (on the ST230 reserved page sizes disable the page). |  |

| Reserved | 7     | Reserved (on the ST230 reserved page sizes disable the page). |  |

*Table 9* lists of the possible values of the PARTITION field:

Table 9. TLB\_ENTRY0\_PARTITION values

| Name    | Value | Comment                                                                          |

|---------|-------|----------------------------------------------------------------------------------|

| REPLACE | 0     | Place in the way specified by the replacement counter and increment the counter. |

| WAY1    | 1     | Place in the way 1 only.                                                         |

| WAY2    | 2     | Place in the way 2 only.                                                         |

| WAY3    | 3     | Place in the way 3 only.                                                         |

*Table 10* lists of the possible values of the PROT\_USER and PROT\_SUPER fields:

Table 10. TLB\_PROT values

| Name    | Value | Comment                               |

|---------|-------|---------------------------------------|

| EXECUTE | 1     | Execute permission.                   |

| READ    | 2     | Read (prefetch and purge) permission. |

| WRITE   | 4     | Write permission.                     |

## 6.4.4 TLB\_ENTRY1

This register allows access to bits [63:32] of the TLB entry. The entry is chosen by writing to the TLB\_INDEX register. The fields in this register are listed in *Table 11*.

Table 11. TLB\_ENTRY1 bit fields

| Name     | Bit(s)  | Writable | Reset | Comment                                                                                                                                                                                   |

|----------|---------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VADDR    | [18:0]  | RW       | 0x0   | The upper 19 bits of the virtual address. For 4Mbyte pages only the upper 10 bits of this field are significant. For 256 Mbyte pages only the upper 4 bits of this field are significant. |

| RESERVED | [31:19] | RO       | 0x0   | Reserved.                                                                                                                                                                                 |

### 6.4.5 TLB\_ENTRY2

This register allows access to bits [95:64] of the TLB entry. The entry is chosen by writing to the TLB\_INDEX register. The fields in this register are listed in *Table 12*.

Table 12. TLB ENTRY2 bit fields

| Name     | Bit(s)  | Writable | Reset | Comment                                                                                                                                                                                     |

|----------|---------|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PADDR    | [18:0]  | RW       | 0x0   | The upper 19 bits of the physical address. For 4 Mbyte pages only the upper 10 bits of this field are significant. For 256 Mbyte pages only the upper 4 bits of this field are significant. |

| Reserved | [31:19] | RO       | 0x0   | Reserved.                                                                                                                                                                                   |

#### 6.4.6 TLB\_ENTRY3

This register maps bits [127:96] of the TLB entry. The entry is chosen by writing to the TLB\_INDEX register. The fields in this register are listed in *Table 13*.

Table 13. TLB\_ENTRY3 bit fields

| Name     | Bit(s) | Writable | Reset | Comment   |

|----------|--------|----------|-------|-----------|

| Reserved | [31:0] | RO       | 0x0   | Reserved. |

#### 6.4.7 TLB REPLACE

Table 14 shows the mapping of the TLB\_REPLACE register.

Table 14. TLB\_REPLACE bit fields

| Name     | Bit(s)  | Writable | Reset  | Comment                                                      |

|----------|---------|----------|--------|--------------------------------------------------------------|

| LFSR     | [15:0]  | RW       | 0xFFFF | Random number used to determine which entry to replace next. |

| LIMIT    | [23:16] | RW       | 0x40   | Number of TLB entries that can be replaced.                  |

| Reserved | [31:24] | RO       | 0x00   | Reserved.                                                    |

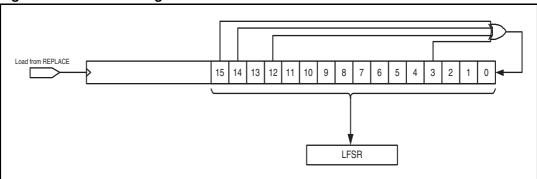

Figure 4 shows the structure of the REPLACE register.

Figure 4. REPLACE register

Software uses the replacement register to randomly decide which TLB entry to replace. The value of the REPLACE field is generated in a pseudo-random manner using a 16-bit linear feedback shift register (LFSR) generating a maximum length sequence (taps on bits 3, 12, 14 and 15).

A read from the TLB\_REPLACE register returns the current LFSR and LIMIT values, the LFSR is then clocked to generate a new value. The current value of the LFSR field can be changed by writing to the TLB\_REPLACE register.

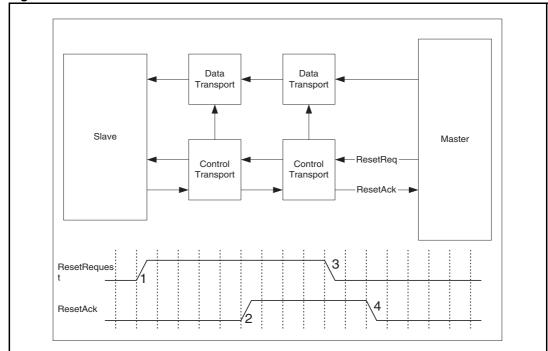

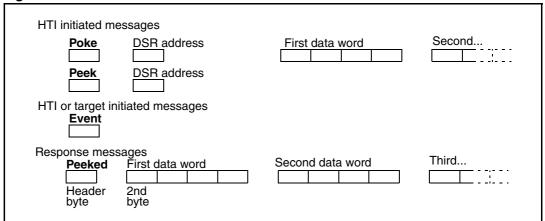

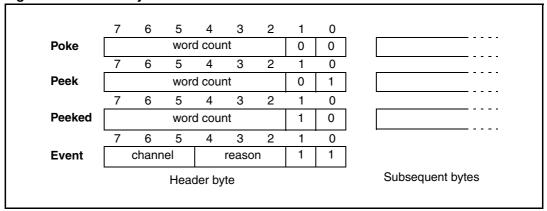

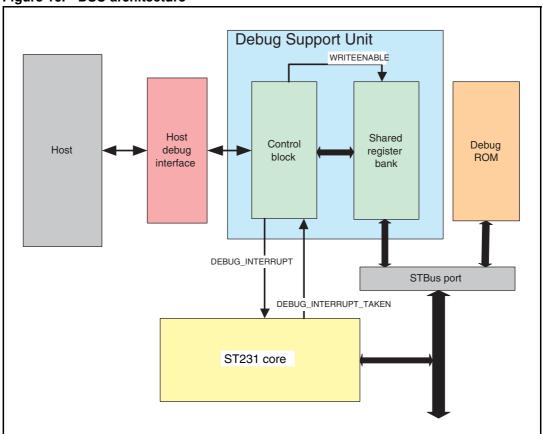

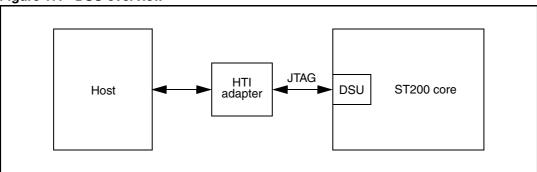

The LIMIT field is reset to the number of entries in the TLB<sup>(a)</sup>. The LIMIT field can be changed by writing the TLB\_REPLACE register. To reserve a number of entries for a fixed mapping, software sets the LIMIT field to less than the number of entries available to the TLB.